高频小功率晶体管设计

模拟技术

描述

① 芯片横向结构参数设计

产品发射区结构设计为梳状结构。晶体管版图中发射区半宽度选择为30μm。充分考虑器件低饱和压降要求和生产经验,非工作基区宽度为20μm。这样单元器件横向宽度为35μm。发射区边缘于基极引线孔边缘为10μm。考虑接触孔尺寸对接触电阻的影响及公司的光刻能力,发射区引线孔距发射区边缘为5μm。

为有效地利用芯片面积,发射极与基极呈梳状设计。发射极宽度为40μm,基极金属电极宽度为25μm,基极与发射极间距为5μm。发射极压焊点尺寸为310×150μm2,基极压焊点尺寸为95×110μm2.设计得到的版图面积为0.41×0.41mm2(如图2(a)~2(d)所示)。与经验数据比较(0.22mm2/W),高频小功率耗散功率为0.5W,所设计的芯片面积较合理。设计得到的高频小功率晶体管的发射区版图面积AE=0.07mm2,LE=2.5mm。

② 芯片纵向结构参数设计

该产品的基底材料选择< 111 >晶向,N+/N型低缺陷外延片。击穿电压主要由N型外延层材料的电阻率及外延层厚度决定,要得到合适的击穿电压就需要选择合适的材料电阻率,若电阻率太高,可能造成产品集电极串联电阻偏大,而导致产品饱和压降大;电阻率太低,在工艺上又很难做到较高的电压。

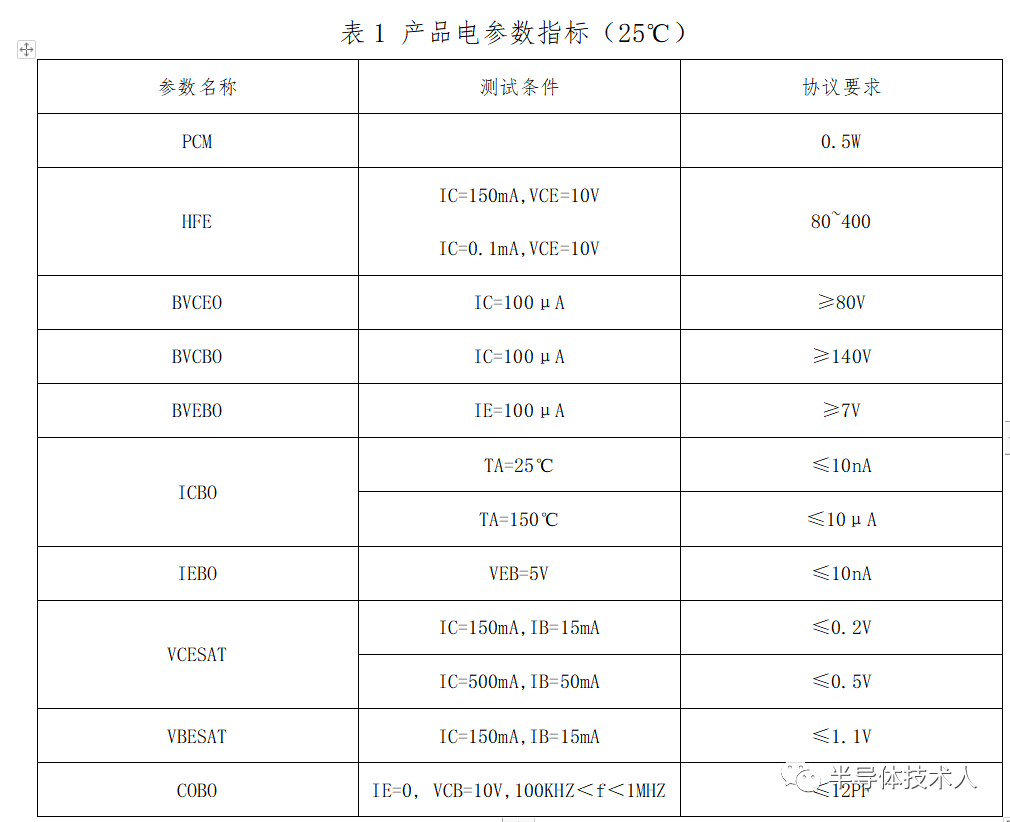

除此之外,在工艺上还需对基区扩散结深及扩散浓度合理地进行控制。根据产品电参数指标要求,在25℃室温情况下,当测试电流IC=100μA时,晶体管集电极-基极击穿电压(BVCBO)需高于140V。为保证器件可靠性,对BVCBO击穿电压指标考虑10%的裕量,即BVCBO设计目标值为154V。图3为仿真得到的器件BVCBO曲线,在仿真过程中,N型外延层电阻率的变化范围为1~5Ω.cm,外延层厚度为8μm,基区次表面浓度1E18cm-3,基区宽度为0.2μm,发射区表面浓度5E19cm-3,发射结结深xjE=0.05μm,集电结结深xjB=0.25μm。由图3可见,当外延层电阻率选择为3Ω.cm时,器件BVCBO达到约160V,满足产品电参数指标要求。另外,当电阻率继续增大时,器件BVCBO击穿特性变“软”,如图4所示。

图5为仿真得到的在上述晶体管结构参数下,当外延层电阻率为3Ω.cm时,集电极-发射极击穿电压(BVCEO)曲线。由图5可见,当N型外延层电阻率为3Ω.cm时,BVCEO高于80V,满足电参数指标要求,表明外延层电阻率的选择较合理。

图6为在上述晶体管结构参数条件下仿真得到的发射极-基极击穿电压(BVEBO)。由图6可见,采用上述晶体管结构参数后,BVEBO达到15V,满足产品电参数指标要求(电参数指标要求BVEBO≥7V)。

晶体管的饱和压降 VCEsat主要由集电区串联电阻决定。集电区串联电阻又是由集电区的电阻率与集电区厚度、面积来决定的。图8为仿真得到的在不同基极电流下,器件饱和压降VCEsat。由图7可见:根据指标要求(VCEsat≤0.5V@IB=50mA,IC=500mA),饱和压降接近指标的上限,因此还需要通过进一步减小基区宽度来实现(或适当增大发射结面积)。

对于基区结构参数的设计,综合考虑了基区掺杂浓度和基区宽度对直流增益、基极电阻自偏压效应、基区穿通效应及特征频率的影响。经过仿真验证,最终确定的基区次表面浓度5×1017cm-3,发射区表面浓度选择要高于基区表面浓度两个数量级),发射区表面浓度选择为5E19cm-3,发射结结深xjE=0.05μm,基区宽度为0.2μm。图8为仿真得到的发生集电极-基极雪崩击穿时,器件内部电场分布曲线。此时基区掺杂浓度和基区宽度设计值满足下限要求。

图9为仿真得到的在上述基区结构参数情况下,不同基极注入水平下晶体管输出IV曲线,由曲线可计算得到不同电流情况下的直流增益。图9为基极注入电流为1mA~9mA情况。由图9可见,从设计角度考虑,仿真所得到的直流增益均满足电参数指标要求。

-

高频晶体管是什么 高频晶体管的特性2023-02-25 3921

-

什么是达林顿晶体管?2023-02-16 2088

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2551

-

常用晶体管的高频与低频型号是什么?2017-10-11 3870

-

高频中、大功率晶体管2013-08-17 3347

-

场效应管是一种什么元件而晶体管是什么元件2012-07-11 6497

-

晶体管的选用经验2012-01-28 3507

-

晶体管分类及参数2010-08-12 3344

-

电力晶体管的原理和特点是什么?2010-03-05 12034

-

高频晶体管,高频晶体管原理是什么2010-03-01 4503

-

高频晶体管的特性与使用技巧2009-10-04 869

全部0条评论

快来发表一下你的评论吧 !