STA分析—时序检查

电子说

描述

Setup和hold时间检查

Setup时间是,为了寄存器可靠的采样到数据,数据必须提前于采样时钟沿稳定的最小时间。Hold时间是,为了寄存器可靠的采样到数据,数据必须在采样时钟沿后稳定的最小时间。

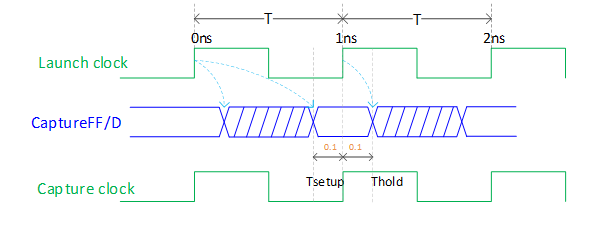

如图一所示,周期T=1ns,该寄存器的setup要求时间是Tsetup=0.1ns,hold要求时间是Thold=0.1ns。setup时间检查机制做这样的检查:上一个Launch时钟沿打出来的数据的data arrival time(数据到达时间)不能晚于T - Tsetup = 0.9ns;而hold时间检查机制做这样的检查:同一个周期的Launch时钟沿打出来的数据的data arrival time(到达时间)不能早于Thold = 0.1ns。

同时满足setup、hold时间要求的意义即是,在时钟采样沿的前后一段最小时间内,数据必须保存稳定,以供寄存器可靠的采样到上一拍发送过来的正确数据。

**图一 ** setup 、 hold****时间检查示意图

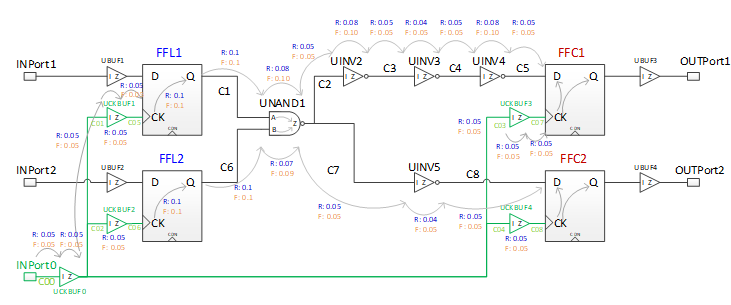

我们把上篇文章的图再贴过来:

图二 逻辑电路图(含BC工作条件下的延迟信息)

下面分析FFC1寄存器的setup、hold检查过程:

上篇文章说过,到FFC1的D端2条逻辑路径和4个path delay,分别是FFL1->FFC1的rise delay、FFL1->FFC1的fall delay、FFL2->FFC1的rise delay、FFL2->FFC1的fall delay。

以时钟源头作为起点的path delay等于data arrival time。 根据图一,可以看出:

0****1

FFL1到FFC1的rise delay的data arrival time

T(FFL1->FFC1-rise)

= T(Launch-clock-tree) + T(data-path-rise)

=T(C00-rise) + T(UCKBUF0-rise) + T(C01-rise) + T(UCKBUF1-rise) + T(C05-rise) + T(FFL1_CK2Q-rise) + T(C1-rise) ~ ~ + D(UNAND1_A2Z-fall) + T(C2-fall) + T(UINV2-rise) + T(C3-rise) + T(UINV3-fall) + T(C4-fall) + T(UINV4-rise) + T(C5-rise)

= (0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.1 + 0.05 + 0.08 + 0.05 + 0.05 + 0.05 + 0.08 + 0.05

= 0.96ns;

02

FFL1到FFC1的fall delay的data arrival time

T(FFL1->FFC1-fall)

= T(Launch-clock-tree) + T(data-path-fall)

=(0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.08 + 0.05 + 0.1 + 0.05 + 0.04 + 0.05 + 0.1 + 0.05

= 0.97ns;

03

FFL2到FFC1的rise delay的data arrival time

T(FFL2->FFC1-rise)

= T(Launch-clock-tree) + T(data-path-rise)

=T(C00-rise) + T(UCKBUF0-rise) + T(C02-rise) + T(UCKBUF2-rise) + T(C06-rise) + T(FFL2_CK2Q-rise) + T(C6-rise) ~ ~ + D(UNAND1_B2Z-fall) + T(C2-fall) + T(UINV2-rise) + T(C3-rise) + T(UINV3-fall) + T(C4-fall) + T(UINV4-rise) + T(C5-rise)

= (0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.09 + 0.05 + 0.08 + 0.05 + 0.05 + 0.05 + 0.08 + 0.05

= 0.95ns;

04

FFL2到FFC1的fall delay的data arrival time

T(FFL2->FFC1-fall)

= T(Launch-clock-tree) + T(data-path-fall)

=(0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.07 + 0.05 + 0.1 + 0.05 + 0.04 + 0.05 + 0.1 + 0.05

= 0.96ns;

05

FFC1的setup requirement时间

T + T(Capture-clock-tree) - T(setup)

= T + T(C00-rise) + T(UCKBUF0-rise) + T(C03-rise) + T(UCKBUF3-rise) + T(C07-rise) - T(setup)

= 1ns + (0.05 + 0.05 + 0.05 + 0.05 + 0.05) – 0.1ns

= 1.15ns

06

FFC1的hold requirement时间

T(Capture-clock-tree) + T(hold)

= T(C00-rise) + T(UCKBUF0-rise) + T(C03-rise) + T(UCKBUF3-rise) + T(C07-rise) - T(setup)

= (0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1ns

= 0.35ns

做setup检查时,STA会遍历计算所有到FFC1/D端路径的data arrival time,然后将每个值与T + T(Capture-clock-tree) - T(setup)做运算。以slack来表示余量,setup time slack = data require time – data arrival time = {T + T(Capture-clock-tree) - T(setup)} – {T(Launch-clock-tree) + T(data-path)}。只有当所有Slack值都为正时,才满足setup时间要求。

类似的,做hold检查时,也是将每个data arrival time的值与T(Capture-clock-tree) + T(hold)做比较,以slack来表示余量,hold time slack = data arrival time - data require time = {T(Launch-clock-tree) + T(data-path)} - {T(Capture-clock-tree) + T(hold)}。只有当所有Slack值都为正时,才满足hold时间要求。

上述4个path delay的Setup time slack分别为:

Setup time slack(1) = 1.15ns – 0.96ns = 0.19ns

Setup time slack (2) = 1.15ns – 0.97ns = 0.18ns

Setup time slack (3) = 1.15ns – 0.95ns = 0.20ns

Setup time slack (4) = 1.15ns – 0.96ns = 0.19ns

4条path delay的hold slack time分别为:

Hold time slack(1) = 0.96ns – 0.35ns = 0.61ns

Hold time slack(2) = 0.97ns – 0.35ns = 0.62ns

Hold time slack(3) = 0.95ns – 0.35ns = 0.60ns

Hold time slack(4) = 0.96ns – 0.35ns = 0.61ns

由于所有slack值都为正,故setup和hold时间检查都满足了。

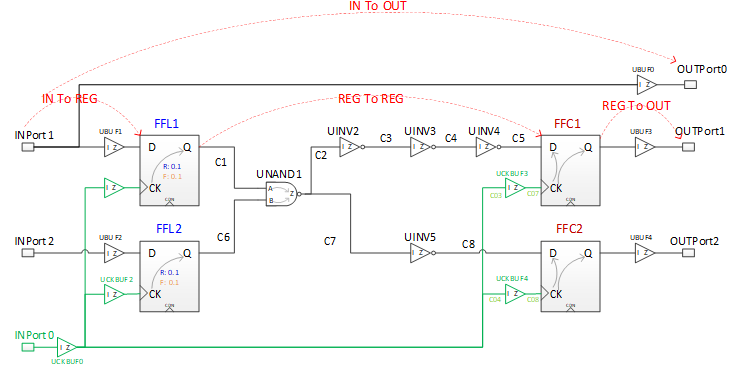

时序路径概念

STA分析时,所有时序路径都有起点和终点,起点包括输入端口和时序单元的时钟端口,终点包括输出端口和时序单元的数据输入端口。所以总共有4种路径集合,即:

a. 从输入端口到输出端口(IN To OUT);

b. 从输入端口到时序单元的数据输入端口(IN To REG);

c. 从时序单元的时钟端口到时序单元的数据输入端口(REG To REG);

d. 从时序单元的时钟端口到输出端口(REG To OUT)。

4种时序路径请见图三:

图三 时序路径

Timing Arc 概念

如图三所示,每个cell都存在多条Timing Arc,如UNAND1存在A->Z和B->Z这2条Timing Arc。FFC1也存在CK->Q和CK->D 2条Timing Arc。

其中UNAND1的A->Z和B->Z是组合路径Timing Arc。FFC1的CK->Q是edge Timing Arc,FFC1的CK->D又含setup arc和hold arc。

-

集成电路设计中静态时序分析介绍2025-02-19 2044

-

STA分析-从一个案例开始2023-07-05 3468

-

静态时序分析的相关概念2023-07-04 2261

-

STA-0.静态时序分析概述2023-06-27 2258

-

FPGA静态时序分析详解2022-09-27 4287

-

VIVADO时序约束及STA基础2022-03-11 11430

-

静态时序分析STA的优点以及缺点分别有哪些呢2021-11-02 2324

-

基本的时序约束和STA操作流程2021-08-10 6860

-

静态时序的分析原理及详细过程2020-11-25 11538

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2869

-

FPGA进行静态时序分析2019-09-01 3837

-

静态时序分析基础与应用2018-04-03 792

-

时序分析基本概念——STA概述简析2017-12-14 31463

-

静态时序分析在高速 FPGA设计中的应用2011-05-27 819

全部0条评论

快来发表一下你的评论吧 !