浅析芯片及系统电源

电源/新能源

描述

**1 **电源系统

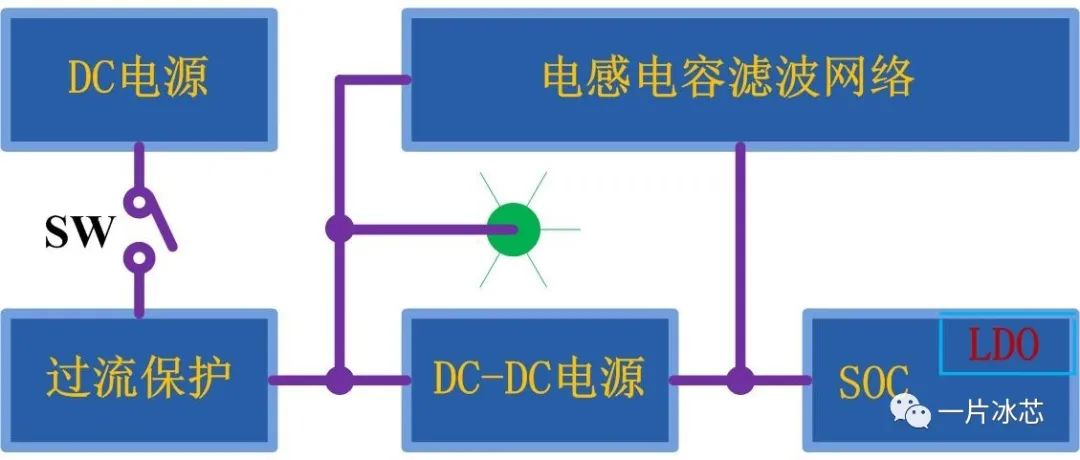

图1是我画的一个完整的电源系统,其中DC电源可以是你笔记本电脑的电源适配器、手机电池或者纽扣电池等,DC电源经开关SW到PCB板上的过流保护,然后送到DC-DC电源(升压/降压),DC-DC电源的输入和输出都需要电感电容滤波,滤波后的电压再送到芯片(SOC)内部。图中绿色小太阳图案代表电源指标灯,LDO表示芯片内部电源。

例如一个手机板级系统包括内存、Flash、CPU、GPU、基带处理器等,每种芯片对电源的需求不同,有的要低压,有的要高压,有的要高性能(模拟电路),有的要高速度(数字电路),有的既要高性能又要高速(模数混合电路),我们的电源系统就是来完成这个任务的。

Fig1. 完整的电源系统

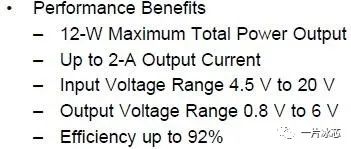

现代集成电路芯片电源电压一般为3.3V/2.5V/1.8V/1.5V/1.2V/1.1V/1.0V/0.9V /0.8V/0.6V/0.5V,换句话说图1中DC-DC电源输出或者SOC输入电压为以上几种。实际应用中无论是wireless还是wireline产品电源都不低于3.3V,因此往往需要降压型的DC-DC电源,我们可以选用TI公司的LMZ12002和PTD08D210W,两种芯片的Spec如图2所示。

(a)LMZ12002的Spec

(b)PTD08D210W的Spec

Fig2. LMZ12002和PTD08D210W的Spec

其中图2(a)给出了LMZ12002输入电压范围为4.5-20V,输出电压范围为0.8-6V,最大输出电流为2A,效率最高可达92%,最大8mV输出电压纹波。

其中图2(b)给出了PTD08D210W输入电压范围为4.75-14V,输出电压范围为0.7-3.6V,最大输出电流为10A,效率最高可达96%,最大11mV输出电压纹波。

TI公司DC-DC芯片宽输入范围降低了图1 DC电源的要求,DC电源可选用6V、8V、12V等典型电压,实际应根据你的应用场景来合理配置DC-DC的输出电压使其能达到最好的性能和最高的效率。

DC-DC电源内部一般都包含一个振荡器,振荡频率在几百kHz到几十MHz,并且输出电压会产生几mV(如LMZ12002输出电压纹波为8mV)到几十mV(如PTD08D210W输出电压纹波为11mV)的电压纹波。4G基带信号带宽为20MHz,mm-Wave5G最大Channel带宽可达400MHz,高速SerDes数据率已经做到了112Gbps,有些应用场景GHz的电源噪声干扰也不得不考虑。这些因素就对芯片内部LDO的电源电压抑制比提出了要求。

**2 **片上电源

2.1 背景

片上电源英文应该叫fully-integrated low-dropout regulator(LDO),当然前边介绍的DC-DC也是一种电源,本期不做重点介绍。

前边介绍的DC-DC是板级系统的第一级电源,翻看LMZ12002和PTD08D210W用户手册我们可以得到DC-DC电源的效率基本可以保证在80%以上,最高可达96%,高的电压转换效率是板级电源系统第一级采用DC-DC的最主要原因。LDO效率一般为输出电压除以输入电压(略小于),如输入电压为3.3V,输出电压为0.8V,效率小于24.2%,为了提高效率应尽量减小输出与输入的电压差。LDO可以产生低噪声、快速响应、高电源电压抑制比(PSRR)的内部电源,因此在高性能模拟电路、快速响应的高速数字电路中LDO不可或缺。

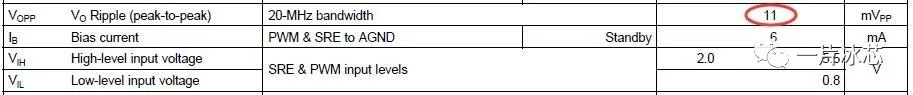

文献[1-5]给出了几种LDO的应用场景,如图3所示。

(a)文献[1]LDO的应用

(b)文献[2]LDO的应用

(c)文献[3]LDO的应用

(d)文献[4-5]LDO的应用

Fig3. 文献[1-5]LDO的应用

图3(a)-(b)应用在了电压模PAM4 Transmitter,速度分别为56Gbps和112Gbps,用于提供稳定及快速响应的电源。图3(c)用于LCVCO,用于产生低噪声和高电源电压抑制比的电源。图3(d)用于高速光通信前端系统中的transimpedance amplifier,用于产生高电源电压抑制比和快速响应的电源。其中文献[4-5]为同一结构,于2014年发表在了ISSCC会议上,次年发表在了TCAS-I期刊上。下面章节我们以图3(d)为例详细分析一下LDO设计时应注意的问题。

2.2 注意事项

一个典型的LDO一般包括两个低频极点,一个位于功率管栅端一个位于输出端,这是因为功率管栅端往往接在误差放大器(EA)的输出,具有较高的输出阻抗和大的寄生电容,Capacitor-less LDO输出一般会挂有pF级的电容,导致输出极点也处于较低的频率,当然片外电容LDO输出端极点频率会更低。

LDO是一个负反馈环路,因此在动手设计一个LDO时应考虑把主极点位置放在什么位置,因为极点的位置会影响环路稳定性。如果把主极点位置放在输出端,重载时单位增益带宽和主极点频率都会增大,当单位增益带宽接近第一非主极点位置时相位裕度会减小,稳定性降低。如果把主极点位置放在内部,需要密勒补偿将内部极点频率推到很低以免在轻载时次极点接近主极点,进而限制环路稳定性,过程如图4所示。

Fig4. 典型LDO轻载重载模式下极点分布

2.3 实例

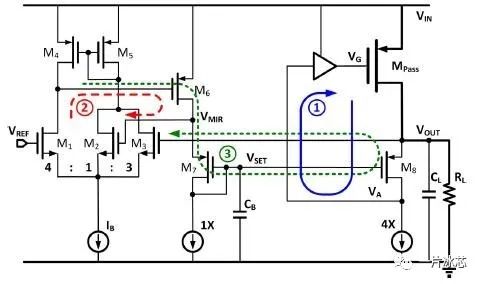

文献[4-5]是一个1.2V转1.0V的LDO,提出了一种采用Flipped Voltage Follower(FVF)及Buffer Impedance Attenuation(BIA)技术的三环Capacitor-less的LDO,其特点是整个频带范围内PSRR小于-12dB且具有快速响应,原理图如图5所示。

Fig5. 片上三环LDO原理图

合理设置三输入EA(图5中M1-M3)M2和M3的比例可实现输出端(图5 V OUT )DC电压精度及环路稳定性之间最优值。M11在轻载和重载时设置在亚阈值或临近亚阈值区以得到最大的gm,从而将图5 Buffered FVF环路极点推到高频。

三个环路标注在了图6所示的结构图,环路1提供快速响应和较低的环路增益,环路2 DC增益大,带宽小可将VREF精确复制到VMIR或V SET ,环路3由VOUT反馈到三输入误差放大器M3的栅端提高了VOUT的DC精度。三个环路各司其职产生一个具有快速响应和全频带范围内高PSRR的高精度电压。

Fig6. 片上三环LDO结构图

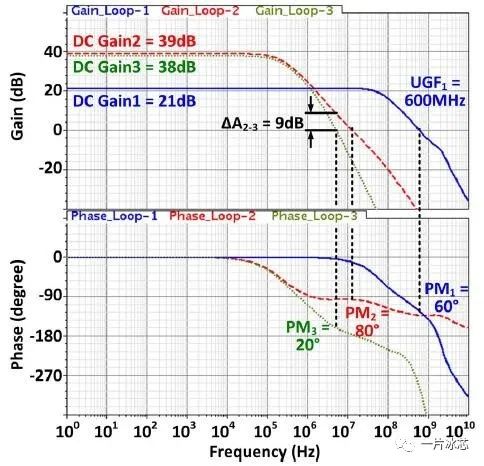

图7给出了重载模式下三环路的幅频和相频特性曲线。环路3相位裕度只有20度,这似乎影响了环路稳定性,但考虑到环路2和环路3共用一个误差放大器,环路稳定性要看整体的,只要环路2和环路3整体相位裕度够大就行,不用在意整体环路中的某一环路相位裕度不够大(就像有些带隙基准或constant-gm偏置中允许存在正反馈一样,只要正反馈小于1且整体是一个负反馈环路就没有问题)。

Fig7. 重载模式下的幅频和相频特性曲线

**3 **思考与讨论

该结构输出端接有140pF电容,在该光通信接收端的应用中是否有必要在片上集成如此大的电容?该应用中是否要考虑放大器的噪声?

-

浅析开关型稳压电源结构原理2012-08-06 2234

-

电源滤波电路浅析2013-02-06 11790

-

机器人操作系统浅析2016-09-28 2971

-

浅析伺服系统应用中的惯量匹配问题2021-09-07 1690

-

浅析TD-SCDMA的系统特点2009-05-20 704

-

TD_SCDMA系统浅析2009-05-22 599

-

浅析高频开关电源的热设计2009-07-15 1240

-

浅析语音芯片与语音合成芯片的异同2010-04-21 1496

-

大屏幕彩电开关稳压电源效率浅析2011-10-11 893

-

UPS电源输入跳闸浅析及解决办法2011-11-10 1447

-

浅析引线阻抗差异和输出滤波环节差异2016-03-30 841

-

浅析基于数据加密的网络通信系统的设计与应用2016-04-19 839

-

浅析BMS上电源芯片SBC应用2022-01-05 1589

-

浅析消防设备电源监控系统设计及应用2024-03-12 1555

-

技术科普 | 芯片设计中的LEF文件浅析2024-11-13 1286

全部0条评论

快来发表一下你的评论吧 !