物理设计中的问题详解

电子说

描述

物理设计中的问题

设计寄生效应

寄生电阻

·如果电阻增加,延迟也会增加(延迟= RC)

·随着技术的缩小,互连也会缩小,因此导线电阻将会增加

·为了避免这种情况我们将增加互连的高度

寄生电容

·随着技术的不断缩小,网络高度不断增加,因此侧壁电容不断增加

·随着技术的缩小,电介质变得更薄,电容将增加

·减小电容,尽量减少可共用的表面积

·所以我们在设计时保持相邻金属层的垂直和水平

寄生电感

·互感影响:高频母线

·自感影响:时钟网络

·为了限制电感,我们为高频信号提供电流返回路径

·隔离和屏蔽是可能的补救措施

·经验法则是,当信号路径的长度足够长,达到波长的一定百分比时,线路本身就开始成为信号完整性的问题

·对于长线网和电源/时钟线,在 500MHz 以上和 130nm 以下尤为突出

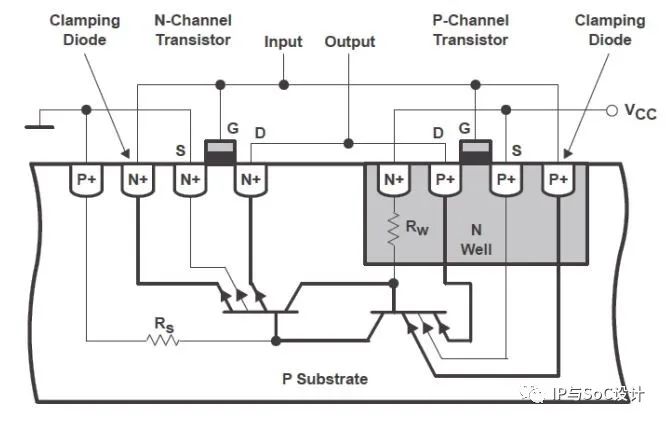

闩锁

什么是闩锁?

·CMOS/BiCMOS电路出现的现象

·在 VDD 电源和地之间生成低阻抗路径

闩锁原因

·由于寄生PNP和NPN晶体管之间的再生反馈

对设计的影响

·PN结会产生寄生晶闸管

·PNP/NPN结构形式

·需要相当大的输入电流才能激活

·由寄生晶体管组成的晶闸管被触发并在 VDD 和 GND 之间产生短路

·由于 VDD 和 GND 直接连接,导致自毁/系统故障

NPN晶体管

·N沟道MOSFET的发射极-漏极/源极

·底座-P基板

·集电极 – N 井,其中有互补的 P 沟道 MOSFET

PNP晶体管

·P沟道MOSFET的发射极-漏极/源极

·基极 – N 阱,其中有互补的 P 沟道 MOSFET

·集电极-P基板

晶闸管/SCR/PNPN二极管

·P沟道MOSFET的阳极-漏极/源极

·N沟道MOSFET的阴极-漏极/源极

·栅极-P基板

闩锁的补救措施

** 抗闩锁 CMOS 工艺**

·降低寄生晶体管的增益(使用硅起始材料,在高掺杂衬底上有薄外延层)

·将保持电压提高至 VDD 电源以上

·增加衬底和阱的掺杂浓度(但会导致更高的VT)

·逆行阱结构(底部高掺杂,顶部轻掺杂)

** 布局技巧**

·NMOS和PMOS之间有足够的空间

·这降低了寄生晶体管的电流增益

·成功有限,因为只能增加到一定限度

·通过保持基板和孔的接触尽可能靠近来减少RS和RW

·将基板触点尽可能靠近连接到电源轨的晶体管的源极连接(VSS n 器件、VDD p 器件)

·这会降低 RSUBSTRATE 和 RWELL 的值

·一种非常保守的规则是为每个电源(VSS 或 VDD)连接放置一个衬底触点

·标准中。基于细胞的设计,常见的 Well Tap 根据需要取出

·保护环

·晶体管的增益降低(在模拟设计中)

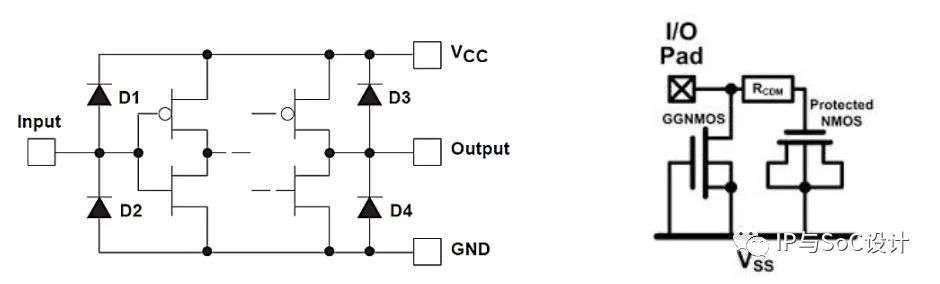

静电放电 (ESD)

静电放电 (ESD)

·当两种非导电材料摩擦在一起然后分离时,相反的静电电荷保留在两者上,试图相互平衡

·由于人为操作或机器接触而产生的静电荷瞬态放电

静电放电的原因

·CMOS 的栅极氧化层薄而脆弱,使得 ESD 保护对于 CMOS 至关重要

·可能是由于电感或电容耦合

·金属化过程中通过摩擦去除多余金属时可能会发生ESD

· ESD 发生得如此之快,以至于普通 GND 线会表现出太大的电感,无法在造成损坏之前耗尽电荷

对设计的影响

·如果热引发,ESD 也会烧毁器件/互连

·PMOS的ESD保护能力强于NMOS,因为NMOS的回弹保持电压较低

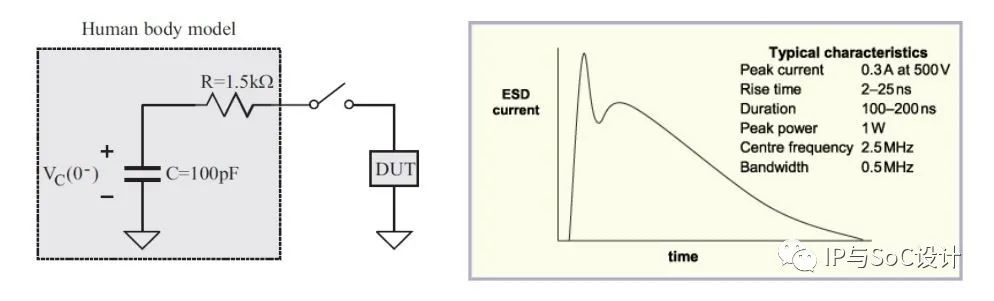

人体模型 (HBM)

·人体的实际电容在150pF到500pF之间,人体的内阻在几千欧到几百欧之间

·峰值电流约1.3A,上升时间约10-30ns

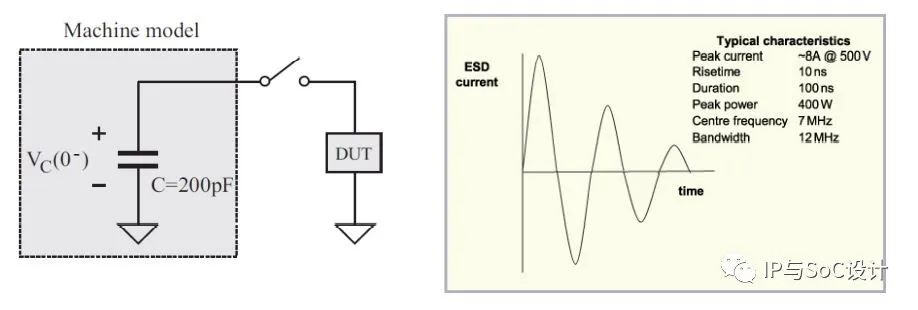

机器型号(MM)

·MM对制造/测试设备的ESD进行建模

·峰值电流约3.7A,上升时间约15-30ns,带宽约12 MHz

·由于体电阻为零,带电机器引起的ESD应力很严重

·MM ESD耐受电压通常为HBM的十分之一

·大多数ESD保护电路只能保护HBM和MM

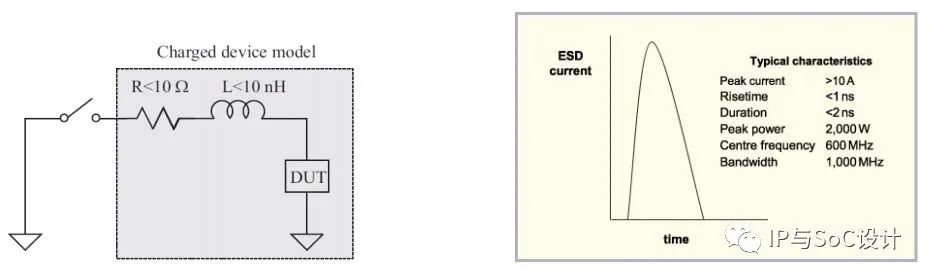

带电器件模型 (CDM)

·CDM 对带电集成电路的 ESD 进行建模

·随着越来越多的电路和功能集成,导致芯片尺寸变大,从而提供了大的体电容,进而在 IC 体中存储 CDM 的电荷

·模型中的电感主要来自键合线的电感

·与 HBM 和 MM 应力的热失效特征相比,栅氧化层击穿是 CDM 应力的特征失效

·CDM 应力是最难防范的 ESD 应力,因为瞬态速度最快,并且具有最大。峰值电流

·峰值电流约10A,上升时间约1ns

静电放电保护

钳位二极管的集成

·限制危险电压并将过量电流传导到电路的安全区域

保护二极管

·正常运行时面向阻塞

·位于要保护的组件的连接和电源电压线之间的安全区域主要由电源电压连接组成

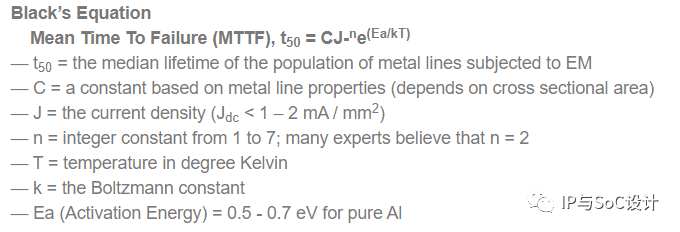

电迁移

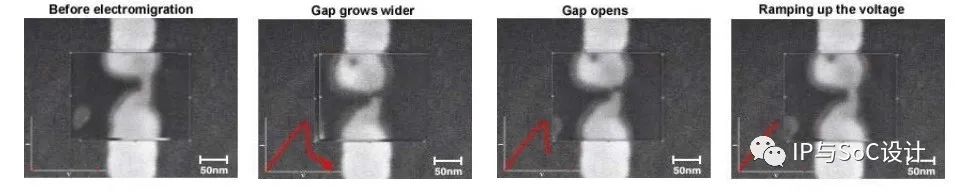

电迁移 (EM)

·高能电子撞击材料中的原子并导致它们移动位置而引起的失效机制

·电场影响下原子的增强和定向迁移

电迁移的原因

·形成正反馈路径,其中电磁将导致原子沿着导线移动,稍微缩小该位置的导线宽度并增加电流密度

·电流密度的增加进一步增加了电迁移,导致更多的原子被移位 由于传导电子和扩散金属原子之间的动量转移,导体中离子的逐渐移动引起材料的传输

·在高电流密度区域问题最严重

·随着尺寸的减小而显着,对于单向 (DC) 电流最为显着

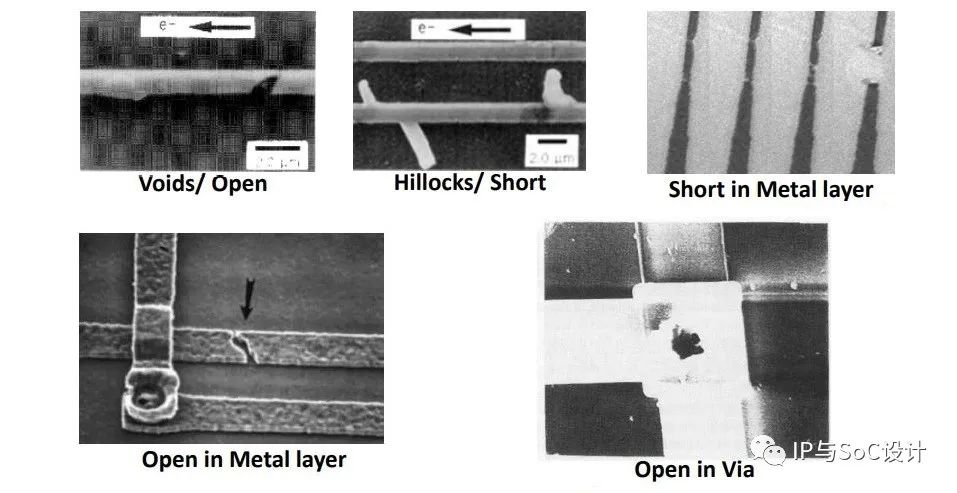

对设计的影响

·过高的EM会导致开路(空洞)和短路(Hillocks),从而降低芯片的可靠性

·更快地接近设备的使用寿命

·功耗增加

·更高的片上温度

·高压操作

·高频开关

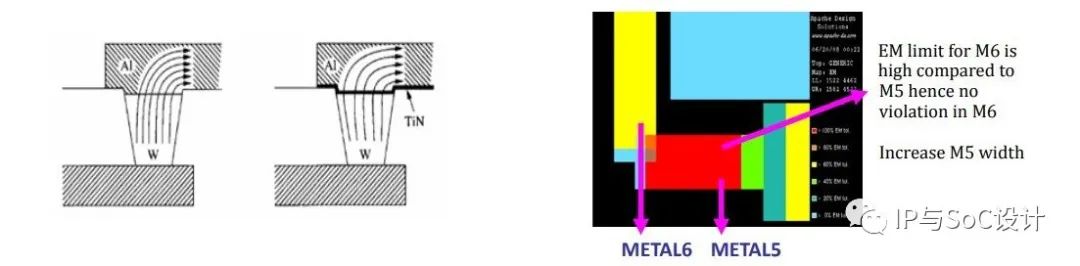

EM 补救措施和预防措施

·导线加宽以降低电流密度

·良好的电源管理技术

·更大的电网用于电网(将电网放在更厚的层上)

·信号网线加宽

·更好的电网规划

·Power Greedy 网络的双倍调整

·提供冗余过孔

·设计电路以在较低电压水平下运行

·通过与铜合金化可以提高电磁抗性

·使用热感知 IC 设计方法控制温度

·减少变异性的DFM技术

·此外,需要注意“碟形”效应(CMP)

EM 检查的类型

与电流相关

·平均EM检查

·RMS EM 检查

·峰值EM检查

与 篮网相关

·信号电磁检查

·电源电磁检查

·所有这些 EM 检查的限制将在技术文件中指定为设备最小寿命的函数,具体取决于应用

·信号 EM 需要满足所有三个与电流相关的 EM 检查,除非另有说明

·对于电力网,满足平均EM数就足够了

电磁故障机制

·时序失败:导线变窄会增加导线电阻,如果信号无法再在时钟周期内传播,可能会导致时序失败

·功能故障:电迁移将持续到导线完全断裂,不允许进一步的电流流动并导致功能故障

EM 规则类型

·基于金属层(这是旧技术中使用的唯一规则)

·金属长度或宽度相关的 EM 规则

·上下金属的长度和宽度也取决于过孔宽度

·多项式的复杂规则

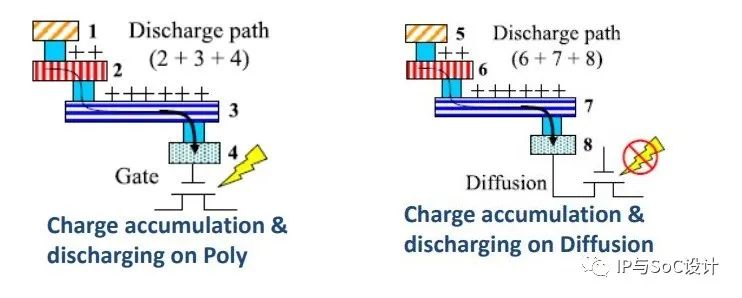

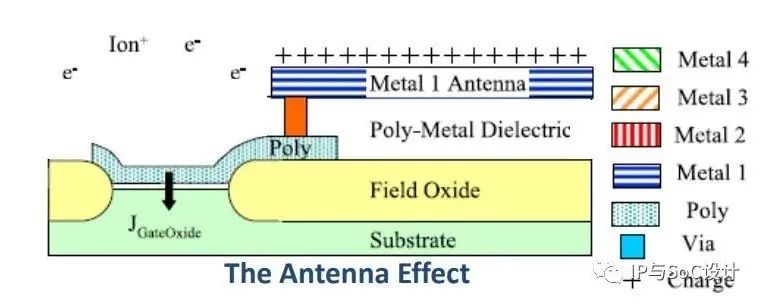

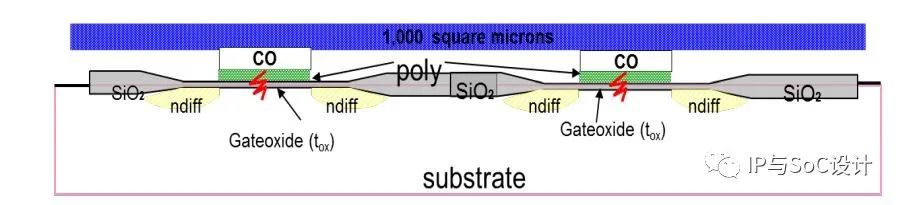

天线效应

天线效应

·金属化过程中连接到隔离栅极(多晶硅)的金属段中电荷积累的现象

·这种现象发生在加工过程中,所以又称为过程天线效应(PAE)

·当导电网充当天线时发生,放大电荷效应

·导电层接收电荷,称为天线效应

天线效应产生的原因

·等离子蚀刻过程中的辉光放电会导致充电,当发生在导电层中时会导致天线效应,因此称为等离子诱导/过程诱导损伤(PID)

·当未被氧化物屏蔽层覆盖的导体层直接暴露于等离子体时,会发生充电

·在焊接等过程中,芯片受到一些屏蔽的保护

·但在制作过程中没有这样的保护,会导致天线效应

·对于铝基工艺,PAE 在蚀刻阶段突出,对于铜基工艺,PAE 在化学机械抛光 (CMP) 阶段突出

·如果较高金属层的区域通过较低金属层连接到栅极,则较高金属层的电荷会添加到较低金属层,这也会导致 PAE,称为累积天线效应

对设计的影响

·如果直接连接到栅极的层区域静电荷通过栅极放电,则放电会损坏绝缘栅极的氧化物并导致芯片失效

·福勒-诺德海姆(FN)隧道电流将通过薄氧化物放电并对其造成损坏

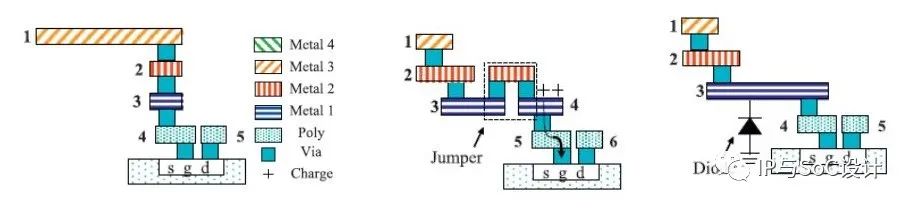

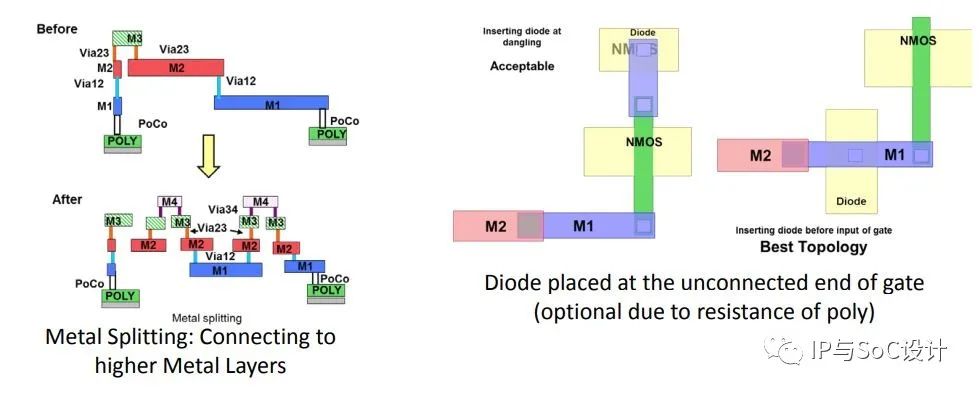

PAE 的补救措施

·为布线分配更高的金属层

·较高的金属层不会直接与Gate连接,通过Via连接连接各种金属

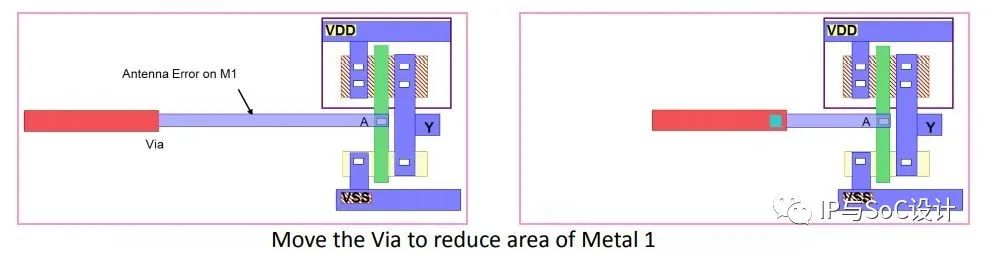

·插入跳线

·如果PAE位于较低层,则可以通过跳线将其连接到较高层来减少PAE

·跳线将减少连接到门的外围金属长度

·连接天线二极管

·如果是在高层,跳线就不行了,需要二极管

·一旦金属/多晶硅上感应出额外的电荷,二极管就会将额外的电荷转移到基板上

·但是对于缓冲器插入,较高的金属层必须到达较低的金属层(M1或M2)以连接到缓冲器的引脚并返回,并且可能没有足够的空间用于缓冲器插入

·布线后我们只进行天线检查,因此缓冲区插入可能会导致拥塞和DRC违规

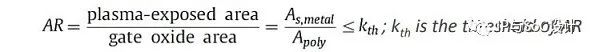

天线比率 (AR)

·防止金属/多晶硅层蚀刻期间电荷积累的设计规则,限制了连接到栅极氧化物的金属段的面积

·代工厂为其制造的芯片设定了最大允许的 AR

·AR 定义为等离子暴露面积 As,metal 与栅极氧化面积 Apoly 的比率,公式如下:

·此规则适用于连接到门的任何金属段

天线效应可能性示例

·假设代工厂设置最大允许天线比率为 500

·如果网络有两个输入门,每个输入门的面积为 1 平方微米,则任何连接到门且面积大于 1,000 平方微米的金属层都存在工艺天线违规,因为它们会导致天线比率高于500

随着技术的萎缩而占据主导地位

·当氧化物厚度减少时

·芯片中添加了更多的金属结构

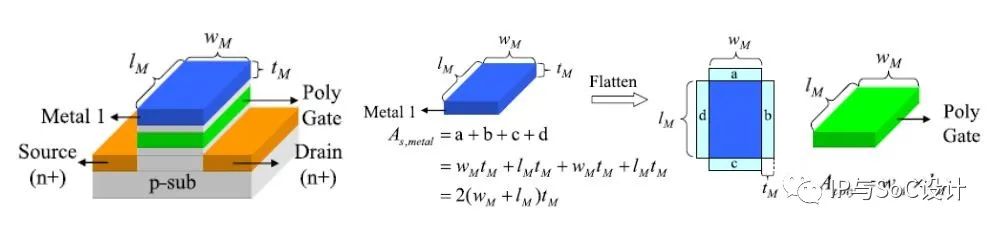

天线 (ANT) 规则

·天线比

·对于铝的蚀刻阶段(金属沉积)

·在此步骤中,金属顶部受到抗蚀剂保护,因此此过程的天线规则应基于金属侧壁区域

·用于化学机械抛光(CMP)阶段的铜

·CMP过程中发生电荷积累

·在此过程中,金属的侧面受到保护,因此天线规则需要基于金属的顶部表面积

·工艺中使用的金属取决于技术

·从28nm开始铝正在取代铜

PAE 作为制造过程的副作用

·等离子蚀刻机/离子注入机将电荷感应到与栅极氧化物连接的各种结构中

·这种感应电荷会破坏氧化层 - 造成永久性损坏

·导体层图形蚀刻工艺

·累积电荷量与周长成正比

·灰化工艺

·累积电荷量与面积成正比

·灰化工艺去除导体层蚀刻工艺后剩余的光刻胶层

·在工艺后期,导体层图形区域直接暴露于等离子体

·接触蚀刻工艺

·累积电荷量与触点总面积成正比

·接触蚀刻工艺在两个导体层之间挖孔

·在工艺后期,下导体层图案上的所有接触点区域直接暴露于等离子体

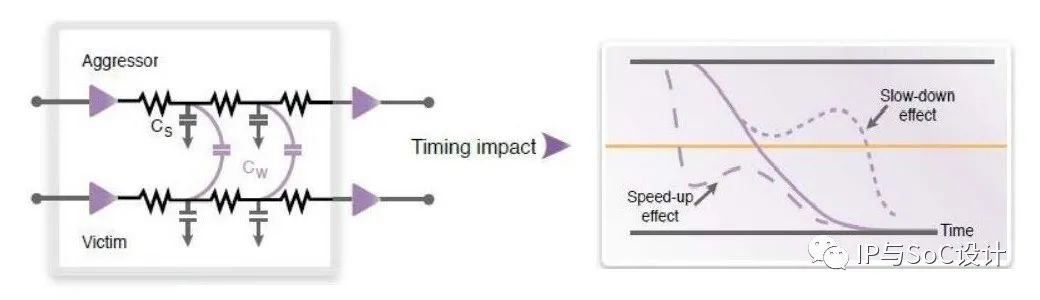

相声

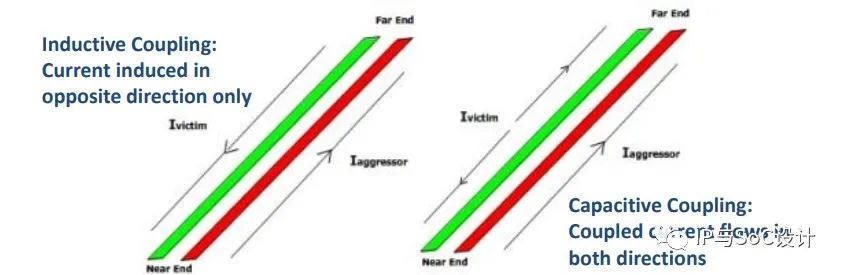

什么是串扰?

·指因电容/电感耦合而影响附近正在传输的另一个信号的信号

·串扰是两条或多条相邻线路之间不必要的能量耦合,它会改变所需的信号,也称为 Xtalk

·发生在长的相邻电线上

·可以解释为能量从一条线到另一条线的耦合:

·互电容,Cm(由于电场)

·互感,Lm(由于磁场)

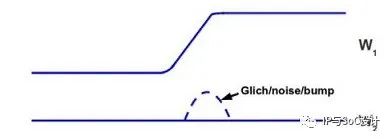

串扰对设计的影响

·功能故障

·噪声引起的故障

·如果Glitch持续时间是时钟周期持续时间,则额外的时钟周期效应

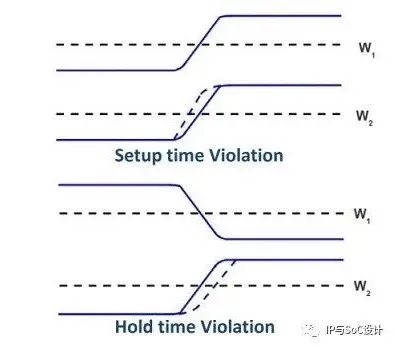

·计时违规

·如果攻击者转向与受害者相反的方向:建立时间违规

·如果攻击者转向与受害者相同的方向:保持时间违规

·如果受害线路的特性阻抗两端没有端接,则感应的杂散信号会在线路的两端反射,并沿线路的相反方向传播

·因此,反射的近端串扰最终可能出现在远端,反之亦然

串扰的类型

·从实际信号线(干扰源)耦合到安静的无源受害线路的能量,以便传输的能量“返回”到受害线路的起点。这称为后向串扰或近端串扰

·能量从有源信号线(干扰源)耦合到安静的无源受害线路,以便传输的能量“向前传播”到受害线路的末端。这称为前向串扰或远端串扰

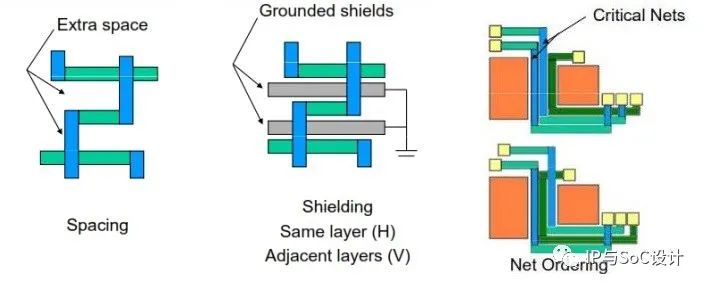

避免 Xtalk 的补救措施

·这是一个三维问题,所以高度、宽度和长度很重要

·可以通过改变关键网络之间的间距来修复噪声/碰撞违规

·通过地线将时钟网络(关键网络)与其他网络屏蔽开

·网络重新排序

·避免长距离并行布线关键网络

·将时钟网络(关键网络)最小宽度从正常值修改为更大的值

·这使得路由器跳过时钟网络附近的网格以防止间距违规

·该技术不仅可以减少串扰,而且由于线宽更大、侧壁电容更小,电阻也更低

·可以通过扩大受害者的规模(增加驱动强度)或缩小攻击者的规模(减少驱动强度)来解决

软错误

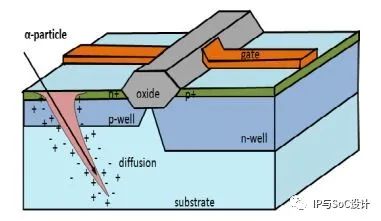

软错误(随机粒子错误)

·软错误是晶体管逻辑值错误变化的现象,可能由多种因素引起,包括信号电压波动、电源噪声、电感耦合效应等,但大多数软错误由宇宙粒子撞击芯片引起

·随着技术的扩展,即使是低能粒子也会导致软错误

·软错误是由于包装材料中杂质的 α 粒子或宇宙射线中子的粒子撞击而发生的辐射引起的故障

·当粒子撞击硅基板时,它们会产生空穴电子对,然后通过漂移和扩散机制由 PN 结收集

·收集到的电荷会产生瞬态电流脉冲,如果它足够大,它可以翻转存储在状态保存元件(位单元、锁存器等)中的值

·这些冷门被称为单项冷门(SEU)

对设计的影响

·软错误可能导致不正确的结果、分段错误、应用程序或系统崩溃,甚至系统进入无限循环

·当组合电路中发生粒子撞击时,结果是一个故障,然后该故障可以传播到锁存器,在锁存器中可以对其进行计时并锁存不正确的数据

避免软错误的预防措施

·辐射强化:降低数字电路软错误率的技术

·辐射硬化通常是通过增加节点处共享漏极/源极区域的晶体管的尺寸来实现的

自加热

·如果电流流过电线,则由于电线的电阻,会产生热量

·电线周围的氧化物是热绝缘体,因此热量容易在电线中积聚

·更热的电线电阻更大并且速度变慢

·电线自热对大容量 CMOS IC 的电源线的影响可以忽略不计

·自加热设计规则/自加热限制交流电流密度以确保可靠性

·典型限值:JRMS < 1.5 MA/ cm2(对于铝网)

·它限制了由于载流或任何附近互连的温度升高而导致的不可避免的电迁移寿命下降

审核编辑:汤梓红

-

Linux内核的物理内存组织结构详解2023-08-21 1288

-

一文详解物理信息神经网络2024-12-05 16385

-

详解电容在实际电路中应用2012-03-08 11808

-

好书分享!《详解MATLAB在科学计算中的应用》2012-05-29 14219

-

为什么AD中设置物理网络时里面是空的?2019-09-29 3690

-

磁路中的物理量及基本定律2021-01-25 1951

-

OrCAD中创建总线及用法详解2011-12-02 28717

-

VC-MFC中socket编程详解2016-09-01 905

-

VB中关于MSComm控件使用详解2016-12-16 1114

-

详解电源中的电容作用及注意事项2017-01-14 1056

-

Linux系统中EXP命令详解质量汇总2021-05-14 1242

-

KEIL中启动文件详解(汇编语言)2021-12-04 893

-

CCIX物理层详解2022-08-15 3590

-

RA MCU CANFD在FSP中的配置详解2024-06-19 1908

-

电力电子中的坐标变换详解2025-02-17 322

全部0条评论

快来发表一下你的评论吧 !