时序分析基本概念介绍<generate clock>

电子说

描述

今天我们要介绍的时序分析概念是 generate clock 。中文名为生成时钟。generate clock定义在sdc中,是一个重要的时钟概念。

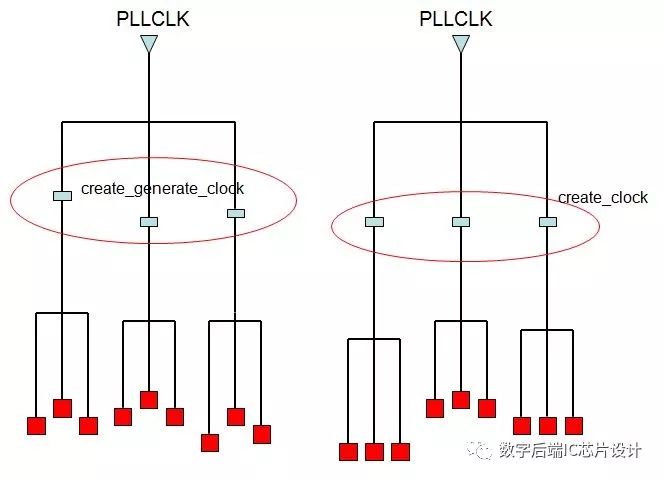

它从master clock中取得的时钟定义。master clock就是指create_clock命令指定的时钟产生点,如图所示:

我们可以用如下命令来描述generated clocks:

#定义master clock

***create_clock -name CLKP -period 10 ***

-waveform {0 5} [get_pins UPLL0/CLKOUT]

#在Q点定义generated clock

***create_generated_clock -name CLKPDIV2 ***

*** -source UPLL0/CLKOUT -add ***

***-master_clock CLKP -divide_by 2 [get_pins UFF0/Q] ***

一般我们把时钟的源头会定义成 create_clock ,而分频时钟则会定义为 create_generated_clock . 两者的主要区别在于CTS步骤,generated clock并不会产生新的clock domain, 而且定义generated clock后,clock path的起点始终位于master clock, 这样source latency并不会重新的计算。

上图中描述,如果我们给PLLCLK出来的三个分频点定义为generate clock,则在trace clock tree时,工具会穿过这三个点,并不会产生新的clock,对工具来说,它会balance所有clock sink。这种情况下,clock tree通常会做得比较长一些。

相反,如果我们给这三个分频点定义为create_clock,则在trace clock tree时,这三个点会生成各自新的clock tree,属于他们自己的sink会分别做balance,但是相互之间会不做balance。而且它本身的input clock pin也会被当成PLLCLK的sink进行balance。

-

时序分析基本概念介绍&lt;Combinational logic&gt;2023-07-10 1906

-

时序分析基本概念介绍&lt;Critical Path&gt;2023-07-07 2525

-

时序分析基本概念介绍&lt;Skew&gt;2023-07-05 5664

-

时序分析基本概念介绍&lt;Operating Condition&gt;2023-07-04 4791

-

介绍时序分析的基本概念lookup table2023-07-03 2953

-

时序分析基本概念之生成时钟详细资料介绍描述2018-09-24 10071

-

详细介绍时序基本概念Timing arc2018-01-02 26238

全部0条评论

快来发表一下你的评论吧 !