带隙基准电路设计原理

电子说

1.4w人已加入

描述

带隙基准广泛应用于模拟集成电路中。带隙基准电路输出的基准电压可以为模拟集成电路提供稳定的参考电压或参考电流,因此,要求带隙基准电路具有较强的抗电源电压波动干扰的能力、环境温度急剧变化的能力,即对带隙基准电路的电源电压抑制比、温度漂移有明确的指标要求,同时需要尽可能的降低带隙基准电路的电路复杂度和工艺加工成本。

利用TCAD半导体器件仿真软件和TSPICE集成电路仿真软件完成无运放高电源电压抑制能力、低温度漂移的CMOS带隙基准集成电路的仿真设计。利用TCAD完成了带隙基准电路核心器件(PNP-BJT、NMOSFET、PMOSFET)的器件结构、工艺流程和电特性仿真。

TSPICE集成电路仿真采用TCAD输出的模型参数,对带隙基准电路有源器件模型参数、结构参数、电阻阻值的选择进行优化,最后完成了高电源抑制比、低温度漂移的带隙基准电路设计。

带隙基准电路设计原理:

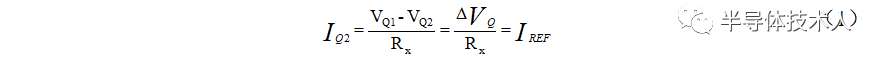

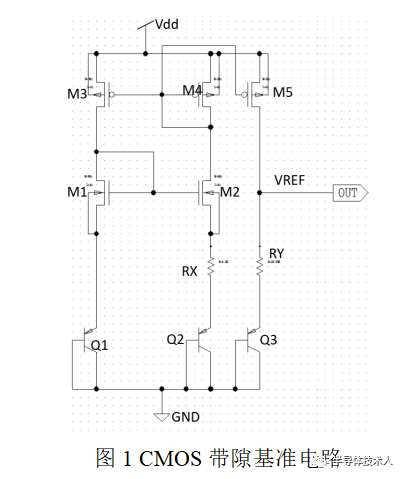

通过具有正温度系数的电压与具有负温度系数的电压之和,二者的温度系数相互抵消,来实现与温度无关的电源基准。图1为所设计的基于CMOS技术的带隙基准电路。M1和M2的源端电位应相等,则有:

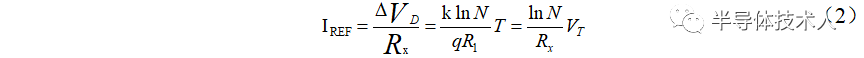

如果Q2的发射区面积是Q1的N倍,则有:

IREF与T成正比,IREF通过M5对外输出。

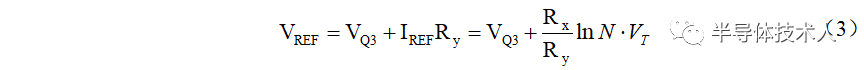

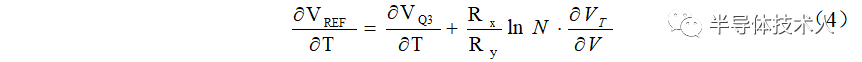

基准电压VREF为:

VQ3与T成反比。

在室温附近,具有零温度系数的VREF值为1.21V。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

带隙基准电路集成有源器件仿真设计2023-07-06 2806

-

带隙基准是什么?带隙基准的结构是由哪些部分组成的?2021-06-22 2124

-

请问有没有做过cadence的CMOS带隙基准电路设计的?2020-05-17 41518

-

带隙基准是什么_带隙基准电路的优点2019-08-06 9672

-

一种高精度BiCMOS电流模带隙基准电路设计2019-07-12 3069

-

带隙基准电路_cmos无运放带隙基准源2018-01-11 18763

-

cmos带隙基准电压源设计2017-11-24 25036

-

带隙基准电压源及过温保护电路2017-09-07 1417

-

一种高电源抑制低温漂带隙基准电路设计2017-01-03 710

-

高电源抑制比带隙基准电路设计2013-03-13 912

-

带隙电压基准源的设计与分析2012-05-24 1859

-

基于汽车环境的带隙基准电压源的设计2010-12-22 846

-

新型BiCMOS带隙基准电路的设计2010-11-02 2836

-

带隙基准电路的研究2009-03-11 1695

全部0条评论

快来发表一下你的评论吧 !