带隙基准电路集成有源器件仿真设计

电子说

描述

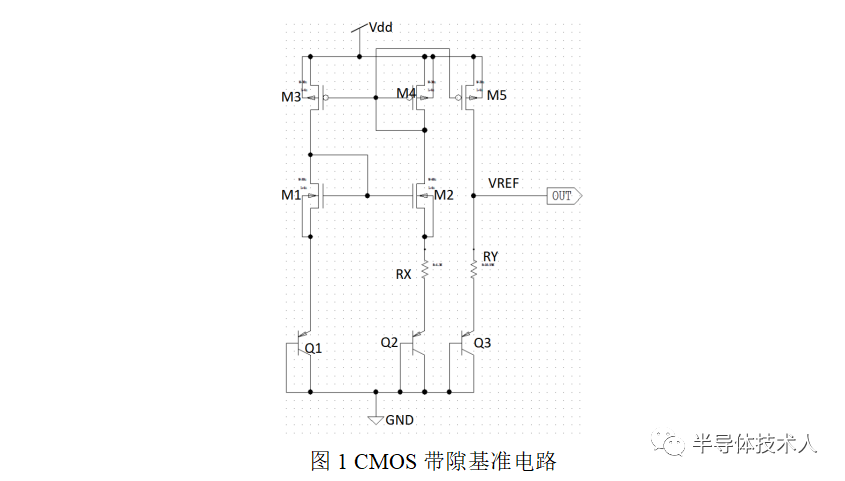

带隙基准广泛应用于模拟集成电路中。带隙基准电路输出的基准电压可以为模拟集成电路提供稳定的参考电压或参考电流,因此,要求带隙基准电路具有较强的抗电源电压波动干扰的能力、环境温度急剧变化的能力,即对带隙基准电路的电源电压抑制比、温度漂移有明确的指标要求,同时需要尽可能的降低带隙基准电路的电路复杂度和工艺加工成本。

集成器件PNP-BJT(Q1、Q2、Q3)采用多晶硅发射极PNP-BJT结构。多晶硅发射极晶体管结构可以很好的折中电流放大倍数、基区电阻、特征频率参数之间的矛盾。可以在满足电流放大倍数的基础上尽可能的降低基区电阻,减弱基区电导调制效应,从而获得较高的特征频率、截止频率和功率增益。

PNP-BJT 结构参数:发射结结深为0.157μm;集电结结深为0.453μm;基区宽度为0.295μm;基区方块电阻为1906.3Ω/□;多晶硅发射极方块电阻为219.968Ω/□。PNP-BJT电学性能:峰值集电极电流密度为2.589×10-5A/μm;峰值电流增益为72.97;峰值特征频率为1.79GHz。在PNP-BJT中提取出结构参数、电学参数,应用于SPICE仿真。图2 为仿真得到的PNP-BJT电学性能。

集成器件NMOSFET(M1、M2)结构参数:NMOSFET宽度1.2μm,衬底厚度5μm。衬底晶向<100>,硼掺杂浓度为1×1014cm-3。栅氧化层厚度0.01μm;源漏区结深0.174μm;沟道表面浓度3.734×1016cm-3;源漏区方块电阻:29.09Ω/□。LDD方块电阻:2176.84 Ω/□;沟道表面浓度3.7×1016/cm3;界面电荷3×1010C/cm2。NMOSFET电学参数:nvt=0.534386;nbeta=0.00023928;ntheta=0.131034,VB=0.0V,QSS=1×1010/cm2,VTH=0.622490 V。在NMOSFET中提取出结构参数、电学参数,应用于SPICE仿真。图3 为仿真得到的NMOSFET电学性能。

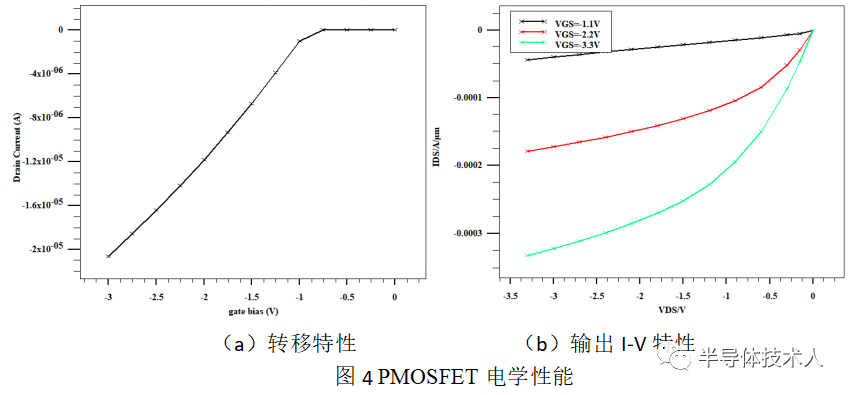

集成器件PMOSFET(M3、M4、M5)结构参数:PMOSFET宽度1.2μm,衬底厚度5μm。衬底晶向<100>,磷掺杂浓度为1×1014cm-3。栅氧化层厚度0.00905μm;源漏区结深0.145μm;沟道表面浓度4.978×1016cm-3;源漏区方块电阻:156.629Ω/□。LDD方块电阻:867.237 Ω/□;界面电荷3×1010C/cm2。PMOSFET电学参数:PVTH=-0.6325V;PBETA=0.000115525,PTHETA=0.0923632;VB=0.0V,QSS=1×1010/cm2,VTH=-0.6325V。在PMOSFET中提取出结构参数、电学参数,应用于SPICE仿真。图4为仿真得到的PMOSFET电学性能。

-

带隙基准电路设计原理2023-07-06 3931

-

带隙基准是什么?带隙基准的结构是由哪些部分组成的?2021-06-22 2112

-

带隙基准是什么_带隙基准电路的优点2019-08-06 9656

-

一种高精度BiCMOS电流模带隙基准电路设计2019-07-12 3059

-

基于LDO稳压器的带隙基准电压源设计2018-10-09 3326

-

带隙基准电路_cmos无运放带隙基准源2018-01-11 18732

-

cmos带隙基准电压源设计2017-11-24 25018

-

带隙电压基准源的设计与分析2012-05-24 1853

-

CMOS带隙基准电压源曲率校正方法2011-05-25 1184

-

基于汽车环境的带隙基准电压源的设计2010-12-22 841

-

新型BiCMOS带隙基准电路的设计2010-11-02 2823

-

带隙基准源的现状及其发展趋势2010-07-29 871

-

基于BiCMOS工艺的带隙基准电压源设计2010-01-11 864

-

带隙基准电路的研究2009-03-11 1689

全部0条评论

快来发表一下你的评论吧 !