电子行业专题分析报告:大算力时代下先进封装大有可为

电子说

描述

1 先进封装成为后摩尔时代提升系统性能的主流趋势

1.1 摩尔定律经济效能达到瓶颈,先进封装提升芯片系统性能

摩尔定律持续推进带来的经济效能达到瓶颈。摩尔定律是指随着技术演进,芯片上容 纳的晶体管数量会呈指数级增长,每1.5-2年翻一倍,同时带来芯片性能提升一倍或 成本下降一半的效应。随着芯片制程工艺的不断发展,芯片上容纳的晶体管数量不断 增加,但单位数量晶体管的成本下降幅度正在持续降低。根据IBS的统计及预测,从 16nm到10nm,每10亿颗晶体管的成本降低了30.7%,从7nm到5nm成本下降了17.8%,而 从5nm到3nm成本仅下降了4.2%。

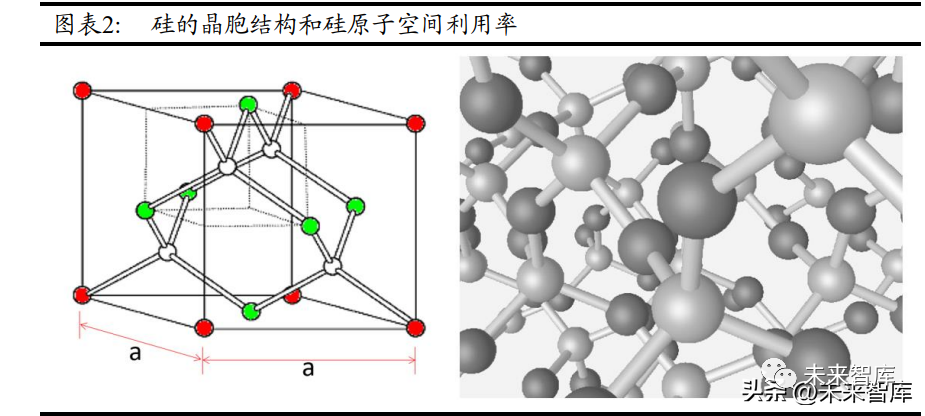

集成电路中晶体管尺寸的微缩逐渐接近硅原子的物理极限。芯片工艺尺寸日益走向 极致(3nm至1nm),而1nm的宽度中仅能容纳2个硅原子晶格,如若 进一步微缩,就将进入量子物理的世界,面临现阶段较为棘手的量子隧穿效应和散热 等问题。晶体管数量不断增加会造成短沟道效应,即当通道长度缩短到量子物理阈值 时会产生量子隧穿效应,从而使晶体管的性能衰减。此外,晶体管工作会持续产生热 量,当数以万计的晶体管以较短的间隔放置时,也需要解决散热问题。

先进封装成为超越摩尔定律、提升系统性能的关键路径之一。目前集成电路发展主要 沿着两个技术路线进行,一个是摩尔定律的延伸,即向芯片小型化的方向发展,通过 微缩半导体器件的晶体管尺寸以增加可容纳的晶体管数量,以单个芯片性能的提升 为目标;另一个是超越摩尔定律,即以先进封装技术的发展为主要方向,将处理、模 拟等多种芯片集成在一个系统内,实现系统级封装(System in Package, SiP),以系 统性能的提升为目标。

1.2 封装技术发展趋势:芯片性能不断提高、系统趋于小型化

封装技术的发展史是芯片性能不断提高、系统不断小型化的历史。封装是半导体晶圆 制造的后道工序之一,目的是支撑、保护芯片,使芯片与外界电路连接、增强导热性 能等。封装技术的发展大致分为4个阶段:第一、第二阶段(1990年以前)以DIP、SOP 和LCC等技术为主,属于传统封装;第三阶段(1990至2000年)已经开始应用先进封 装技术,这一阶段BGA、CSP和FC技术已开始大规模生产;第四阶段(2000年至今), 先进封装技术从二维开始向三维拓展,出现了2.5D/3D封装、晶圆级封装、扇出型封 装等封装技术。先进封装也称为高密度封装(HDAP,High Density Advanced Package), 采用先进的设计和工艺对芯片进行封装级重构,并有效提升系统性能。相较于传统封 装,先进封装具有引脚数量增加、芯片系统更小型化且系统集成度更高等特点。

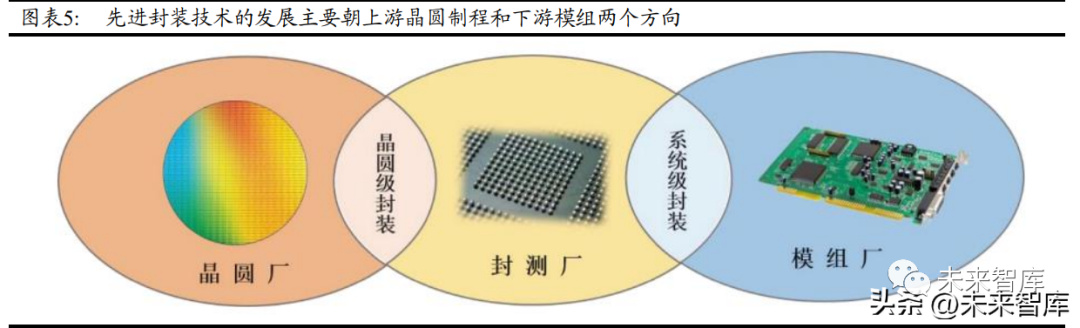

先进封装技术的发展主要朝上游晶圆制程和下游模组两个方向。1)向上游晶圆制 程领域发展,该方向发展的技术即晶圆级封装,通过晶圆重构工艺在晶圆上完成重 布线,并通过晶圆凸点工艺形成与外部互联的金属凸点以进行封装,该技术的特点 是可以在更小的封装面积下容纳更多的引脚;2)向下游模组领域拓展,即发展系 统级封装技术,将以前分散贴装在PCB板上的多种功能芯片,包括处理器、存储器等功能芯片以及电容、电阻等元器件集成为一颗芯片,压缩模块体积、缩短电气连接 距离,提升芯片系统整体功能性和灵活性。

1.3 先进封装的技术与形态根据需求不断迭代,多应用于高性能场景

先进封装的四要素是Bump、RDL、Wafer和TSV,具备四要素中任意一种技术即为先进 封装。1)Bump(金属凸点)技术,普遍应用于Flip-Chip(倒装焊)技术中,处于晶 圆之间互联的位置,起着电气互联和应力缓冲的作用,其发展趋势是使金属凸点越来 越小,直至发展为Hybrid Bonding(混合键合)技术,该技术制造的电介质表面光滑、 没有凸点,且具有更高的集成密度;2)RDL(重布线层)技术,用于X与Y平面电气延 伸和互联,适用于为I/O端口进行宽松排布,广泛应用于WLP(晶圆级封装)技术和 2.5D/3D技术中,但不适用于Flip-Chip技术;3)Wafer(晶圆)技术,可以用作芯片 的基底和WLP封装的载体,也可以与硅基板一同实现2.5D集成,技术发展趋势是使 Wafer面积逐渐增大;4)TSV(硅通孔)技术,用于Z轴电气互联,是实现多维立体结 构封装的关键技术。

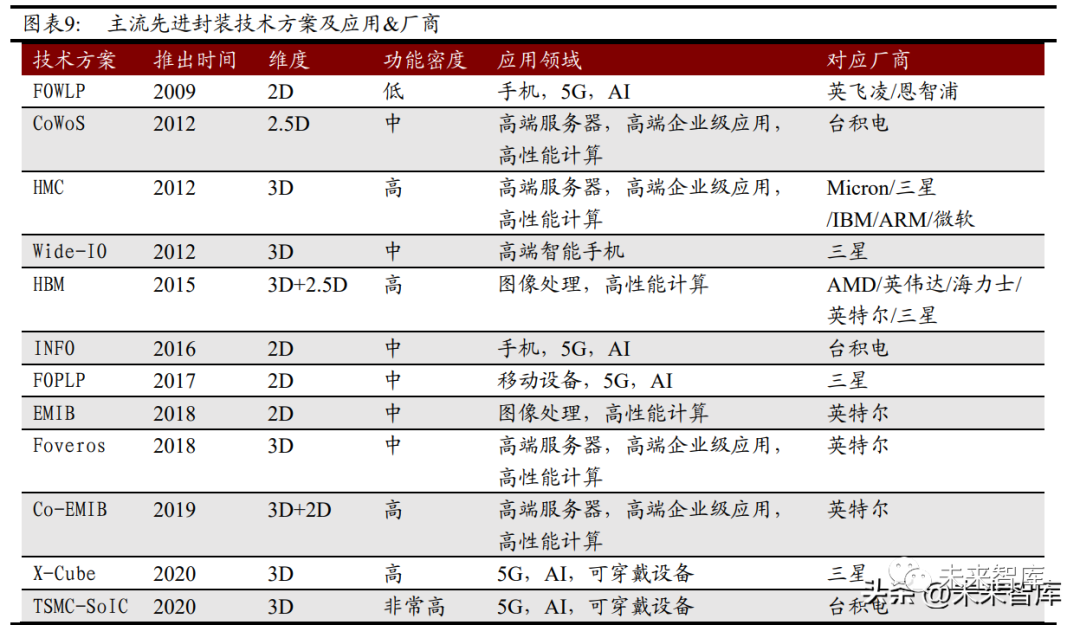

RDL和TSV使封装技术在X-Y-Z三维空间中具备延伸和发展的可能性。重布线层(RDL) 技术使得晶圆级封装得以在X-Y平面进行延伸,诞生了WLCSP、FOWLP、INFO、FOPLP、 EMIB等技术。基于硅通孔(TSV)技术,封装系统沿着Z轴进行延伸,实现了二维向三 维的拓展,出现了2.5D和3D集成,并演变出CoWoS、HBM、Co-EMIB、HMC、Wide-IO、 Foveros、SoIC、X-Cube等技术。

先进封装的技术与形态会根据应用侧需求不断变化与迭代。从WLP、SiP、2.5D/3D等 技术方案出发,各厂商根据应用侧需求进一步迭代出更深层的技术。以晶圆级封装 (WLP)技术为例,起初WLP技术采用Fan-in形态,随着引脚数要求增加,Fan-out形 态逐渐成为主流;而后出于提升系统性能的目标,台积电将多个芯片Fan-out工艺集 成起来,诞生了INFO技术;而从节省成本的角度出发,单个芯片的FOWLP技术又进一 步迭代出面板级封装技术(FOPLP)。

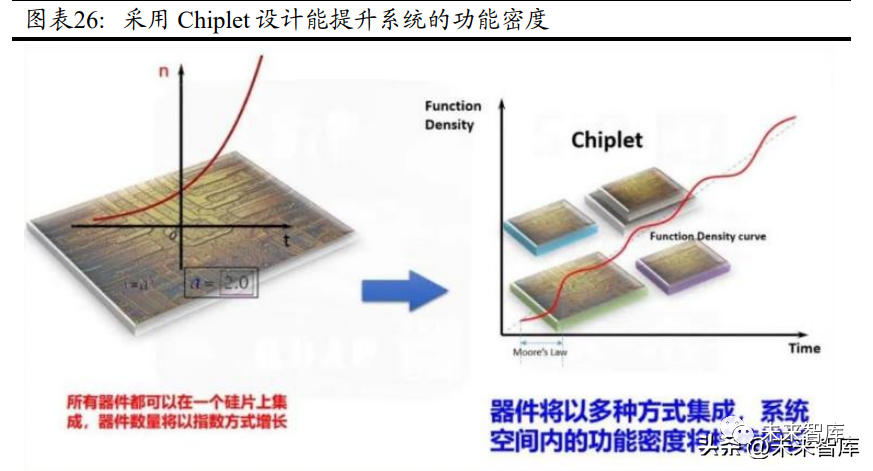

先进封装技术能提升系统的功能密度,多应用于高性能场景。目前主流的先进封装技 术主要由国际半导体龙头厂商研发,技术研发的维度从2D逐渐提升至2.5D和3D,系统 的功能密度也随之提升。同时,先进封装主要应用于高性能计算、高端服务器等领域, 因此产品技术壁垒与价值量相对传统封装会更高。

系统级封装(SiP)属于广义的先进封装,侧重于系统属性。SiP是指在封装内形成一 个系统,关注系统在封装内的实现,所以系统是其重点关注的对象,与之对应的是CSP (单芯片封装)。但SiP并不是先进封装特定的某种技术方案,因为SiP可能采用传统的Wire Bonding工艺,也可能采用先进封装的Flip Chip工艺。但随着系统对性能、 功耗、体积的要求越来越高,集成密度的需求也越来越高,SiP也会越来越多地采用 先进封装工艺。

Chiplet通过先进封装工艺实现。Chiplet也称为小芯片或芯粒,该技术通过将多个芯 片裸片(Die)通过内部互联技术集成在一个封装内,构成专用功能的异构芯片。通 过采用2.5D、3D等高级封装技术,Chiplet可实现多芯片之间的高速互联,提高芯片 系统的集成度,扩展其性能、功耗优化的空间。相对SoC系统级芯片的传统设计方法, Chiplet技术方案不需要购买IP或者自研生产,只需要购买已经实现好的小硅片进行 封装集成,且IP可以复用。所以Chiplet可以看成是一种硬核形式的IP,但它是以芯 片的形式提供的。

3D Chiplet是Chiplet进一步的发展。3D Chiplet是由AMD在2021年6月首先提出的, 通过3D TSV将Chiplet集成在一起,同时为了提高互联密度,采用了no Bump的垂直互 联结构。目前3D Chiplet产品是由台积电以SoIC的先进封装技术进行代工,主要应用 在3D V-Cache上,将包含有64MB L3 Cache的Chiplet以3D堆叠的形式与处理器封装 在一起。

2 先进封装市场空间广阔,为半导体设备行业带来增量

2.1 先进封装市场空间广阔,中国大陆先进封装产业蓬勃发展

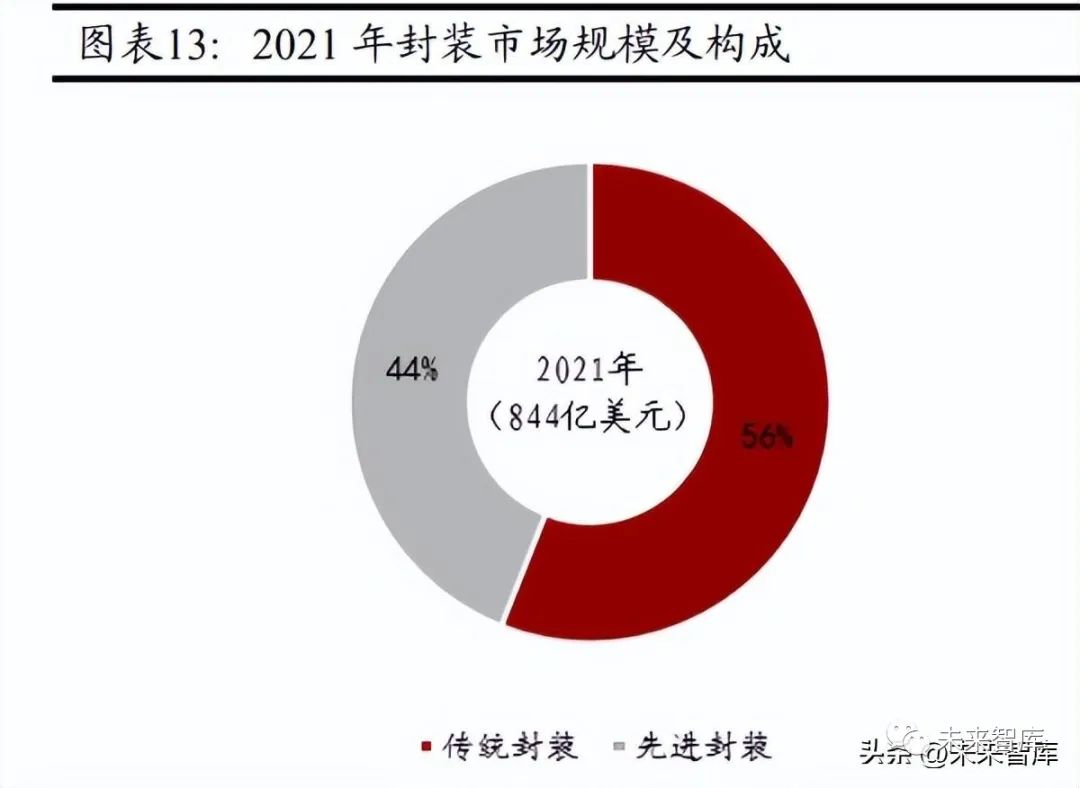

先进封装市场占比逐渐高于传统封装。据Yole数据,2021年全球封装市场总营收为 844亿美元,其中先进封装占比44%,市场规模达374亿美元。据Yole预测,2027年全 球封装市场规模为1221亿美元,其中先进封装市场规模为650亿美元,占比将提升至 53%。2021-2027年间先进封装市场规模的年化复合增速为9.6%,将为全球封测市场贡 献主要增量。

受益于国产替代加速及制造业的发展,中国大陆的先进封装市场蓬勃发展。根据 Frost&Sullivan统计,中国大陆2020年先进封装市场规模为351.3亿元,预计2025年 将增长至1,136.6亿元,2020-2025年间年化复合增速达26.47%,高于Yole对全球先进 封装市场年化复合增速9.6%的预测值。

倒装封装目前是先进封装行业营收规模最大的技术方案,嵌入式、3D堆叠和晶圆级扇 出型等高阶封装成长速度较快。根据互连技术的分类,目前倒装封装技术的营收规模 最大,其次是3D堆叠封装及晶圆级扇出型封装。许多普通规格的芯片产品均需要采用 倒装封装(Flip-chip)进行内部封装,因此目前倒装封装的市场规模最大。而晶圆 级封装(WLCSP)和嵌入式封装(ED)属于更高阶的封装技术,主要应用于高端芯片 封装,目前市场应用规模相对较小。但是从成长速度看,高阶封装技术如嵌入式封装、 3D堆叠、晶圆级扇出型封装是发展最快的三种方案,根据Yole的预测,2020-2026年 市场规模年化复合增速预计分别为25%、22%及15%。

2.2 先进封装为半导体设备行业带来增量

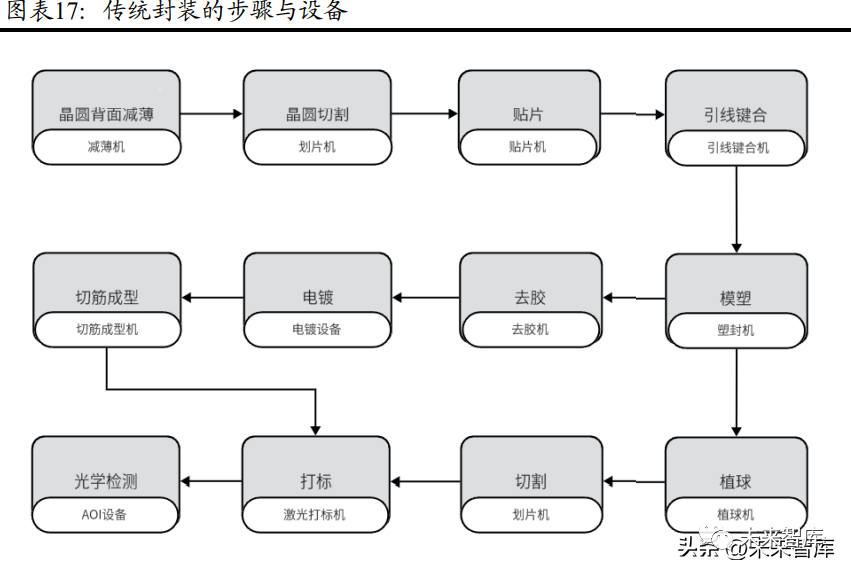

在先进封装工艺中,对传统封装设备的使用需求和精度要求都有所提升。传统封装测 试主要位于晶圆制造链的后道工序,包括减薄、切割、贴片、键合、打标、测试等步 骤,需要使用减薄机、划片机、贴片机、引线键合机、激光打标机等半导体设备。随 着先进封装的发展,在传统封装工艺的基础上也会有所改进,主要包括:(1)在先进 封装工艺中,芯片堆叠的层数增加,为了保持芯片体积较小,对减薄设备的精度提出更高要求;(2)在Chiplet设计中,制造小芯片需要更多的的切割和贴合,使得划片 机、贴片机的需求数量和精度要求都有所提升;同时Chiplet技术中每个裸片都需要 进行测试,且将小芯片集成后还需要进行系统性的测试,因而亦增加了测试设备的需 求。

在先进封装工艺中,除了传统封装设备,还需要使用晶圆制造前道工艺的设备。先进 封装使用的设备与晶圆制造的前道工艺开始有所重叠,而不只是传统封装所需要的 减薄机、划片机、贴片机等,刺激设备需求应封装技术发展而增长。在RDL、Bumping、 TSV等互连技术中,均需要使用涂胶机、***等设备;TSV技术需要钻孔,还增加了 刻蚀机的需求。此外对传统封装设备中的减薄机、划片机也需要进行一定改进,比如 将设备进一步设计为带凸点晶圆减薄机、带凸点晶圆划片机等,同时对厚度、划切道 宽度等均提出了更高的精度要求。

国内先进封装产业链所用设备有望部分实现国产替代。近年来国内半导体设备厂商 发展迅速,涌现了北方华创、中微半导体、沈阳拓荆、华海清科、精测电子等具备较 先进制程设备工艺实力的公司,对于先进封装所使用的刻蚀机、涂胶显影设备、清洗 设备、测试机等有望部分实现国产替代。

3 高性能计算驱动半导体产业发展,先进封装实现算力提升

3.1 HPC 超越手机成为半导体第一大需求驱动力,大算力时代来临

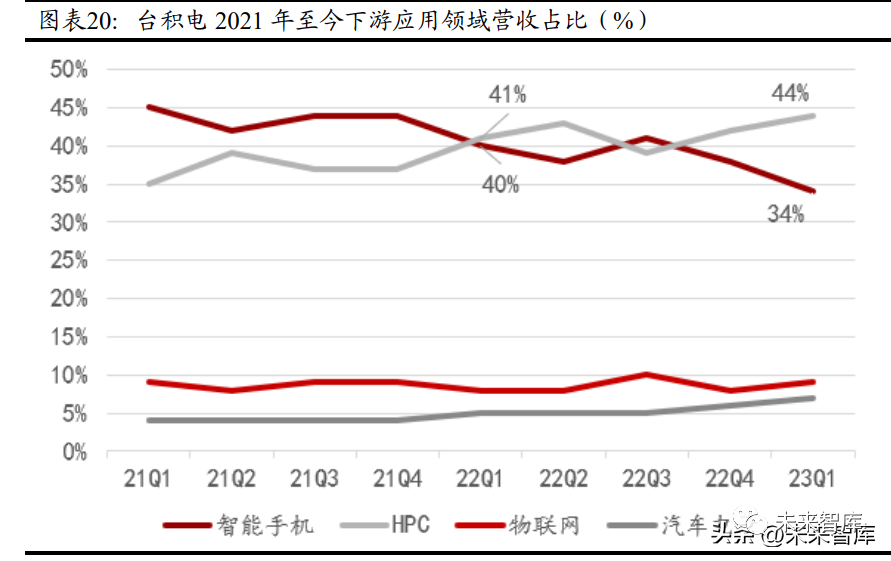

2022年Q1开始,HPC逐渐超越手机成为半导体第一大需求驱动力。5G手机渗透率逐渐 饱和,随着人工智能的发展,需要处理的数据量指数级增长,AI服务器、高性能计算 等算力需求迎来爆发式增长。从2022年Q1开始,在台积电下游应用领域的营收占比中, HPC(高性能计算)首次超越智能手机跃居第一,随后继续保持上升态势,而手机营 收占比逐渐下行。

智能算力规模快速增长,大算力时代来临。算力作为人工智能的要素之一,在数字经 济发展、产业智能化升级的进程中发挥巨大作用。根据IDC预测,到2026年,我国智 能算力规模将达到1271.4EFLOPS,2022-2026年化复合增长率达47.58%。

3.2 AI 服务器产业链迎来高景气,异构集成与异构计算共推算力发展

以AI服务器产业链为代表的硬件产品将充分受益于人工智能发展的浪潮。据 TrendForce集邦咨询预测,在AI+应用广泛落地的刺激下,AI服务器2023年出货量预 计将同比增长38.4%,2022-2026年AI服务器的年化复合增长率将达22%。

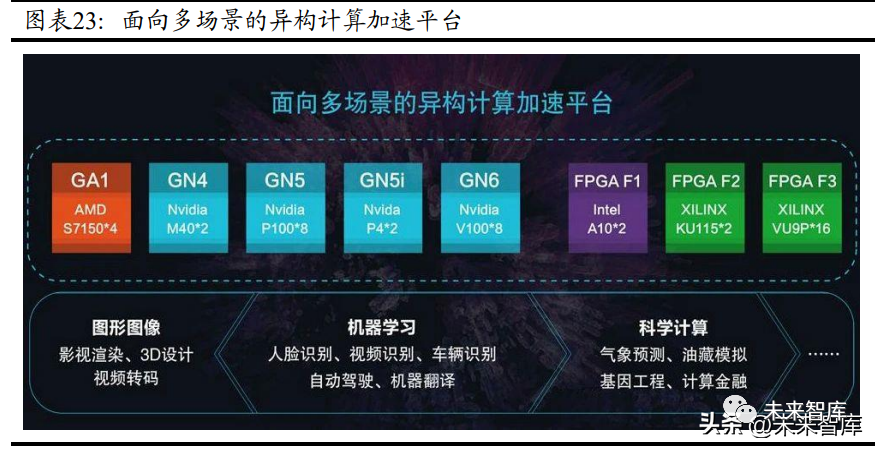

AI服务器采用的是异构计算架构。异构计算(Heterogeneous Computing),是指将 CPU、GPU、FPGA、DSP等不同架构的运算单元整合到一起进行并行计算。例如,CPU擅 长管理和调度,比如读取数据,管理文件,人机交互等;GPU管理弱,运算强,更适 合整块数据进行流处理的算法;FPGA实时性高,能管理能运算,但是开发周期长,复 杂算法开发难度大;DSP适合特定算法的计算等。异构计算的实现架构通常是CPU+ GPU/FPGA/DSP,主要由CPU完成不可加速部分的计算以及整个系统的控制调度,由 GPU/FPGA/DSP完成特定的任务和加速,具备计算能力强、可扩展性好、资源利用率高、 发展潜力大等优点。

异构集成通过先进封装工艺将多个高性能算力芯片集成在一个系统中,实现异构计 算以提升算力。异构集成(Heterogeneous Integration),准确的全称为异质异构集 成,异构代表采用的不同工艺节点,异质代表不同模块使用的半导体材料不同。异构 集成通过先进封装工艺将不同工艺节点、不同材质的高性能芯片集成在一起,使在单 个封装内构建复杂系统成为了可能,能够快速达到异构计算系统内的芯片所需要的 功耗、体积、性能的要求,从而使异构计算可以通过整合不同架构的运算单元来进行 并行计算,达到提升算力的目的。

在存算一体大算力领域,已有国内企业走在前列。存算一体架构将不同类型的处理器 和存储组件等集成到同一个芯片上,是异构集成的一种形式,目前在该领域已有国内 企业取得突破。2023年5月,后摩智能正式发布国内首款存算一体智驾芯片——鸿途 H30。该芯片仅用12nm工艺制程,其物理算力实现了高达256TOPS,在Int8全精度的计 算提供下,计算延时只有1.5ns,能效比为30-150 TOPS/W,比业界同等精度计算条件 下的水平提高了3倍以上。H30芯片采用的是后摩智能自研的AI处理器架构—IPU (Intelligence Processing Unit),将面向智能驾驶、通用人工智能等领域。与国 际巨头的某款智能驾驶8nm芯片相比,在Resnet50网络的条件下,后摩智能H30的性能 可以达到友商的2倍以上。

3.3 Chiplet 优势明显,是***“破局”路径之一

高性能计算的应用场景不断拓宽,对算力芯片性能提出更高要求,进而拉动了先进封 装及Chiplet工艺的需求。随着AI大模型数据处理需求的持续提升,对算力芯片性能 提出更高要求。Chiplet是高性能算力芯片的封装解决方案之一,其在设计、生产环 节均进行了效率优化,能有效降低成本并持续提高系统集成度。Chiplet需要采用先 进封装工艺中的异构集成技术进行实现,因而Chiplet的高增长亦将带动异构集成的 需求提升。根据Omdia预测,随着人工智能、高性能计算、5G等新兴应用领域需求渗 透,2035年全球Chiplet市场规模有望达到570亿美元,2018-2035年复合年均增长率 为30.16%,发展势头强劲。

与传统SoC相比,Chiplet在设计灵活度、良率等方面优势明显。相对单片集成技术SoC 而言,Chiplet是由不同工艺节点的模块共同组成,在相同的系统性能目标下,部分 模块对制程的要求有所降低,节省了部分开发时间;由于芯片面积越大越容易产生缺 陷,而Chiplet每个模块的载体都是较小的硅片,有效降低了生产中产生的缺陷数量;同时每个小硅片拥有单独的IP,并且可以重复使用,根据特定客户的独特需求定制产 品,节省开发时间。不同工艺生产制造的Chiplet可以通过SiP技术结合,典型的方案 就是XPU+DRAM,通过异构集成把内存和算力单元直接整合到一起,提升系统性能、突 破算力瓶颈。

针对先进制程,Chiplet更具成本优势。一方面小芯片形式的制造良率有所提升,另 一方面是Chiplet允许使用不同的制程制造异构芯片,例如高性能模块采用7nm,其他 模块只需要14nm或28nm就可以做到性能最大化,使系统整体的功能密度非常接近于 7nm的集成。AMD采用“7nm+14nm”的Chiplet设计方案,较7nm的单芯片集成的成本下 降了接近一半。AMD认为是否使用Chiplet设计思想的动机,在于性能、功耗与造价能 否妥协。Chiplet对成本下降的效果会随着核数(芯片核心的数量)的降低而边际减 小,因此未来可能会出现一个价格的均衡点来判断采用Chiplet技术是否更具有经济 效益。

中美科技摩擦加剧背景下国内先进制程发展受限,Chiplet是***“破局”路径 之一。近年来美国以《芯片与科学法案》、贸易管制“实体清单”及与日本、荷兰组 成芯片联盟等手段限制我国芯片先进制程的发展,使我国高端芯片领域面临“卡脖子” 问题。Chiplet降低了芯片设计的成本与门槛,且其IP复用的特性提高了设计的灵活 性,是***“破局”路径之一。2023年2月,北极雄芯发布了国内首款基于异构 Chiplet集成的智能处理芯片。该芯片采用12nm工艺生产,HUB Chiplet采用RISC-V CPU核心,可通过灵活搭载多个NPU Side Die提供8-20TOPS(INT8)稠密算力。该芯 片可用于AI推理、隐私计算、工业智能等不同场景,有效解决了下游客户在算法适配、 迭代周期、算力利用率、算力成本等各方面难以平衡的核心痛点。

4 龙头积极布局先进封装,中国大陆封装厂商蓬勃发展

4.1 晶圆厂和封测厂积极布局先进封装,侧重点各有不同

封测厂及晶圆厂龙头均积极布局先进封装。根据Yole数据,2021年各行业龙头在先进 封装行业的资本支出合计约为119亿美元。晶圆厂阵营方面,英特尔以35亿美元的资 本支出排名第一,主要用以支持Foveros和EMIB技术。台积电、三星以30.5亿美元和 15亿美元的资本支出分别排名第二、第四。而封测厂阵营方面,日月光以20亿美元的 资本支出排名第三,其是最大也是唯一能够与代工厂和集成设备制造商形成竞争的 OSAT。中国大陆封测厂长电科技和通富微电在先进封装资本支出方面则分居第6、7名。

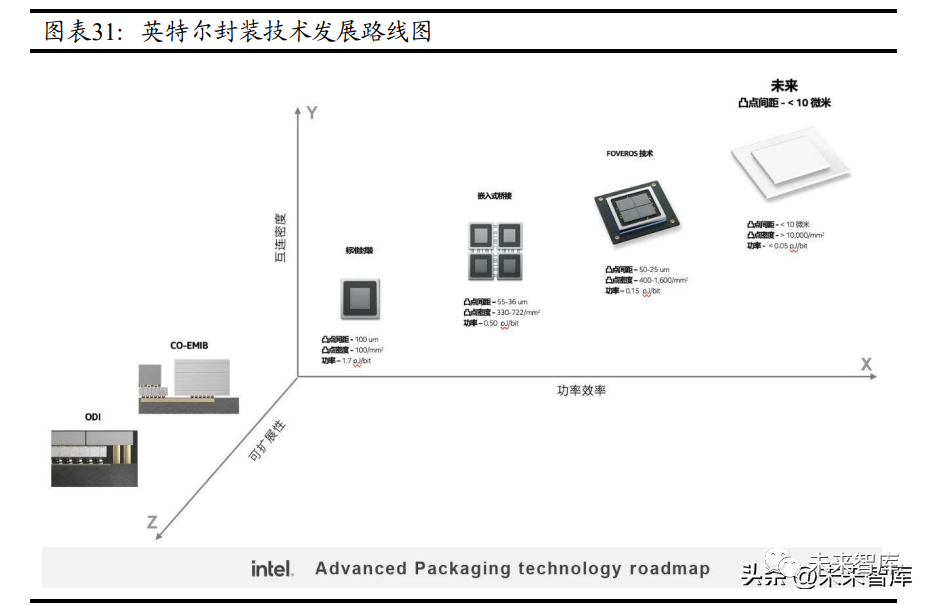

英特尔致力于实现每毫米立方体里功能最大。在英特尔的技术发展路线图中,先进封 装主要关注互连密度、功率效率和可扩展性三个方面。其中,Foveros和混合键合技 术主要关注功率效率、互连密度方面,而Co-emib和ODI技术则体现了集成的可扩展性 特点。从Foveros到混合键合技术,英特尔逐渐实现凸点间距越来越小,使系统拥有 更高的电流负载能力、更好的热性能。未来英特尔将继续致力于实现每毫米立方体里 功能最大。

台积电推出“3D Fabric”先进封装平台。台积电将2.5D和3D先进封装技术整合为“3D Fabric”平台,在2.5D层面推出了CoWoS及InFO等技术,在3D层面推出了3D SoIC技术。其中前段技术包含3D的整合芯片系统(SoIC InFO-3D),后端组装测试相关技术包含 2D/2.5D的整合型扇出(InFO)以及2.5D的CoWoS系列。目前最新的第五代CoWoS-S封 装技术,将增加3倍的中介层面积、8个HBM2e堆栈(容量高达128GB)、全新的硅通孔 (TSV)解决方案等,有望将晶体管数量翻至第3代封装解决方案的20倍。

日月光半导体推出“VIPack”先进封装平台,提供垂直互连整合封装解决方案。该平 台由六大核心封装技术组成,包括日月光基于高密度RDL的Fan Out Package-onPackage(FOPoP)、Fan Out Chip-on-Substrate(FOCoS)、Fan Out Chip-on-SubstrateBridge(FOCoS-Bridge)和Fan Out System-in-Package(FOSiP),以及基于硅通孔 (TSV)的2.5D/3D IC和Co-Packaged Optics。平台具备先进的RDL制程、嵌入式整合 以及2.5D/3D封装等技术,提供可优化时脉速度、频宽和电力传输的高度整合硅封装 解决方案所需的制程能力,能缩短共同设计时间、产品开发和上市时程。其中FOPoP 是由日月光在2023年3月14日发布的,该技术实现了电气路径减少3倍(降低延迟性)、 带宽密度提高8倍(提高带宽优势)的提升,主要应用于移动装置和网络通讯市场。

晶圆厂阵营及封测厂阵营关注侧重点各有不同。晶圆厂由于在前道环节的经验更丰 富,能更快掌握需要刻蚀等前道步骤的TSV技术,因而在2.5D/3D封装技术方面较为领 先,如英特尔的Foveros技术和台积电的CoWoS技术,均是高维集成的领先技术。而后 道封装厂商则更熟悉异质异构集成且封装技术布局全面,因此在SiP技术的发展方面 更有优势,比如日月光的“VIPack”平台中就将FOSiP等系统级封装技术列为核心技 术之一。在后摩尔时代,先进封装为封装行业带来核心增量,亦成为晶圆厂和封测厂 的兵家必争之地。我们预计未来晶圆制造厂的工艺程序将会演变成从制造到封装的 一体化工程,而OSAT则会呈现马太效应,技术迭代能力强、客户资源丰富的龙头企业 更具优势,市场份额有望更加集中。

4.2 OSAT 竞争格局较为稳定,中国大陆厂商蓬勃发展

OSAT竞争格局较为稳定,中国大陆封测厂营收名列前茅。根据2022年海内外已经上市 的封测厂(OSAT,Outsourced Semiconductor Assembly and Test)营收情况,OSAT 行业整体营收排名变化不大,竞争格局较为稳定。中国大陆封测厂中有长电科技、通 富微电、华天科技和甬矽电子进入前三十名的榜单,其中长电科技、通富微电和华天 科技稳居榜单前十。从毛利率和研发营收比来看,中国大陆封测厂的研发投入水平处 于国际领先水平,但毛利率与海外巨头相比仍有提升空间。

中国大陆封测厂蓬勃发展,以长电科技最为突出。在芯思想发布的委外封测前十大榜 单中,中国大陆市占率占比24.55%,仅次于中国台湾地区。在中国大陆封测厂中,长 电科技市占率占比44%,是国内封测行业的龙头企业。

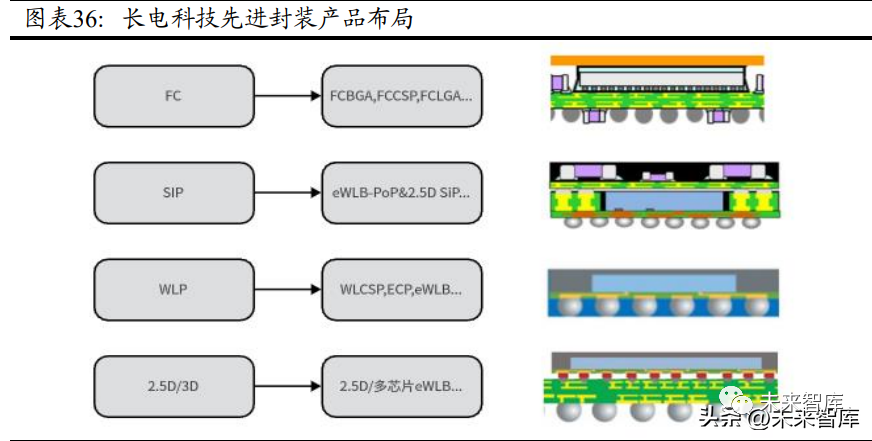

长电科技在国内封测厂中具有领先优势,先进封装技术布局全面且背靠中芯系。近年 来长电科技重点发展系统级、晶圆级和2.5D/3D等先进封装技术,提供的解决方案包 括扇入型晶圆级封装(FIWLP)、扇出型晶圆级封装(FOWLP)、集成无源器件(IPD)、硅通孔(TSV)、包封芯片封装(ECP)、射频识别(RFID)等。在SiP封装领域,长电科技拥 有双面塑形、EMI电磁屏蔽、激光辅助键合(LAB)等先进技术,具有电气性能更佳、 EMI屏蔽效果更好、可靠性更强等优势。此外,中芯国际为长电科技股东之一,双方 合作紧密,且中芯国际作为国内晶圆代工龙头,在需要前道工艺辅助的2.5D/3D封装 环节可以与长电科技协同合作,增强长电科技较其他封测厂的竞争优势。

通富微电聚焦算力芯片封测,与AMD深度合作。通富微电不断加强自主创新,并在多 个先进封装技术领域积极开展国内外专利布局,截至2022年12月31日累计国内外专 利申请达1,383件,其中发明专利占比约70%。公司在多芯片组件、集成扇出封装、 2.5D/3D等先进封装技术方面均有前瞻性布局,已能提供多样化的Chiplet封装解决方 案,且现已具备7nm、Chiplet封装技术规模量产能力。此外,通富微电是AMD最大的 封装测试供应商,占其订单总数的80%以上。未来随着和AMD的深入合作,通富微电将 持续深耕算力芯片封测领域,分享算力产业链加速发展的红利。

华天科技持续发力先进封装,推出3D-Matrix先进封装技术平台。华天科技为国内第 三大、全球第六大的封测厂,现已掌握了SiP、FC、TSV、Bumping、Fan-Out、WLP、 3D等集成电路先进封装技术。在Fan-Out领域,华天科技拥有完全自主知识产权的晶 圆级扇出型封装解决方案-eSiFO(embedded Silicon Fan-Out),可以提供8寸,12寸 晶圆级扇出封装的服务。此外公司实现了3D FO SiP 封装工艺平台的开发,现已具备 由TSV、eSiFo、3D SiP构成的最新先进封装技术平台——3D Matrix。未来华天科技 将持续加强技术创新工作,推进2.5D Interposer(RDL+Micro Bump)项目的研发, 布局UHDFO、FOPLP封装技术,加大在FCBGA、汽车电子等封装领域的技术拓展,提升 公司在先进封装领域的竞争力。

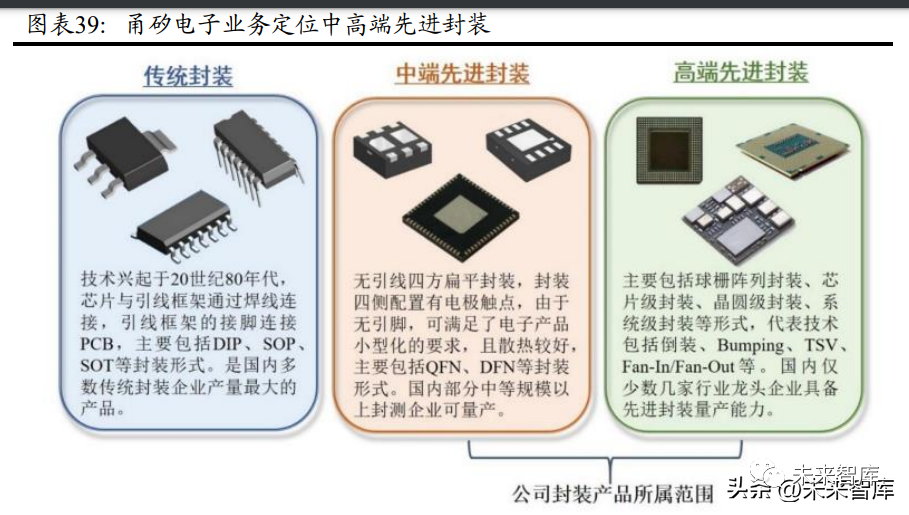

甬矽电子定位中高端先进封装,后起之秀蓬勃发展。甬矽电子于2017年11月设立,从 成立之初即聚焦集成电路封测业务中的先进封装领域,且坚持中高端先进封装业务 定位,车间洁净等级、生产设备、产线布局、工艺路线、技术研发、业务团队、客户 导入均以先进封装业务为导向。公司全部产品均为QFN/DFN、WB-LGA、WB-BGA、HybridBGA、FC-LGA等中高端先进封装形式,并在系统级封装(SiP)、高密度细间距凸点倒 装产品(FC类产品)、大尺寸/细间距扁平无引脚封装产品(QFN/DFN)等先进封装领 域具有较为突出的工艺优势和技术先进性。

晶方科技聚焦传感器封装,持续拓展差异化竞争优势。晶方科技是晶圆级硅通孔(TSV) 封装技术的领先者,具备8英寸、12英寸晶圆级芯片尺寸封装技术规模量产封装线, 涵盖晶圆级到芯片级的一站式综合封装服务能力。公司重点聚焦以影像传感芯片为 代表的智能传感器市场,封装的产品主要包括CIS芯片、TOF芯片、生物身份识别芯片、 MEMS芯片等,同时针对汽车电子应用领域的性能提升需求,大力推进车规STACK封装 工艺的开发创新,持续提升在车规CIS领域的技术领先优势与业务规模。

-

AI时代算力瓶颈如何破?先进封装成半导体行业竞争新高地2026-02-23 13892

-

大模型时代的算力需求2024-08-20 1112

-

【战疫专题】第二期:硬核战“疫”,机器人大有可为2020-02-25 12854

-

模块化UPS大有可为2009-07-06 830

-

角逐消费市场 MEMS传感器大有可为2013-08-08 2173

-

汽车电子控制系统大有可为2017-02-08 842

-

中国在可弯曲柔性屏领域将大有可为2019-08-11 1616

-

微内核是大势所趋,国产系统必将大有可为2019-08-21 5910

-

VR技术应用于医疗、教育等行业任重道远将大有可为2020-08-26 923

-

未来半导体行业将大有可为,激光焊锡机强势赋能赋智2020-10-18 2896

-

全球无刷电机行业发展现状 行业大有可为2022-07-12 4650

-

摄像机poe供电,PoE供电技术的大有可为2022-08-02 5736

-

助推汽车零配件行业高质量发展,机器视觉大有可为2022-08-17 2258

-

大算力浪潮下,国产先进封装技术取得了怎样的成绩?面临怎样的挑战?2024-07-22 6784

-

氢能源车加速放量,AEM制氢大有可为!2024-08-27 1268

全部0条评论

快来发表一下你的评论吧 !