时序分析基本概念介绍—Timing Arc

电子说

描述

今天我们要介绍的时序基本概念是 Timing arc ,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。如果两个pin之间在timing上存在因果关系,我们就把这种时序关系称为Timing arc,主要分为定义时序延迟,和定义时序检查两种。为啥叫它时序弧?因为时序图中经常用一条弧形线段来表示它。如下图所示:cell的timing arc定义在lib中,net之间没有timing arc, 它的delay则有RC参数计算而出。

时序延迟的Timing arc :有以下几种

Combinational Timing Arc

Edge Timing Arc

Preset and Clear Timing Arc

Three State Enable & Disable Timing Arc

时序检查的Timing arc :有以下几种

Setup Timing Arc

Hold Timing Arc

Recovery Timing Arc

Removal Timing Arc

Width Timing Arc

首先看 Combinational Timing Arc ,Combinational Timing Arc 是最基本的Timing Arc。Timing Arc 如果不特别指明的话,就是属于此类。如下图所示,定义了从特定输入到特定输出(A到Z)的延迟时间。

Combinational Timing Arc 的Sense有三种,分别是 inverting (或 negative unate), non-inverting (或 positive unate)以及 non-unate 。当Timing Arc 相关之特定输出(下图Z)信号变化方向和特定输入(下图A)信号变化方向相反(如输入由0变1,输出由1变0),则此Timing Arc 为inverting sense。

反之,输出输入信号变化方向一致的话,则此Timing Arc 为non-inverting sense。当特定输出无法由特定输入单独决定时,此Timing Arc 为non-unate。

其它的Timing Arc 说明如下。

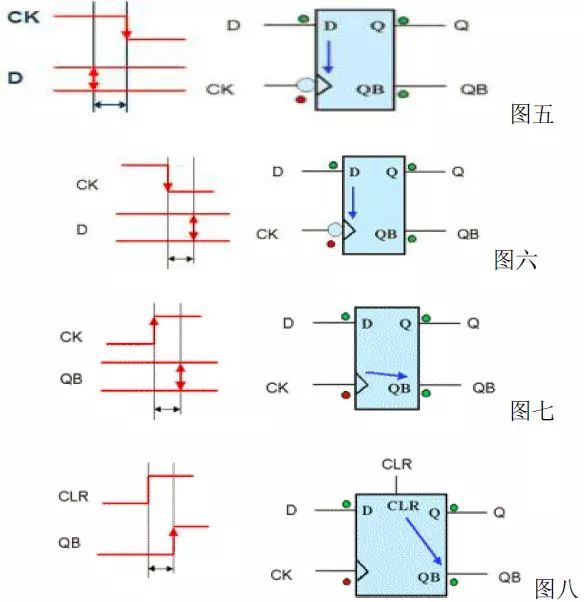

Setup Timing Arc :定义时序组件(Sequential Cell,如Flip-Flop、Latch 等)所需的Setup Time,依据Clock上升或下降分为2类(图五)。

Hold Timing Arc :定义时序组件所需的 Hold Time,依据Clock 上升或下降分为2类(图六)。

Edge Timing Arc :定义时序组件Clock Active Edge 到数据输出的延迟时间,依据Clock上升或下降分为2类(图七)。

Preset and Clear Timing Arc :定义时序组件清除信号(Preset或Clear发生后,数据被清除的速度,依据清除信号上升或下降及是Preset或Clear分为4类(图八)。这个Timing Arc 通常会被取消掉,因为它会造成信号路径产生回路,这对STA而言是不允许的。

Recovery Timing Arc :定义时序组件Clock Active Edge 之前,清除信号不准启动的时间,依据Clock上升或下降分为2类(图九)。

Removal Timing Arc :定义序向组件Clock Active Edge 之后,清除信号不准启动的时间,依据Clock上升或下降分为2类(图十)。

Three State Enable & Disable Timing Arc :定义 Tri-State 组件致能信号(Enable)到输出的延迟时间,依据Enable或Disable分为2类。(图十一)

Width Timing Arc :定义信号需维持稳定的最短时间,依据信号维持在0或1的位准分为2类。(图十二)

-

时序分析基本概念介绍<Virtual Clock>2023-07-07 2474

-

时序分析基本概念介绍<Skew>2023-07-05 5589

-

时序分析基本概念介绍<Latency>2023-07-04 4856

-

介绍时序分析的基本概念lookup table2023-07-03 2889

-

FPGA设计中时序分析的基本概念2022-03-18 4483

-

时序分析和时序约束的基本概念详细说明2021-01-08 1804

-

时序分析的基本概念ETM的详细介绍及如何应用的资料概述2018-09-24 19616

-

详细介绍时序基本概念Timing arc2018-01-02 26073

-

时序分析基本概念介绍——时序库Lib,除了这些你还想知道什么?2017-12-15 14020

全部0条评论

快来发表一下你的评论吧 !