探讨一下SDC的各种语法构成和整体结构

电子说

描述

引言

SDC是一个设计从RTL到netlist的桥梁,是FE/ME/BE都需要掌握的一项基本技能。通常情况来说,由前端工程师(designer)提供SDC文件是最合理的,因为只有designer才是最了解整个设计的结构的,所以最能够合情合理的提供出约束文件,但是,ME/BE又必须要能够看得懂,因为只有这样,在做综合和PR以及timing signoff的时候,在遇到问题时能够最快的定位timing问题的合理性。所以,接下来连续更新的文章,会从基础到深入,并结合实例的方式,跟大家一起探讨一下SDC的各种语法构成和整体结构,最终达成的目标就是每个人能够独立完整的提供合理的约束文件。

基础介绍

SDC全称是Synopsys Design Constraints Format,是由S公司最早提出的一种约束文件格式。主要用于指定design内部的Timing关系,约束Power消耗和Area大小。但是在这当中,最为关键的便是指定design的时序。其语法结构是基于TCL语法实现的。主要应用于综合、PR、以及STA过程当中,当然在其他方面也会有很大用途,比如CDC check。现在的SDC可以看做是一项标准的指令系统,基本上所有的EDA工具都可以兼容性识别。

tools行为简介

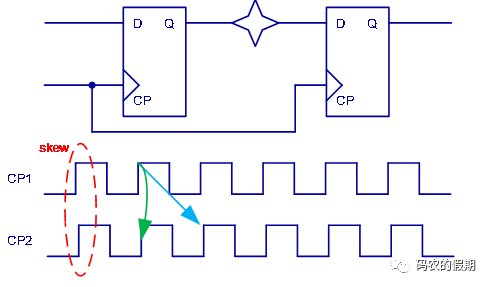

要想知道怎么约束一个design,我们首先需要清楚的知道,工具的行为是如何的。如图1所示,我们design通常情况下都是同步结构的设计,tools在做timing分析的时候,会将design中所有的path都抽象成这样前后两级DFF的结构。并将前一级的DFF作为source register,也称作launch register,将后一级的register作为destination register,也称作capture register。如果check setup,tools的默认行为是从launch DFF的当前触发沿到capture DFF的下一个触发沿之间的时间,如图中蓝色箭头所示。而check hold timing,tools的默认行为是从launch DFF的当前触发沿到capture DFF的当前触发沿之间的时间,如图中绿色箭头所示。

图1 design中的基本timing path

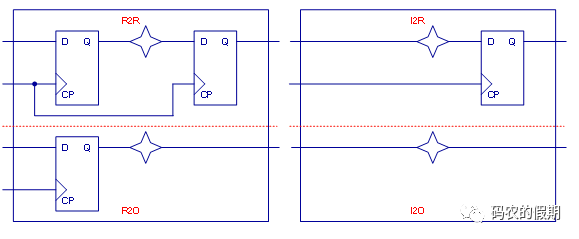

所以,要想让tools能够自动的check到design中的所有path的setup/hold。就需要保证design中所有的path都可以抽象成这种R2R的结构。而通常情况下,所有的design,在抽象之后,其timing path都可以抽象为图2中示例的四种结构,分别是R2R,R2O,I2R,I2O。那现在问题来了,图中的R2R的结构,是符合工具自动check timing的行为(当然,这里前提是clock定义好了);但是另外的三种结构,是不符合工具自动check timing的行为的。所以这就需要我们自己去构造出符合工具行为的path。

图2 design结构抽象

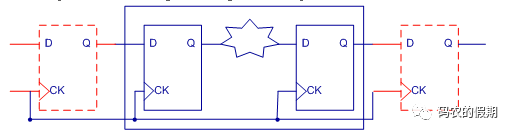

如图3所示,对于另外的三种path,我们需要做的就是在整个design的输入端、输出端分别虚拟一级DFF,如图中红色虚线register所示。这样,无论哪种结构(I2R/R2R/R2O/I2O),在工具看来都有了完整的launch DFF和capture DFF,从而就能够自动的完成timing check。

图3 timing path构造

我们虚拟构造前后级register的过程,其实就是我们SDC中,设置input delay、output delay的过程。

SDC构成分析

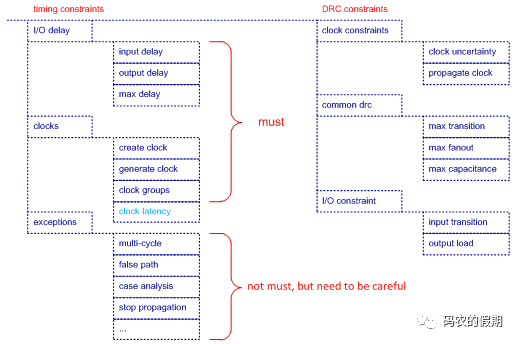

通过上面的分析,我们可以知道,对于一个design,我们需要设置input/output delay约束以构造前后两级虚拟register。当然,要设置input/output delay,我们首先需要完成clock的定义;除此之外,我们整个design当中还有很多path,我们不想让工具完全按照自己的行为去做timing分析,因此还需要设置一些timing exceptions;最后工具能够完成这种自动timing check的过程,还需要我们提供一些DRC相关的约束。因此,总结之后,整个SDC结构可以划分为两大类,如图4所示,其中一类是timing constraints,实现对design的timing约束;另一类是DRC constrains,实现对tools DRC方面的约束。当然,此划分也是按照我自己的理解来做的,不同的方面来看,可以做出不同种类的划分。

图4 SDC构成

图中timing constrains是最为关键的一部分,最好是由FE(即designer)提供,DRC constraints可以ME/BE或者timing signoff的相关人员,结合经验来提供具体约束。图中must部分,是每个SDC文件中基本上必须要有的,另外not must部分,通常情况下也是肯定存在的,并且这一部分约束通常会放松tools对timing的check,因此一定要谨慎…

-

SDC 2(100UM 厚 PTF 背板)材料清单及设计要点解析2026-05-14 263

-

探讨一下菊花链拓扑结构2023-06-15 23186

-

探讨一下深度学习在嵌入式设备上的应用2021-10-27 1974

-

探讨一下机械硬盘为啥那么容易坏掉2021-09-08 1836

-

了解一下Markdown的基本语法知识2021-08-04 958

-

电磁炉加热一下就停一下什么原因2021-06-04 42169

-

TVM整体结构,TVM代码的基本构成2021-01-07 3879

-

探讨一下关于贴片机在使用过程中会遇到的问题2020-11-25 2079

-

简单探讨一下关于电线电缆的结构材料的相关知识2020-09-10 1282

-

XDC时钟约束的三种基本语法2020-01-30 11254

-

双色非标模具模胚在整体结构方面具备的特点2019-07-22 1160

-

一起探讨一下这个可行?2016-05-30 3965

-

探讨一下,CRC校验的优势2014-06-11 6111

-

监控系统设备构成的分层次结构详析2009-12-18 2001

全部0条评论

快来发表一下你的评论吧 !