用于基准电压产生的启动电路设计

电子说

描述

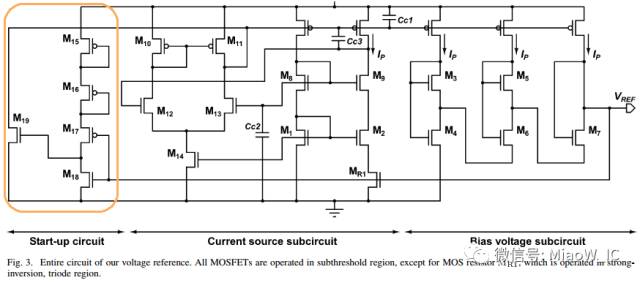

1.2009 A 300 nW, 15 ppm/ C, 20ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs

2. 2004 TOWARDS A SUB-1 V CMOSVOLTAGE REFERENCE

3. 2006us7148672 Low Voltage BANDGAP ReferenceCircuit with Startup Control

4. 2014 a low power CMOS voltage reference generator with temperature and process compensation

5. 2015 A wide temperature range voltage bandgap reference generator in 32nm CMOS technology

6. 2010 low voltage bandgap reference with output regulated current mirror in 90nm CMOS

这里在摘要部分说明了“小于1V带隙基准面临的问题”,However, these structures have outputvoltage errors due to a mismatchin the temperature dependency of the current in the output current mirrordevice and that of the BGR core, caused by the difference between the drain voltages of these devices . To reduceerrors, the output reference voltage is usually set close to theVBE of the BJT [4]. However, this is not a good solution because theoutput current mirror and output resistor forman open-loop configuration , so that accuracy relies on voltage and layout matching alone . In DSM CMOStechnologies such as 90 nm, the variability of devices becomes more severe andthe changes in temperature dependency of the MOS current caused by changes inthe drain voltage are much bigger than those which occur with long-channeltechnologies. This makes it difficult to obtain an output voltage with anacceptable temperature coefficient using the open-loop mirror structure.

7. 2010 NanoPower CMOS Voltage Reference with Temperature and Process Compensation

这篇文章以前学习过。

8. CN102385405 一种通用的带隙基准启动电路

下拉晶体管源极输出端即为启动电路的启动节点,该启动节点连接带隙基准电路的PMOS电流镜栅极,启动电路工作时将带隙基准电路中的PMOS电流镜栅极电平拉低,为三极管充电。用于启动带隙基准电路,使带隙基准电路脱离错误工作状态。

PMOS管412镜像带隙基准电路的工作电流,NMOS管411镜像由自由偏置电路41产生的比较基准电流,412与411漏极连接构成电流比较电路。当带隙基准电路处于错误兼并点时,412镜像的带隙基准电路支路电流小于411镜像的比较基准电流,由于两管电流应保持相等,因此,411管处于深线性区,VX电压接近地,下拉管413开启,将412栅极也即带隙基准电路PMOS电流镜组栅极电压拉低,为三极管充电,使带隙基准电路脱离错误兼并点,进入正确的工作状态;进入正确的工作状态后,412管镜像的带隙基准电路工作电流大于411管镜像的比较基准电流,因此为保证流过411管和412管的电流相等,412管进入深线性区,VX接近电源电压,此时下拉管413关断,启动电路不对正常工作的带隙基准电路构成影响。

流过409管的电流为比较基准电流,设为Icomp,Icomp满足下式关系:

当带隙基准电路工作在错误简并点时,最大支路电流产生于三极管202导通的临界状态,此时412管镜像的支路电流IDS,412为

由于NMOS电流镜411和PMOS电流镜412中流过的电流应保持相等,均为IDS,412,因此411工作在深线性区,VX~0。下拉晶体管413迅速将电流镜412管,PMOS管207管、208管和209管的栅极电压下拉,使得大电流充入带隙基准电路的支路,使三极管202和201导通,基准电路脱离错误简并点,其他错误简并点或零简并点时工作原理相同。当启动电路进入正确工作状态后,此时流过NMOS电流镜像管411管的电流为Icomp,而PMOS电流镜412管镜像的电流应为Inormal,由于

且411管和412管电流应保持相等,因此,412管进入深线性区,VX~VDD,下拉晶体管413关闭,启动电路不再对带隙基准电路产生影响。只要带隙基准电路进入错误简并点,启动电路即开始工作,直至带隙基准电路进入正确工作状态为止。

图6为电压模带隙基准电路,只存在一个错误简并点,即零简并点,此时比较基准电流需满足

本发明比较基准电流取值范围(上限值与下限值之差)为

它是一个正温度系数的PTAT电流,因此,为在所定温度-40~85范围内,实现比较基准电流都满足取值限定条件,偏置电流产生电路42产生的比较基准电流具有相同的或近似的正温度系数

图4的比较基准电流为

9. CN101644938A 低电压带隙基准源的安全启动电路

例如,在某工艺下,提供了5V和1.8V电压下的标准CMOS晶体管。而带隙基准源电路由于系统工作需要,要求工作电压在1.3V~5.5V。由于电路需要工作在5V电压下,因此必须使用5VCMOS晶体管。而在该CMOS工艺中,P型晶体管的阈值电压典型值为1.1V。N型晶体管的阈值电压典型值为0.8V。则在某些情况下,PMOS的阈值电压几乎要与电源电压相等了。这个时候,带隙基准源的主题电路和启动电路都要求非常严格才能保证在各种工艺下能够正常启动工作。

电流源电路要在vdd为1.3V正常工作,并保证BGR运放正常偏置。

BGR启动电路 ,P管M42相当于是电流产生源的镜像输出电流,当Ibias送入Q3和M30产生了启动电位Vstart,即M32的栅(源)电位,

当Vstart-VINN>Vth(M32),则M32会导通,则VINN将会被拉高,使Vstart-VINN

一般Ibias电流比Ibgr要小得多,并且可以改变Q3和Q0的个数来调节,使得正常工作的时候Vstart电压小于VINN。图2中的M32的衬底接地,可以利用晶体管的衬偏效应使得正常工作的时候M32的实际阈值电压略高于衬底和源极短接的同样尺寸的晶体管。因此,该电路既能保证主题电路的正常启动,又不会影响主题电路正常工作时的特性。

-

负电压是什么?它在电路中是怎么产生的?负电压产生的意义2024-03-27 14238

-

带隙基准电路设计原理2023-07-06 3865

-

LTC6258LT6656演示电路-适用于小电流启动基准的低噪声基准2021-06-02 877

-

基准电压源电路设计中遇到的挑战和要求是什么?2021-03-16 2447

-

基准电压源电路设计中遇到的挑战和要求2020-04-14 5214

-

一种高精度BiCMOS电流模带隙基准电路设计2019-07-12 3050

-

基于CMOS阈值电压的基准电路设计2012-10-10 6785

-

低压低功耗CMOS带隙电压基准及启动电路设计2010-04-13 921

-

如何选择最佳的电压基准源2010-01-08 1199

-

选择最佳的电压基准源2009-01-23 2388

全部0条评论

快来发表一下你的评论吧 !