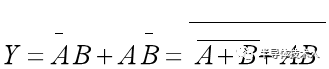

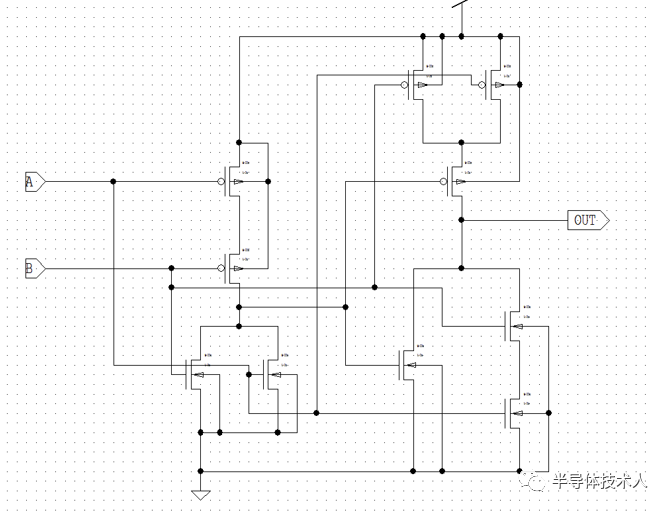

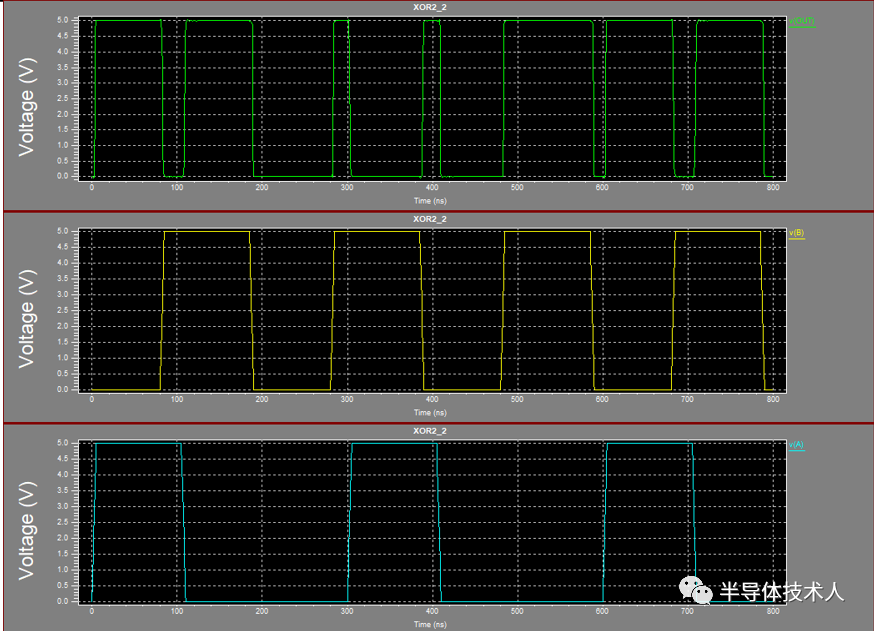

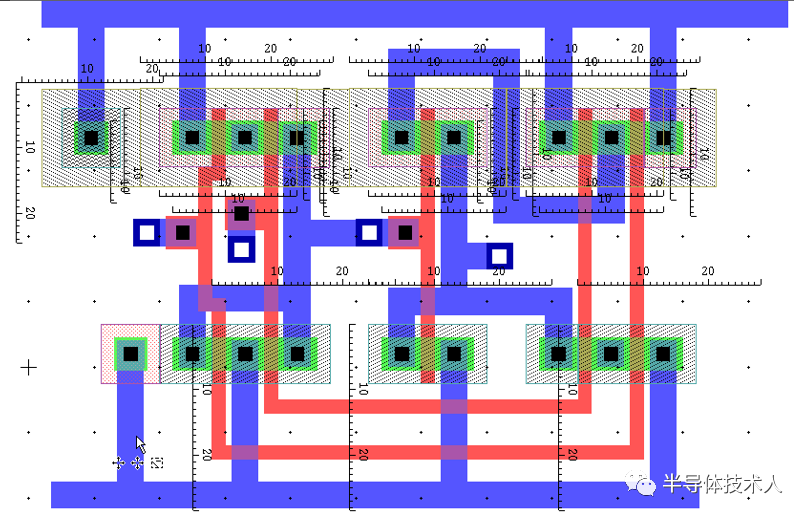

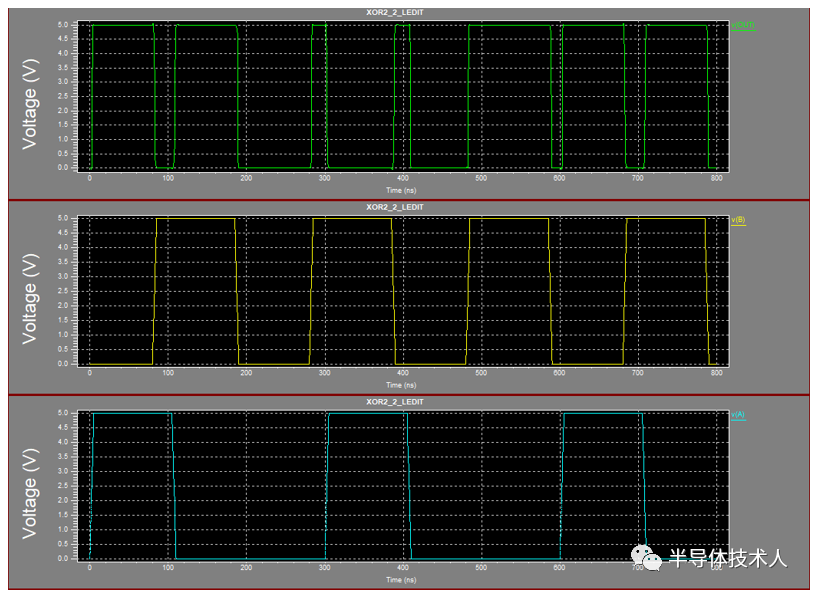

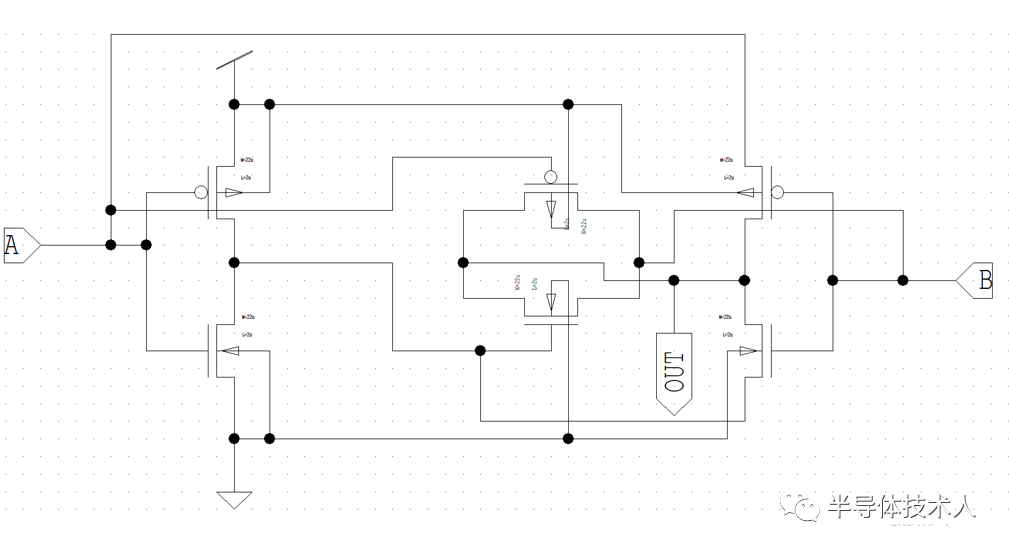

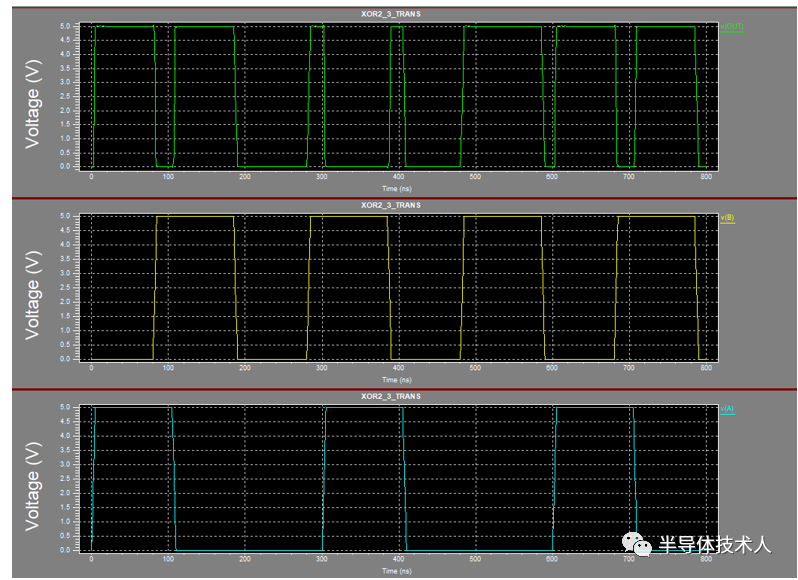

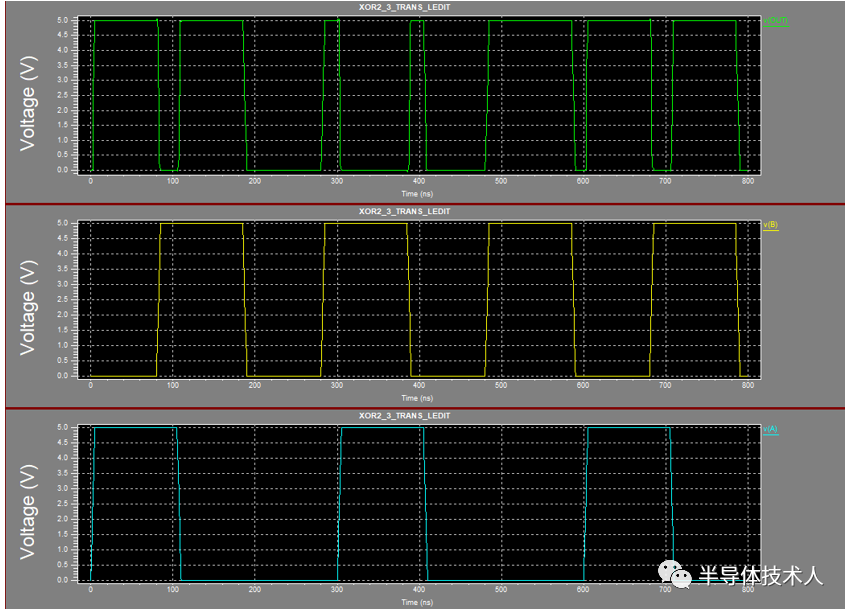

CMOS异或门仿真设计

电子说

1.4w人已加入

描述

异或门 (简称XOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个输出端,多输入异或门可由两输入异或门构成。若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。即如果两个输入不同,则异或门输出高电平1。

虽然异或不是开关代数的基本运算之一,但是在实际运用中相当普遍地使用分立的异或门。大多数开关技术不能直接实现异或功能,而是使用多个门组合设计。

##############################################

##############################################

随着超大规模集成电路的复杂程度不断提高,电路制造后的测试所需的时间和经济成本也不断增加。电路在设计时向电路添加一些特殊的结构(例如扫描链和内建自测试),能够大大方便之后的电路测试。这样的设计被即为可测试性设计,它们使电路更加复杂,但是却能凭借更简捷的测试降低整个项目的成本。

随着超大规模集成电路的集成度不断提高,同时市场竞争压力的不断增加,集成电路设计逐渐引入了可重用设计方法学。可重用设计方法学的主要意义在于,提供IP核(知识产权核)的供应商可以将一些已经预先完成的设计以商品的形式提供给设计方,后者可以将IP核作为一个完整的模块在自己的设计项目中使用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

低功率,1.8/2.5/3.3-V输入,3.3-V CMOS输出,2输入异或门数据表2024-05-09 366

-

异或门两种常见的实现方式2024-02-04 19117

-

为什么异或门又称可控反相器2023-09-12 11133

-

【数字电路】关于逻辑异或门基础知识点总结教程2021-01-23 13385

-

CMOS异或门的设计方法及技巧2020-11-10 41325

-

异或门逻辑测试的Multisim仿真实例电路图免费下载2020-09-23 2991

-

电路中用了四异或门74HC86D,但是异或门输出的信号有干扰?2018-01-03 9201

-

异或门的逻辑功能解析2017-11-19 73952

-

异或门2014-03-24 12105

-

异或门的应用电路图2010-09-14 8277

-

异或门,异或门是什么意思2010-03-08 16425

-

异或门符号,异或门逻辑符号2009-07-16 22744

-

TTL异或门电路2009-07-15 5691

-

异或门电路图2009-04-06 38948

全部0条评论

快来发表一下你的评论吧 !