一文了解i.MXRTxxx系列片内SRAM分区电源控制

描述

大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家介绍的是从功耗测试角度了解i.MXRTxxx系列片内SRAM分区电源控制。

我们知道配合 MCU 一起工作的存储器包含 ROM(Flash) 和 RAM 两类,前者主要放 RO 代码和数据,后者放 RW 数据。MCU 可以没有片内 ROM,但是一般都会包含片内 RAM,这个片内 RAM 功耗是 MCU 整体功耗的重要组成部分。

恩智浦 i.MXRT 四位数系列片内 RAM 主要由 FlexRAM 和 OCRAM 组成,痞子衡写过一篇文章 《FlexRAM模块详解》,里面介绍了 FlexRAM 的电源控制策略。虽然 FlexRAM 也是由多个 Bank 组成,但是其无法做到任意开关每个 Bank,其受既定的组合策略控制(跟随系统 Low Power 模式),而 OCRAM 则直接是整体开关。就这方面设计而言,i.MXRT 三位数系列片内 SRAM 电源控制则灵活得多,今天痞子衡就重点聊聊这个话题:

一、片内SRAM分区控制

恩智浦 i.MXRT 三位数系列目前主要是 RT500 和 RT600 两大型号,前者包含 5MB 片内 SRAM,后者包含 4.5MB 片内 SRAM。因为片内 RAM 够大,所以为其设计的电源控制策略就更精细。

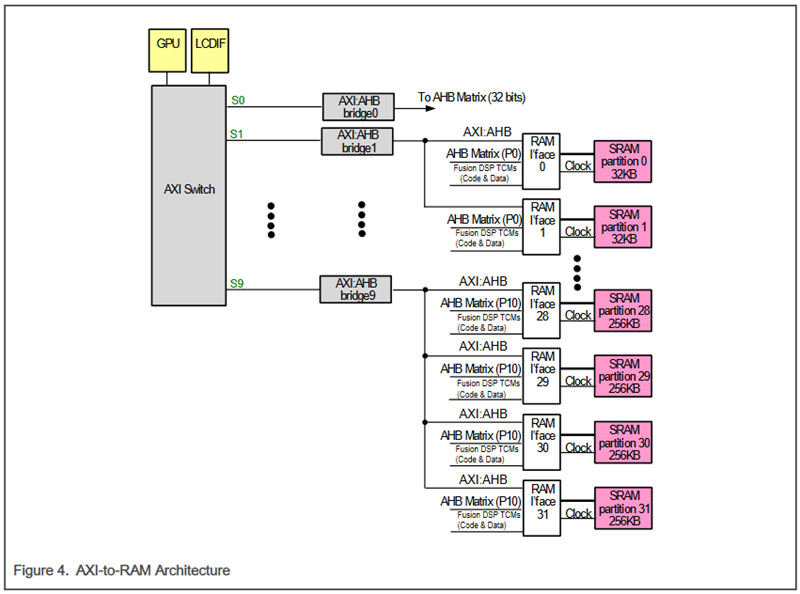

下图是 RT500 上 AXI-to-RAM 架构图,从图里我们知道 5MB SRAM 一共被分成了 32 块(注意不是等分,有 32KB/64KB/128KB/256KB 四种不同大小)。

- RT500 一共 32 个 SRAM 分区(SRAM0-31): - RT600 一共 30 个 SRAM 分区(SRAM0-29): - 不同大小的 SRAM 分区: SRAM0-7 :32KB SRAM8-11 :64KB SRAM12-15 :128KB SRAM16-31 :256KB

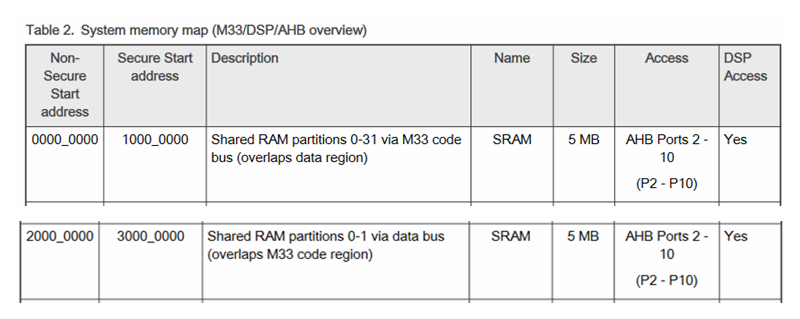

因为 RT500/600 都是基于 ARM Cortex-M33,所以片内 SRAM 在系统地址映射里有 Secure 和 Non-Secure 两个不同起始地址,再加上可以通过 Code 和 Data 两个不同总线去访问,所以应用里可以通过如下 4 个不同起始地址来访问到这同一块物理 SRAM。

这些 SRAM 分区除了大小不同之外,有一些还被赋予了特殊用途。比如 SRAM2,3 被 ROM API 征用了,如果应用里需要调用 ROM API,需要释放 SRAM2,3 使用权。SRAM0 则更特殊,它是唯一的一个软复位后依旧能保持内容的分区(其它分区复位后默认是Power down状态,不过上电 BootROM 执行时会将全部分区都打开)。

-(适用RT500/600)The SRAM2,3 region [0x10000-0x1BFFF] is reserved for ROM code. -(适用RT500/600)The SRAM0,3 region [0x0-0xFFFF], [0x1C000-0x1FFFF] are reserved for app-specific use cases. -(适用RT500/600)The SRAM4-11 region [0x20000-0x7FFFF] is reserved for Non-cached shared memory between M33 and DSP. -(适用RT500) The SRAM12-21 region [0x80000-0x27FFFF] is reserved for DSP code and data.

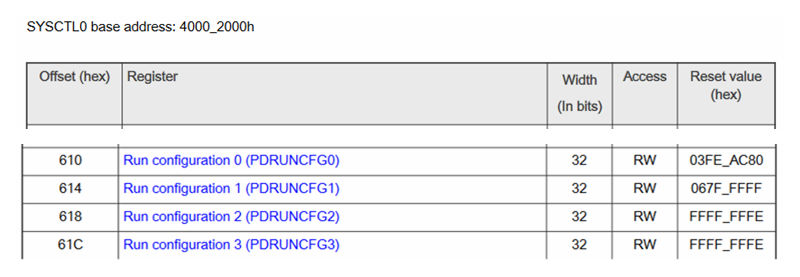

全部 SRAM 分区的电源开关在 SYSCTL0->PDRUNCFG2,3寄存器中,其中 PDRUNCFG2 控制的是 SRAM 各分区存储介质的电,PDRUNCFG3 控制的是 SRAM 各分区外围支持电路(线性驱动器、感测放大器)的电。如果我们想在保持 SRAM 中内容的情况下省电,可以仅操作 PDRUNCFG3 去关闭外围。

二、功耗测量方法

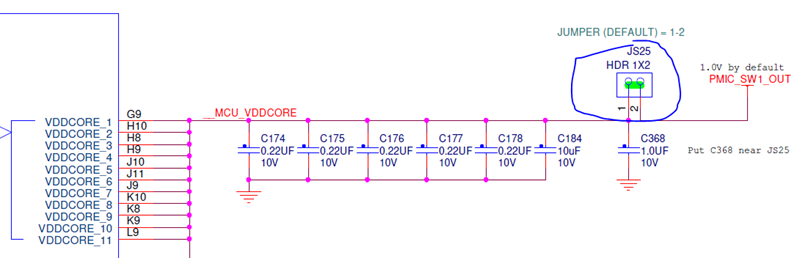

功耗测量最简单的办法就是找一个万用表,调节到电流测量模式,将其串到 VDDCORE 信号上,MIMXRT595-EVK (Rev.D3) 板卡特地设计了 JS25 接头,方便测量电流。

板子上电,应用程序加载执行后,便可以实时观测到运行时电流。不过电流测量有几个注意事项:

1. 不要挂载调试器在线运行时测量电流,会导致结果偏大。 2. 应用程序里如果有涉及模块电源开关代码,不要使能编译器优化等级,防止代码优化影响结果(电源开关有顺序要求)。 3. 如果是 CPU 高频运算相关代码,不同编译器下会导致结果不同,因为代码密度可能有差异。 4. 即使是单纯 while (1) 执行(可以在前面按需要加多个 NOP() 改变 while(1) 指令地址),指令地址不同也可能导致结果不同。

三、功耗测量结果

最后痞子衡在 MIMXRT595-EVK (Rev.D3) 板上借助 SDK_2_13_1_EVK-MIMXRT595oardsevkmimxrt595demo_appshello_worldiar 模板例程(debug Build,需要修改 main 函数以及相应修改链接文件),来测试代码在不同 SRAM 分区下执行的电流情况:

void sram_power_cfg(void)

{

PRINTF("CPU Frequency %d

", CLOCK_GetFreq(kCLOCK_CoreSysClk));

PRINTF("Main Clock %d

", CLOCK_GetFreq(kCLOCK_BusClk));

// 控制 SRAM 分区电源

SYSCTL0->PDRUNCFG2_SET = 0xFFFFFFFC;

SYSCTL0->PDRUNCFG3_SET = 0xFFFFFFFC;

PRINTF("PDRUNCFG 0x%x, 0x%x, 0x%x, 0x%x

", SYSCTL0->PDRUNCFG0, SYSCTL0->PDRUNCFG1, SYSCTL0->PDRUNCFG2, SYSCTL0->PDRUNCFG3);

}

int main(void)

{

BOARD_InitPins();

BOARD_BootClockRUN();

BOARD_InitDebugConsole();

sram_power_cfg();

// 增减 nop 指令数量来控制 while(1) 指令地址

asm("nop");

//asm("nop");

//asm("nop");

//asm("nop");

while (1)

{

}

}

最终测试结果如下,不同大小的 SRAM 分区功耗是有差异的,并且即使 SRAM 分区大小相同,功耗也可能有差异。此外 while(1) 指令地址不同导致的运行功耗差异也不小:

|

RO section in SRAMx RW section in SRAM0 |

SYSCTL0->PDRUNCFG2,3值 |

NOP数控制 while(1)指令地址 |

VDDCORE电流 |

|---|---|---|---|

| 1 | 0xFFFFFFFC | 0xbe50/0xbe52/0xbe58/oxbe5a | 29.39 - 30.52mA |

| 1 | 0xFFFFFFFC | 0xbe54/0xbe56/0xbe5c/oxbe5e | 32.55 - 33.86mA |

| 8 | 0xFFFFFEFE | 0x43e50/0x43e52/0x43e58/ox43e5a | ~30.4mA |

| 8 | 0xFFFFFEFE | 0x43e54/0x43e56/0x43e5c/ox43e5e | ~34.3mA |

| 12 | 0xFFFFEFFE | 0x83e50/0x83e52/0x83e58/ox83e5a | ~31.97mA |

| 12 | 0xFFFFEFFE | 0x83e54/0x83e56/0x83e5c/ox83e5e | ~37.03mA |

| 16 | 0xFFFEFFFE | 0x103e50/0x103e52/0x103e58/ox103e5a | ~31.45mA |

| 16 | 0xFFFEFFFE | 0x103e54/0x103e56/0x103e5c/ox103e5e | ~34.7mA |

| 30 | 0xBFFFFFFE | 0x483e50/0x483e52/0x483e58/ox483e5a | ~34.66mA |

| 30 | 0xBFFFFFFE | 0x483e54/0x483e56/0x483e5c/ox483e5e | ~42.2mA |

至此,从功耗测试角度了解i.MXRTxxx系列片内SRAM分区电源控制痞子衡便介绍完毕了,掌声在哪里~~~

审核编辑:汤梓红

-

68HC08系列单片机片内FLASH的在线写入方法2011-03-02 1281

-

Linux下使用片内SRAM有什么优点?2020-03-05 2567

-

一文了解LVGL的学习路线2021-12-07 3040

-

i.MX RTxxx系列MCU的OTP介绍2021-12-16 2086

-

i.MXRTxxx系列ROM中灵活的串行NOR Flash启动硬复位引脚选择2021-12-21 1544

-

如何在PS中调用Zynq内部的XADC模块进行片内温度和电源电压测量2021-12-27 2169

-

请教高手ARM不能和片外SRAM通信的原因2022-06-10 2080

-

请教一下大神在8051单片机片内RAM该如何分区呢?2023-05-09 1375

-

HPM6000系列微控制器的片上各类SRAM使用指南2023-06-01 795

-

请问AVR对片内SRAM的访问需要多久?2023-10-24 674

-

Linux下ColdFire片内SRAM的应用程序优化设计2010-02-05 857

-

i.MXRT系列的ROM API设计2020-10-30 1360

-

i.MXRTxxx系列与i.MXRT11xx系列双程序启动细节差异2022-05-06 3175

-

应用分享| HPM6000系列片上SRAM揭秘2022-09-19 3297

全部0条评论

快来发表一下你的评论吧 !