时序约束连载01~output delay约束

电子说

描述

本文将详细介绍输出延时(output delay)的概念、场景分类、约束参数获取方法以及约束方法。

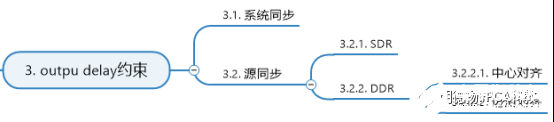

图1 output delay约束类型

如上图1所示:输出延时(output delay)约束与输入延时(input delay)约束相似,输出延时亦分成系统同步和源同步两大情形。

其中源同步根据时钟特性,又可以细分成SDR和DDR两种情况。根据数据和时钟的相位关系,DDR可以分成中心对齐和边沿两种。本文将详细讨论各种情况下的约束方法。

第1节 输出延时约束的目的

在详细讨论输出延时约束之前,明确为什么要做输出延时约束,通过该约束可以解决什么问题?

第2节 输出延时概念

设置输出延时的目标:让FPGA调整自身输出的时序,使输出的时序满足下游器件寄存器的建立时间和保持时间要求,来使得下游器件能够正确的捕获数据。

2.1 输出延时的max与min

2.1.1 max

max的意思是最大延时时间,用于考虑建立时间:一般为正数,表示数据在时钟采样沿之前就到达。

最大延时时间公式:最大板级延时+TSU。TSU为下游器件要求的建立时间。假如板级延时为0,则max就是下游器件的“TSU”。

2.1.2 min

min的意思为最小延时时间,用于考虑保持时间:一般为负数,表示数据在时钟采样沿之后还保持了一段时间 。

公式:最小板级延时-TH。TH为下游器件要求的保持时间。假如板级延时为0,min则是下游器件的“-Th”。

第3节 输出延时的两种测量方法

3.1 下游器件的参数(推荐)

第一种是根据下游器件的参数来设置建立时间和保持时间,通过下游器件的数据手册,可以得知下游器件寄存器的建立时间和保持时间的要求。在得知下游器件的建立时间和保持时间之后,就可以进行相应的设置,从而实现时序约束。

3.2 示波器测量

第二种方法是用示波器测量下游器件的一个输入端口,来得到它的时序信息。 比如说它的延时这种信息。但这种方法一般不常用。本书推荐使用第一种方法,因为第二种方法要求硬件做的比较规范,不能出现延时不断抖动的情况。

第4节 各应用场景下的约束方法

接下来讨论各种不同情况下输出接口的时序约束方式。

4.1 系统同步

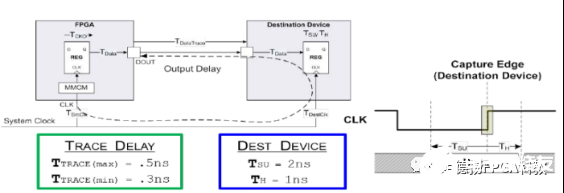

如图2所示,系统同步就是FPGA和下游器件共用一个时钟,可以认为这个时钟的延时等于零。但实际上,FPGA把数据送给下游器件,是有一定延时的。

一般下游器件的寄存器会有一个建立时间和保持时间参数。可以从数据手册中得到下游器件相应的参数,比如说它的建立时间是2ns,保持时间是1ns。而FPGA的延时可能符合一个抖动的情况,通过示波器测量或者计算方式可以得到FPGA的板级延时。比如说它的板级延时最大是0.5ns,板级延时最小是0.3ns。

图2 系统同步接口示意图

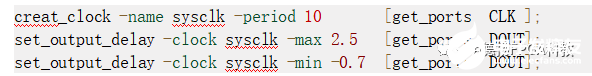

当测量得到板级延时之后,下一步便可以进行配置了。比如说最大的输出延时为最大的板级延时加上建立时间要求,即2ns+0.5ns=2.5ns。最小板级延时为输出最小延迟时间减去下游芯片寄存器保持时间,即0.3ns–1ns=-0.7ns。使用TCL语句实现以上约束的代码如下所示:

上面约束语句首先是通过creat_clock创建了一个生成时钟,输出给下游芯片作为时钟信号(需要注意该信号本身是存在的,只是通过创建生成时钟的方式告知quartus、vivado等综合软件该信号是时钟信号)。然后,set_output_delay –clock sysclk -max 2.5 [get_ports DOUT]的含义就是输出信号DOUT相对生成时钟sysclk的最大延迟是2.5ns。而set_output_delay –clock sysclk -min -0.7 [get_ports DOUT] 的含义就是输出信号DOUT相对生成时钟sysclk的最小延迟是-0.7ns。

这是系统同步的情况,系统同步就是FPGA和下游器件共用一个时钟信号。

4.2 源同步SDR

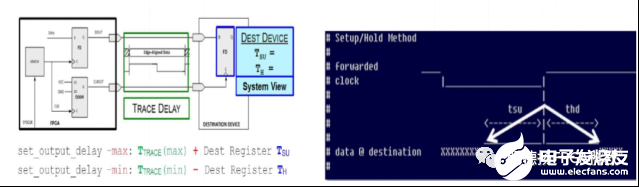

接下来看一下源同步,如图3所示,FPGA输出数据给下游器件同时,也会与数据同步输出一个时钟信号给下游器件,时钟和数据一起传输。其中分为SDR和DDR。SDR是指使用时钟上升沿去采样数据,DDR是指上升沿和下降沿都去采样数据。

图3 SDR传输示意图

上图3为典型的SDR传输示意图,SDR使用上升沿对数据进行采样。SDR的原理、方法与系统同步都是一样的,也是通过查数据手册得到下游器件寄存器的建立时间、保持时间。它保持的要求也能知道我的这个延时的抖动是多少啊。在测量之后得到最大抖动和最小抖动,就能根据公式计算出最大延迟时间和最小延迟时间。根据公式,最大延时时间是指板级传输延时最大值加上下游器件建立时间要求,而最小延迟是指板级传输延迟最小值减去下游器件保持时间。

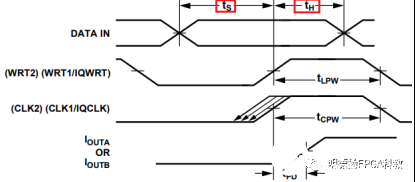

MP801开发板提供了两路高速DAC,AD9709时钟频率最高支持125MHz,输出也是符合SDR要求的,通过阅读手册获取该芯片寄存器的建立时间和保持时间。如下图4是AD9709芯片的接口时序图,CLK2是时钟信号,WRT2是类似写使能的信号,一般与时钟CLK保持一致即可,DATA IN是FPGA个AD9709芯片的八位数字信号,而IOUTA OR IOUTB是DAC芯片的两路模拟输出信号,与本次时序分析无关。建立时间是指数据必须在时钟上升沿之前到达的一段时间,所以下图中ts就是AD9709接口寄存器建立时间。保持时间是指数据必须在时钟上升沿之后保持的一段时间,所以下图中tH就是AD9709接口寄存器的保持时间。

图4 AD9709接口时序图

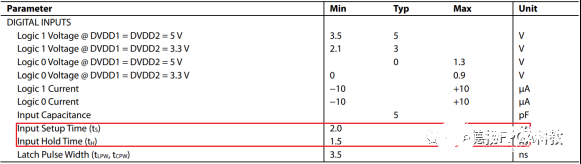

在根据芯片手册的数据表查的上图4中对应的时间,如下图5所示,tS的最小值为2.0ns,故建立时间为2.0ns,保持时间tH为1.5ns。能够对概念理解,不管是什么芯片都可以根据芯片手册的接口时序图得知接口寄存器的建立时间和保持时间,后续时序约束可以直接使用该参数。

图5 AD9709芯片时间参数

4.3 源同步-DDR(查手册方法)

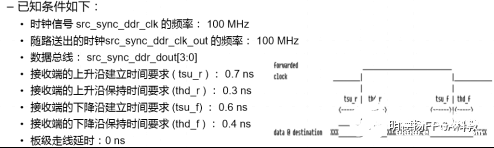

DDR其实就是SDRAM的升级版,为了提高数据传输效率,DDR在时钟的上升沿和下降沿都对数据采样。同样可以查手册得到接口寄存器的建立时间、保持时间,由于在时钟上升沿和下降沿都在采集数据,在这两个边沿都会存在建立时间和保持时间的要求,例如:

图6 DDR接口示意图

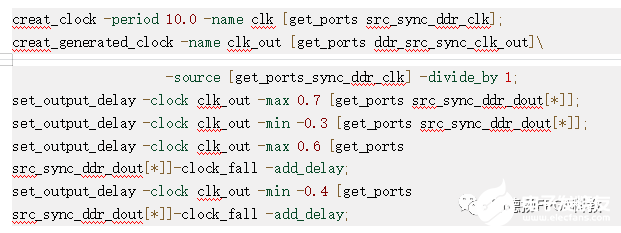

如上图6要求上升沿建立时间tsu_r为0.7ns,上升沿的保持时间thd_r为0.3ns,下降沿的建立时间tsu_f为0.6ns,下降沿的保持时间thd_f为0.4ns。进行IO约束之前,一般都会先约束一个生成时钟,目的在于告诉综合软件该接口信号以哪个时钟信号为标准,便于后续约束直接使用。根据理论知识,如果时钟线与数据信号线的PCB走线做了等长处理,那么源同步的最大延迟为下游器件的建立时间,最小延迟为0减去下游器件的保持时间。所以该DDR上升沿最大延迟0.7ns,最小延迟为0-0.3ns=0.3ns,下降沿最大延迟0.6ns,最小延迟是-0.4ns。上述约束转换成TCL代码如下所示:

注意这个clock_for下降沿的时候,要加上-add_delay。上面的六句约束中的前面两句时钟约束不是一定存在的,这两句与前面的时钟约束方式是一样的,后面四句set_output_delay用于约束输出接口信号所对应的最大和最小输出延迟,带有clock for的表示以时钟的下降沿作为参考点,从而完成对DDR输出接口信号的约束。

有的读者会注意到input delay 有个什么叫中心对齐的,为什么这里就没有了?因为 input delay 是靠测量的方式去得到的,而output delay是查数据手册的方式获得的数据。那么他的边缘这个点的时候,就不不可能会抖动。在下降沿的时候,在之前会稳定,稳定多久,之后会稳定多久,因此他一定是这么稳这样一个情况的啊,他会把这个实际参数要求给你啊,所以没有什么边缘对齐和中心对齐的情况。我们从查数据手册就会查到这几个参数,然后进行配置就可以了啊。还有一点就是对于我们的板级延时的一般情况下呢,如果我们硬件做的好的板,这件事是不需要考虑的。也就是说我们的output delay 一般呢就是设置它的鉴定时间啊,就是从手册里面得到它鉴定时间和保质时间这两个参数。然后根据它公式直接就是配置就可以了啊,所以它output delay 的方式相对比较简单。

第5节 总结与建议

根据经验,按照顺序去索引,找到对应的情况,按要求进行约束。比如说这个端口是属于上面三种情况中的哪一种,就按照那一种进行配置,进行约束就可以了。

input delay 、output delay就是告诉综合工具现在的实际情况。告诉综合软件FPGA下游器件的情况、要求是什么,综合软件得知这些参数后,结合自身的参数,在对设计进行布局、布线时就会去考虑满足下游器件的建立时间和保持时间要求。如果延迟时间过长,可以通过减小内部走线的延迟,或者采用更加接近芯片管脚的触发器去实现设计,减小输出延迟来达到目的。如果延迟过短导致下游器件保持时间不满足,综合软件可以通过增加走线延迟等增大输出延迟时间的方式满足下游器件保持时间的要求。总之,只要添加合理的约束,告知综合软件下游器件的延迟要求,综合软件就可以通过调节内部触发器的布局、走线来满足下游器件的建立时间和保持时间的要求,从而达到约束的目的。这就是 output delay 一个配置方式,相对比较简单。

审核编辑:汤梓红

-

set_output_delay的本质是什么?浅谈set_ouput_delay时序2023-08-12 3671

-

时序约束连载02~时序例外2023-07-11 1657

-

浅谈时序设计和时序约束2023-07-04 2749

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4562

-

创建输入输出接口时序约束的窍门2022-08-02 3678

-

FPGA的时序input delay约束2022-07-25 4058

-

详解FPGA的时序input delay约束2022-05-11 5209

-

FPGA设计之时序约束2022-03-18 2399

-

VIVADO时序约束及STA基础2022-03-11 11539

-

时序约束中如何精确找到匹配的template?2021-04-10 2950

-

FPGA时序约束分析余量2019-11-10 5442

-

FPGA时序约束方法2015-12-14 1022

-

时序约束用户指南2010-11-02 767

-

时序约束与时序分析 ppt教程2010-05-17 955

全部0条评论

快来发表一下你的评论吧 !