串行ADC布局布线设计要点

电子说

1.4w人已加入

描述

一、PCB布局设计注意要点:

①电源部分尽量远离AD与时钟部分。

②电源部分,主芯片FPGA,时钟部分尽量放同一面,AD部分放一面,这样既能减弱数字部分的信号对AD部分的干扰,又能方便结构统一做散热;(此设计点是限于板子空间小的情况下处理)。

③AD芯片与时钟芯片的LDO电源要靠近各供给模块芯片放置。

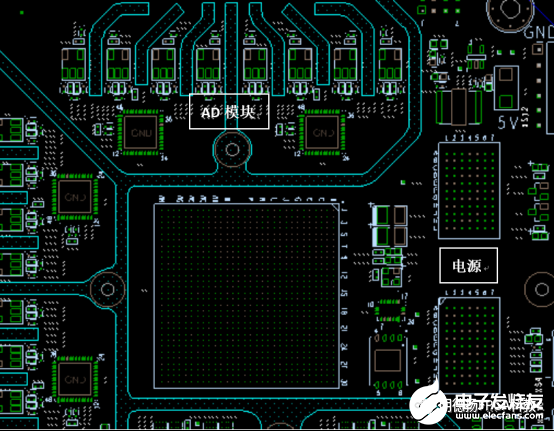

④AD模块之间间距尽量大,并且AD的多路输入端之间尽量留出空间做结构隔离条。

二、PCB布线设计注意要点:

①AD模块的输入端由单端50ohm经过变压器后转为差分100ohm这段模拟信号,单端阻抗要控制50ohm,差分阻抗要控制100ohm,走表层,路径尽量短。

②AD模块的数字部分的每1路数据信号由[AD*_D0---AD*_D*]组成,同层同组,以AD_DCO_CLK为参考进行等长匹配,等长公差控制在±50mil(如空间足够,公差可以尽量做小)。

③每个AD芯片的数字信号尽量做到等长,公差控制在±50mil,以保证多个AD模块同时使用时,数据信号同步。

④每个AD芯片的CLK时钟信号到时钟芯片的长度要等长,走差分对,控制100ohm阻抗,单对差分内等长公差控制在±5mil,差分对之间等长公差控制在±10mil。

⑤ADC_SYNC信号要走T型走线,到每个AD芯片上的长度要等长匹配。

本文转载自: 明德扬FPGA科教微信公众号

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入探讨PCB布局布线的专业设计要点与常见挑战2026-01-04 397

-

SAR ADC如何做好布线布局?2024-12-17 484

-

干货!电源设计器件布局和布线要点2023-10-18 1498

-

PCB布局布线设计要点2023-09-19 948

-

简述无源/有源晶振的布局布线要点2023-08-15 21418

-

电源设计器件布局和布线要点2022-11-10 2174

-

电源PCB布局、布线、调试要点及注意事项2022-01-06 2462

-

电源PCB布局、布线、调试要点及注意事项相关资料分享2021-12-28 2462

-

高速ADC设计中的PCB布局布线技巧有哪些?2021-04-21 1536

-

AN-1142: 高速ADC PCB布局布线技巧2021-03-20 1509

-

PCB规划/布局和布线的设计技巧和要点2021-01-22 2809

-

SAR ADC PCB布局布线的参考路径2018-09-12 2282

全部0条评论

快来发表一下你的评论吧 !