Xilinx Zynq7035 PL SFP光口通信例程

电子说

描述

(基于TI KeyStone架构C6000系列TMS320C6657双核C66x 定点/浮点DSP以及Xilinx Zynq-7000系列SoC处理器XC7Z035-2FFG676I设计的异构多核评估板,由核心板与评估底板组成。)

ZYNQ7035 PL SFP光口通信例程

1.1.1 例程位置

ZYNQ例程保存在资料盘中的DemoZYNQPLaurora_8b10b_0_ex文件夹下。

1.1.2 功能简介

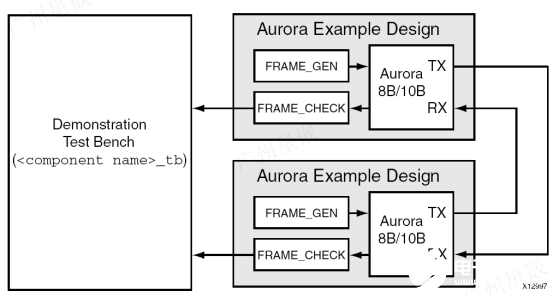

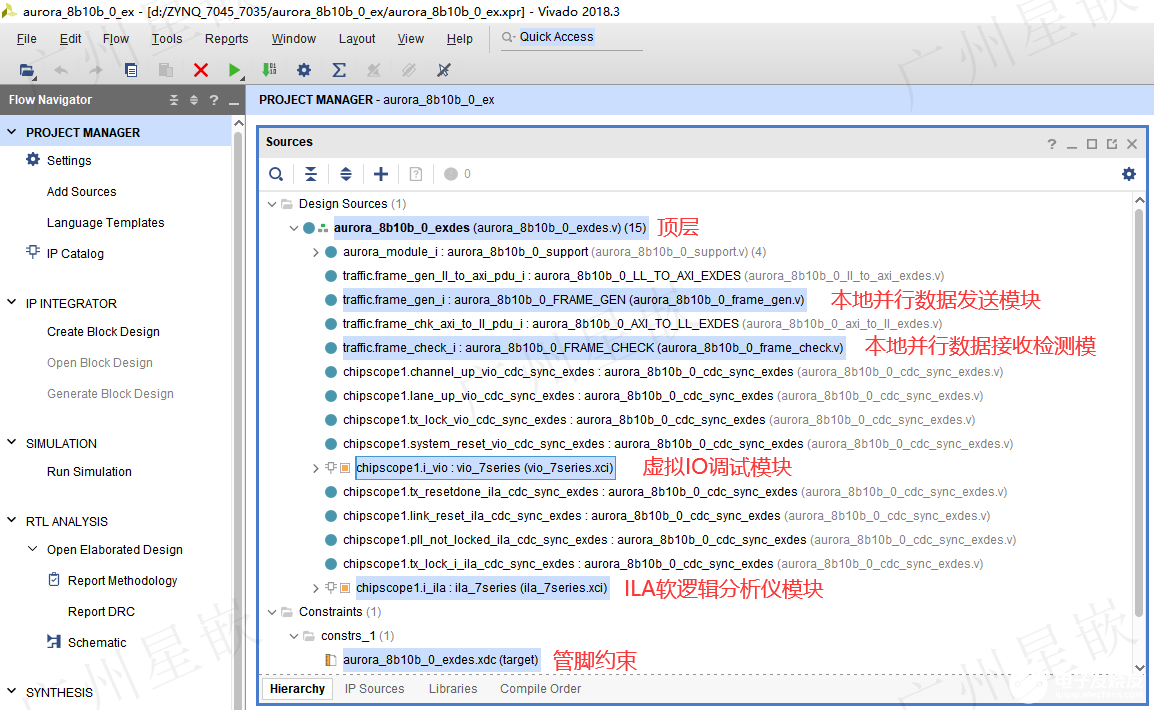

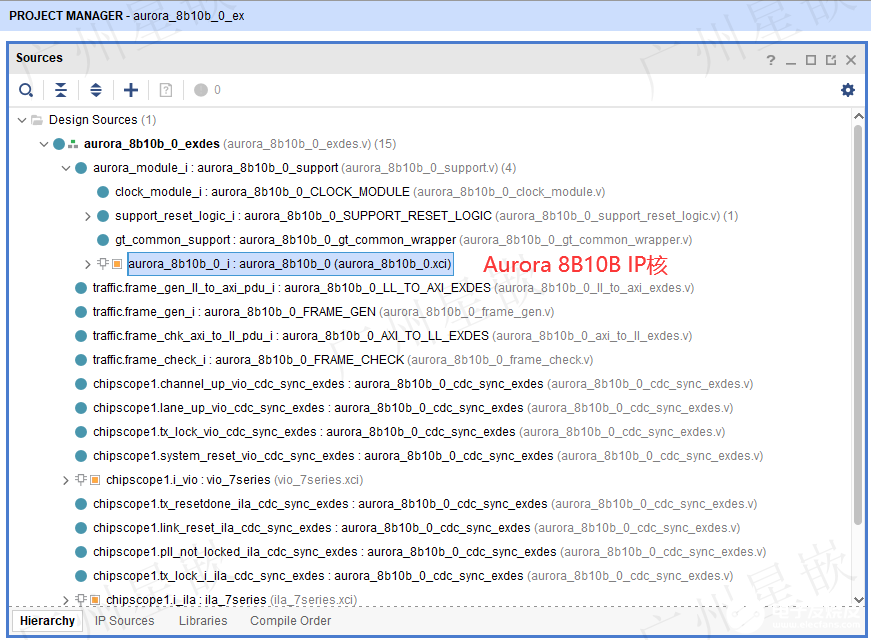

使用Aurora 8B/10B IP核生成后带的例子工程,稍作修改。

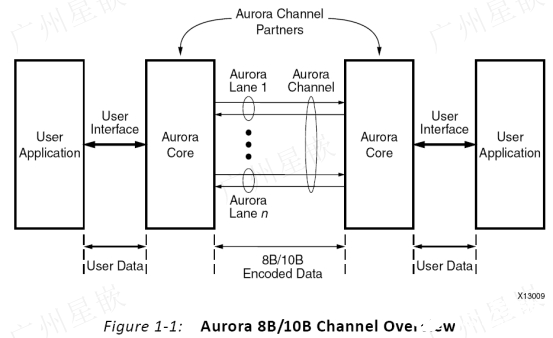

图 Aurora 8B/10B例子工程

FRAME_GEN: 本地并行数据发送模块

功能:本地产生GTX并行发送数据

接口说明:

// User Interface

output [0:15] TX_D; //发送数据

output TX_REM; //最后一个16bits数据的高低字节有效标识,0表示,表示TX_D[0:7]有效;1表示TX_D[0:15]有效。

output TX_SOF_N; //发送开始标识,低电平有效

output TX_EOF_N; //发送结束标识,低电平有效

output TX_SRC_RDY_N; //发送数据源端准备好标志,低有效

input TX_DST_RDY_N; //发送数据目的端准备好标,为0时才允许发送数据

// System Interface

input USER_CLK;//用户时钟,由Aurora IP核提供,数据发送模块用此时钟作为同步时钟

input RESET;//复位,高有效

input CHANNEL_UP;//GTX通道初始化完成标志,为1时表示完成

数据发送模块只有在RESET=0、CHANNEL_UP=1和TX_DST_RDY_N=0时,才允许发送数据。

FRAME_CHECK: 本地并行数据接收检测模块

功能:本地接收GTX并行数据,并检测数据是否存在误码

接口说明:

// User Interface

input [0:15] RX_D; //接收数据

output RX_REM; //最后一个16bits数据的高低字节有效标识,0表示,表示RX_D[0:7]有效;1表示RX_D[0:15]有效。

output RX_SOF_N; //接收开始标识,低电平有效

output RX_EOF_N; //接收结束标识,低电平有效

input RX_SRC_RDY_N; //接收数据有效,低电平有效

// System Interface

input USER_CLK; //用户时钟,由Aurora IP核提供,数据发送模块用此时钟作为同步时钟

input RESET; //复位,高有效

input CHANNEL_UP; //GTX通道初始化完成标志,为1时表示完成

output [0:7] ERR_COUNT; //接收数据错误个数

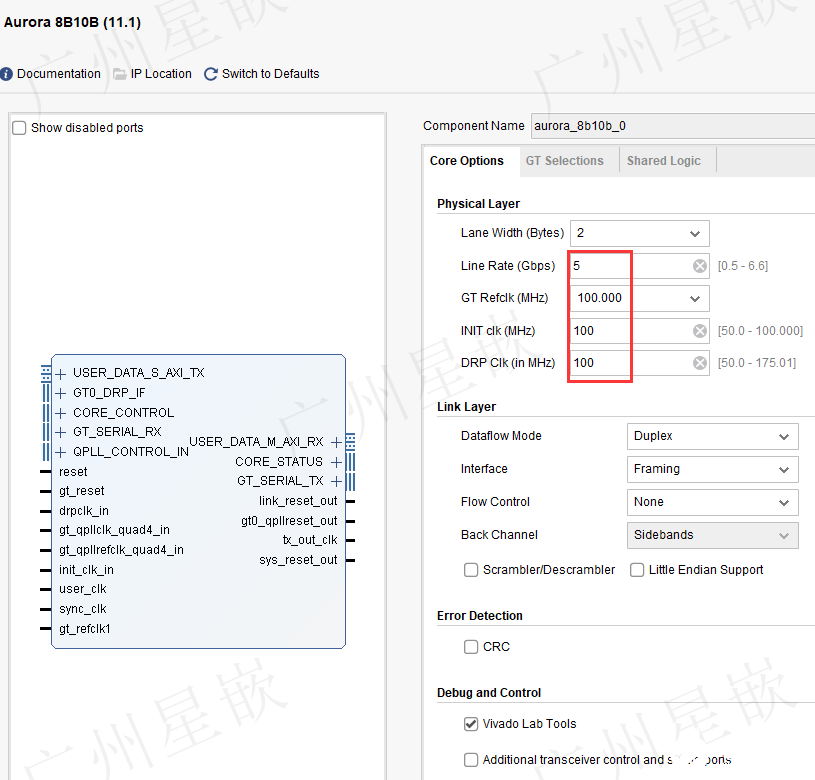

Aurora 8B10B IP核参数设置如下图所示:

Aurora 8B10B IP核显示最高只支持6.6Gbps,这里我们将线速率设置为5Gbps,参考时钟设置为100MHz。

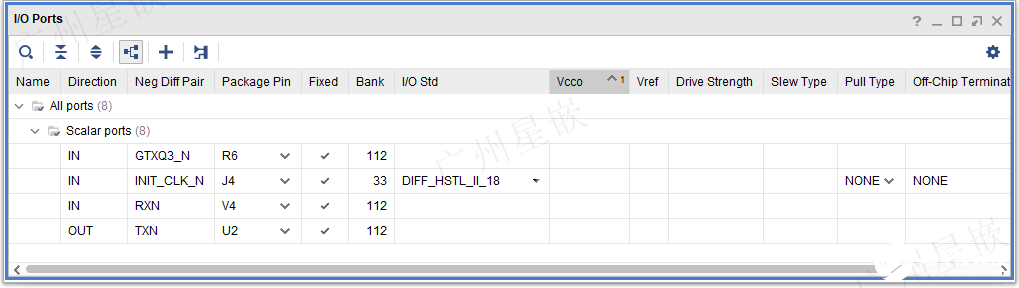

1.1.3 管脚约束

ZYNQ PL工程管脚约束如下图所示:

1.1.4 例程使用

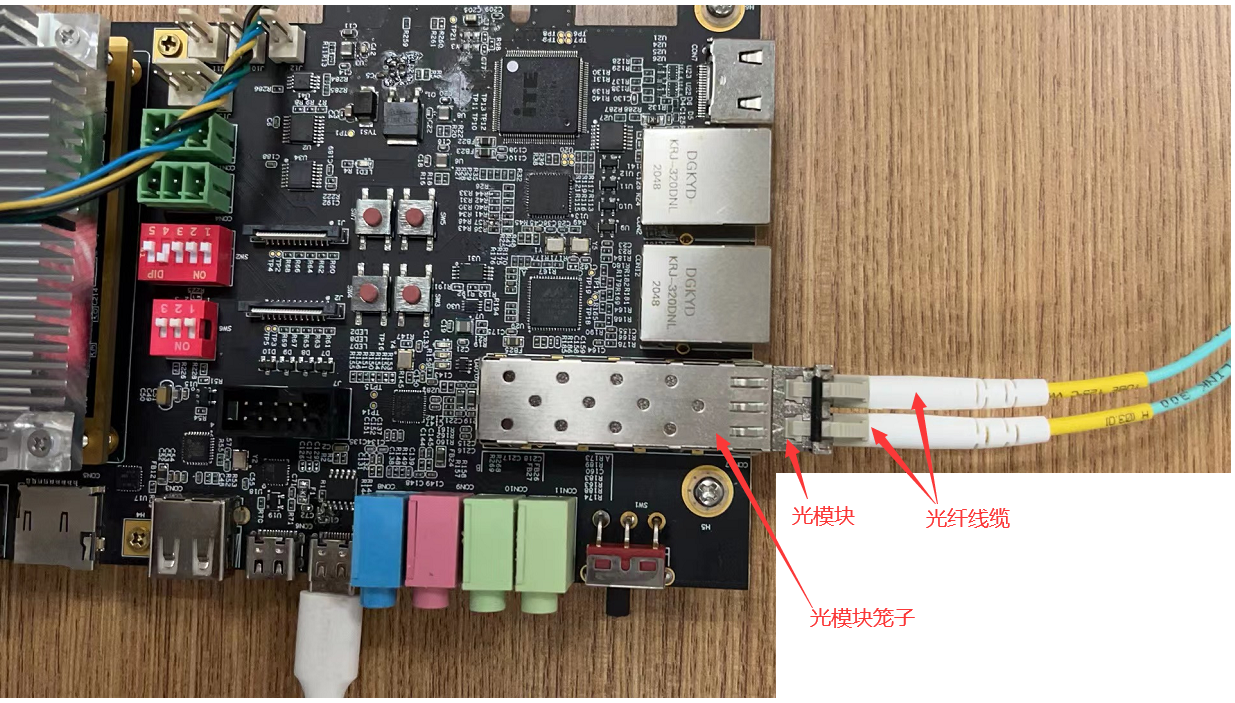

1.1.4.1 连接光纤模块

将光模块插入光模块笼子,并使用光纤线缆将光模块的收、发端口自环对接:

1.1.4.2 加载运行ZYNQ程序

1.1.4.2.1 打开Vivado工程

打开Vivado示例工程:

工程打开后界面及工程主要模块说明如下图所示:

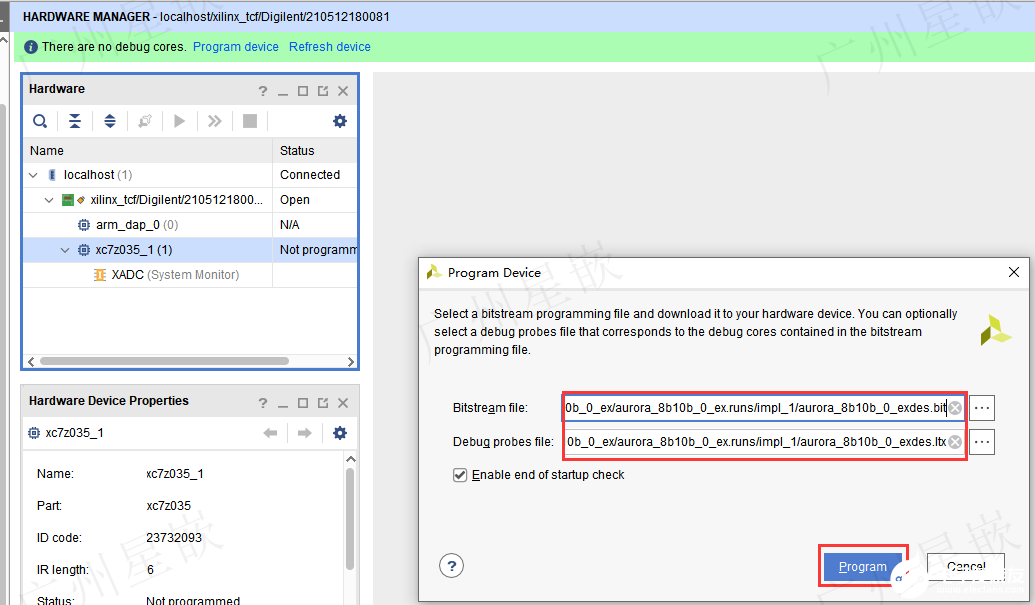

1.1.4.2.2 下载ZYNQ PL程序

下载bit流文件aurora_8b10b_0_exdes.bit,并且配套aurora_8b10b_0_exdes.ltx调试文件,如下图下载界面所示:

1.1.4.3 运行结果说明

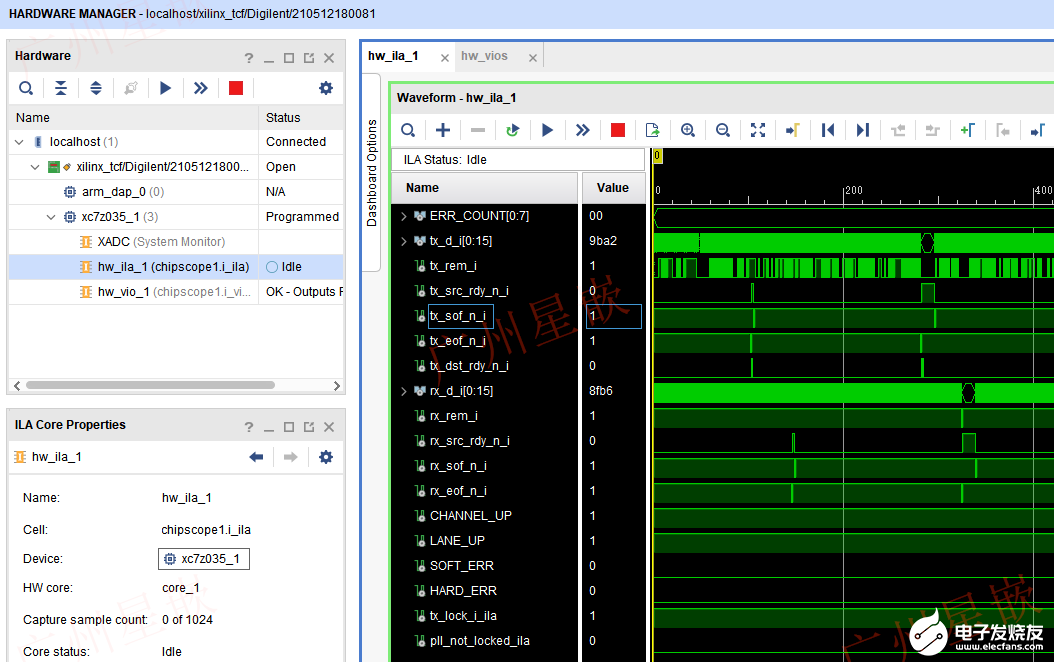

ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集GTX收发本地并行信号以及错误检测信号的时序波形。

ILA抓取波形如下图所示:

ILA抓取信号说明如下:

ERR_COUNT[0:7]:接收数据错误个数,接收模块分析接收数据是否正确;

tx_d_i[0:15]:发送数据;

tx_rem_i:最后一个发送数据的高低字节有效标识,0表示,表示tx_d_i[0:7]有效,1表示tx_d_i[0:15]有效;

tx_src_rdy_n_i:发送数据源端准备好标志,结合tx_dst_rdy_n_i使用,都为0时表示可以发送数据,

tx_sof_n_i:发送开始标识,低电平有效;

tx_eof_n_i:发送结束标识,低电平有效;

tx_dst_rdy_n_i:发送数据目的端准备好标志;

rx_d_i[0:15]:接收数据

rx_rem_i:最后一个接收数据的高低字节有效标识,0表示,表示rx_d_i[0:7]有效,1表示rx_d_i[0:15]有效;

rx_src_rdy_n_i:接收数据源端准备好标志;

rx_sof_n_i:接收开始标识,低电平有效;

rx_eof_n_i:接收结束标识,低电平有效;

CHANNEL_UP:为1表示GTX通道完成正常初始化;

LANE_UP:指示GTX每个lane是否正常初始化成功,这里只有1个Lane;

SOFT_ERR、HARD_ERR:软、硬件错误指示,正常情况应该为0

tx_lock_i_ila:GTX时钟锁定指示,正常情况应该为1

pll_not_locked_ila:GTX时钟失锁指示,正常情况应该为0

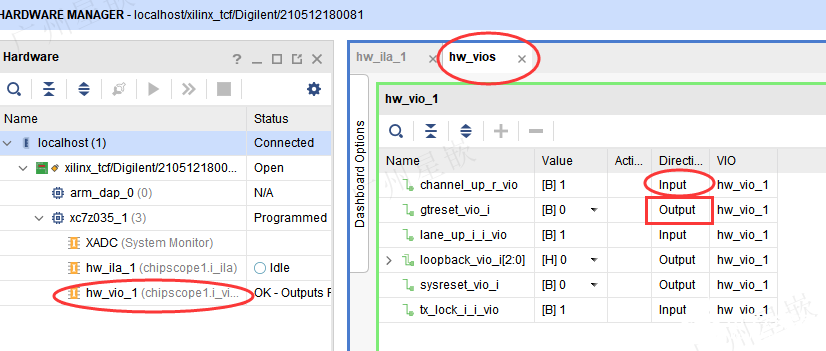

VIO虚拟IO界面如下图所示:

VIO界面上标识Input的为采集信号,用户只能查看对应信号当前的逻辑电平值,1表示高电平,0表示低电平;VIO界面上标识Output的为用户控制信号,用于控制用户逻辑的,用户可以在Value一栏输入0/1电平值,从而达到控制用户逻辑的目的。VIO界面主要用于复位用户逻辑,以及查看通道是否链接成功,VIO界面可以不用操作。

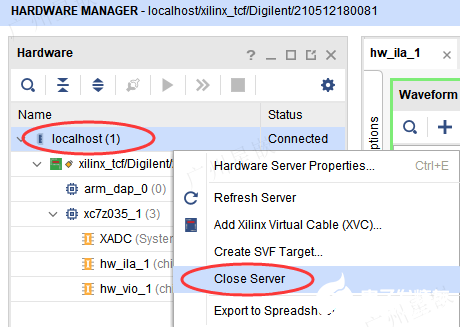

1.1.4.4 退出实验

Vivado调试界面Hardware Manager窗口,右键单击localhost(1),在弹出的菜单中点击Close Server,断开ZYNQ JTAG仿真器与板卡的连接:

最后,关闭板卡电源,实验结束。

审核编辑:汤梓红

-

SFP千兆光模块概述2024-12-02 2498

-

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!2024-09-02 10195

-

Xilinx ZYNQ UltraScale+RFSoCZU27DR 开源RFSOC算法验证评估板2023-08-25 2159

-

ZYNQ7035 PL Cameralink回环例程2023-07-07 1968

-

ZYNQ(FPGA)与DSP之间GPIO通信实现2023-06-16 1881

-

Xilinx Zynq7035 PL Cameralink回环实现2023-02-24 1054

-

Xilinx Zynq7035 PL SFP光口通信例程2023-02-20 1331

-

DSP+ZYNQ多核例程使用手册-XQTyer【开源】2022-12-27 21361

-

Xilinx Zynq7035算力指标2022-12-15 1524

-

基于FPGA的光口通信开发案例|基于FPGA Kintex-7 SFP+光口的10G UDP网络通信开发案例2021-01-21 4948

-

zynq XC7Z100板卡学习资料:基于zynq XC7Z100 FMC接口通用计算平台2020-03-24 4672

-

ZYNQ7000开发平台的AX7Z035开发板用户手册免费下载2019-06-24 3651

-

易天光通信SFP电口模块和10G SFP+电口模块介绍2019-04-29 9378

-

百科:BIDI SFP光模块和普通SFP光模块的区别2018-05-31 6554

全部0条评论

快来发表一下你的评论吧 !