ZYNQ与DSP之间EMIF16通信

电子说

描述

[基于TI KeyStone架构C6000系列TMS320C6657双核C66x 定点/浮点DSP以及Xilinx Zynq-7000系列SoC处理器XC7Z035-2FFG676I设计的异构多核评估板,由核心板与评估底板组成。]

1.1 ZYNQ与DSP之间EMIF16通信

1.1.1 例程位置

ZYNQ例程保存在资料盘中的DemoZYNQPLFPGA_DSP_EMIF文件夹下。

DSP例程保存在资料盘中的DemoDSPXQ_EMIF16文件夹下。

1.1.2 功能简介

实现DSP与ZYNQ PL端之间EMIF16接口传输功能。

DSP首先通过EMIF16接口往ZYNQ PL端发送4096字节数据,然后再读回来,并检测数据是否有错,数据发送、读回以及错误情况实时打印。

ZYNQ PL端开辟了一块RAM空间,用于存放DSP通过EMIF16接口写入的数据,同时用作DSP通过EMIF16接口读数据时的数据源。

DSP与ZYNQ PL端之间EMIF16接口连接示意图如下图所示:

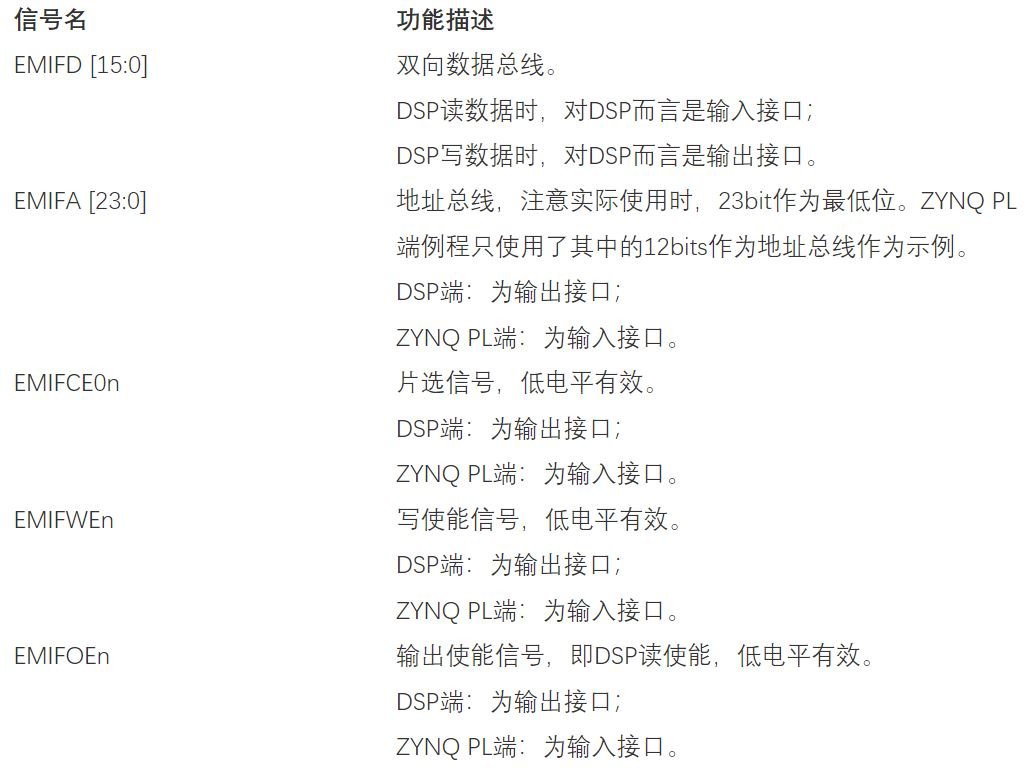

EMIF16接口信号定义说明如下表格所示:

1.1.3 例程使用

1.1.3.1 加载运行ZYNQ程序

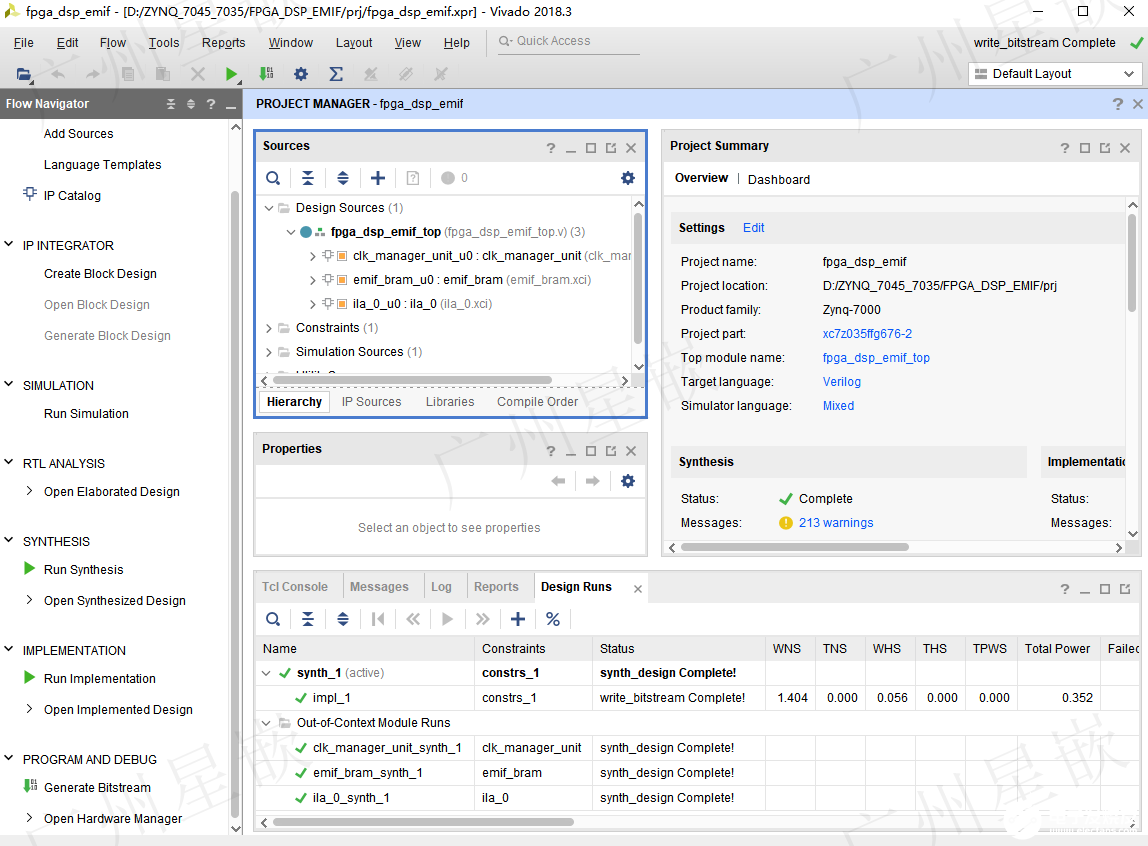

1.1.3.1.1 打开Vivado工程

打开Vivado示例工程:

工程打开后界面如下图所示:

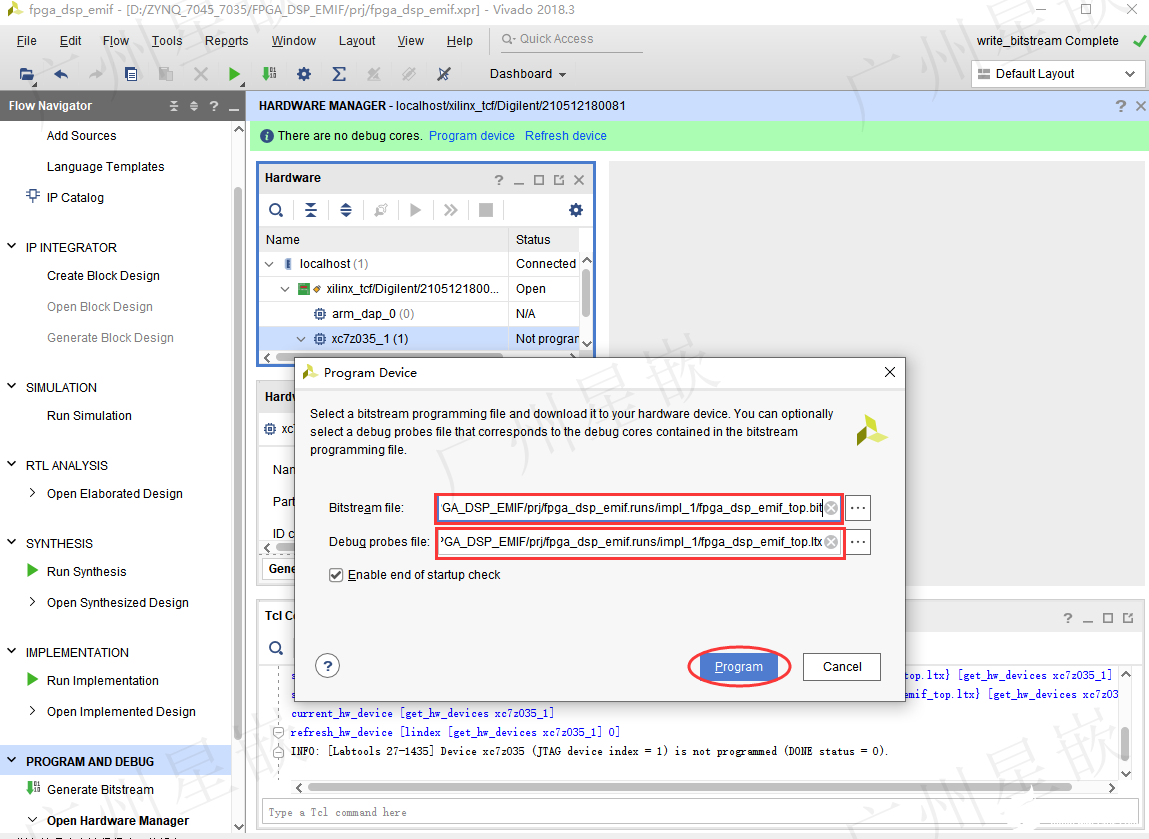

1.1.3.1.2 下载ZYNQ PL程序

下载bit流文件fpga_dsp_emif_top.bit,并且配套fpga_dsp_emif_top.ltx调试文件,如下图下载界面所示:

1.1.3.2 加载运行DSP程序

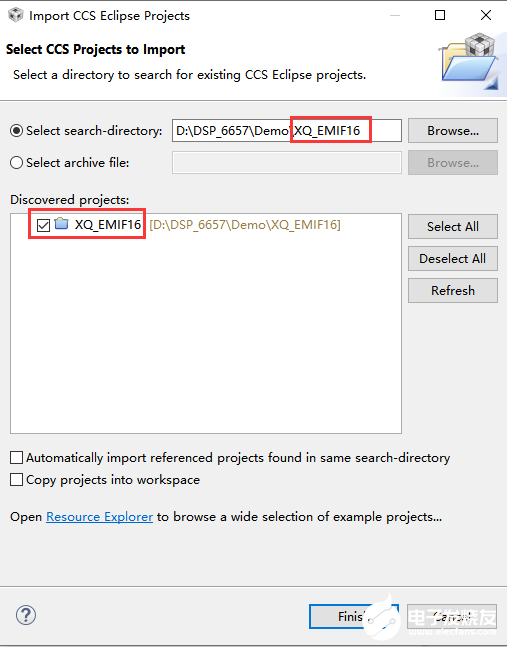

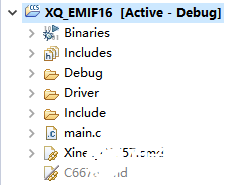

1.1.3.2.1 CCS导入例程

CCS软件导入EMIF16示例工程XQ_EMIF16,如下图所示:

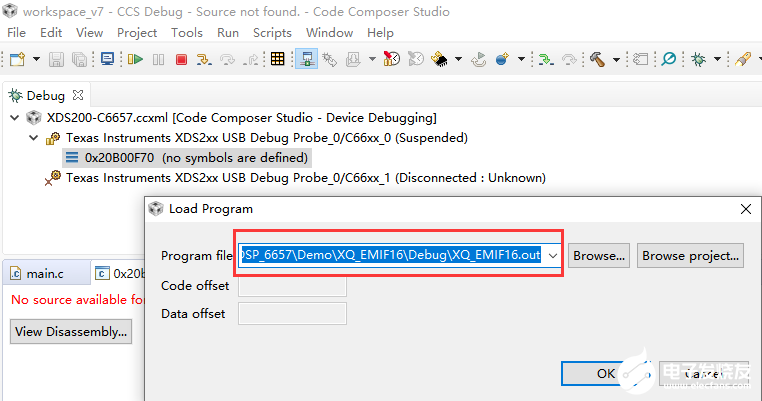

1.1.3.2.2 下载运行CCS程序

下载DSP可执行文件XQ_EMIF16.out:

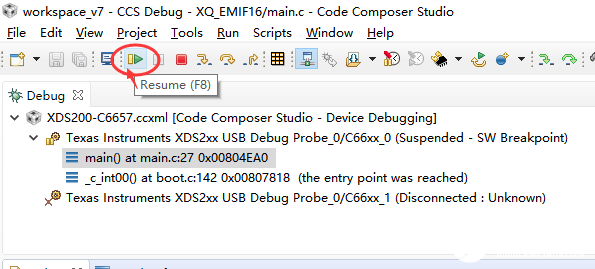

点击Resume运行DSP程序:

1.1.3.3 运行结果说明

1.1.3.3.1 DSP程序运行结果

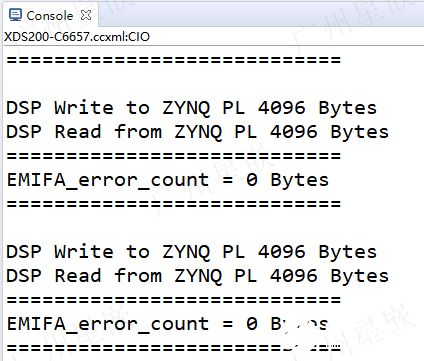

DSP首先通过EMIF16接口往ZYNQ PL端发送4096字节数据,然后再读回来,并检测数据是否有错,数据发送、读回以及错误情况实时打印,如下图所示:

1.1.3.3.2 ZYNQ PL程序运行结果

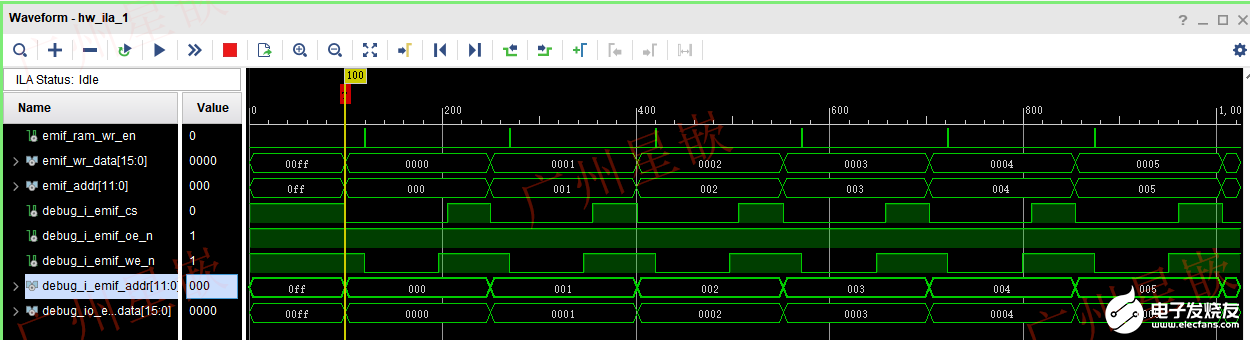

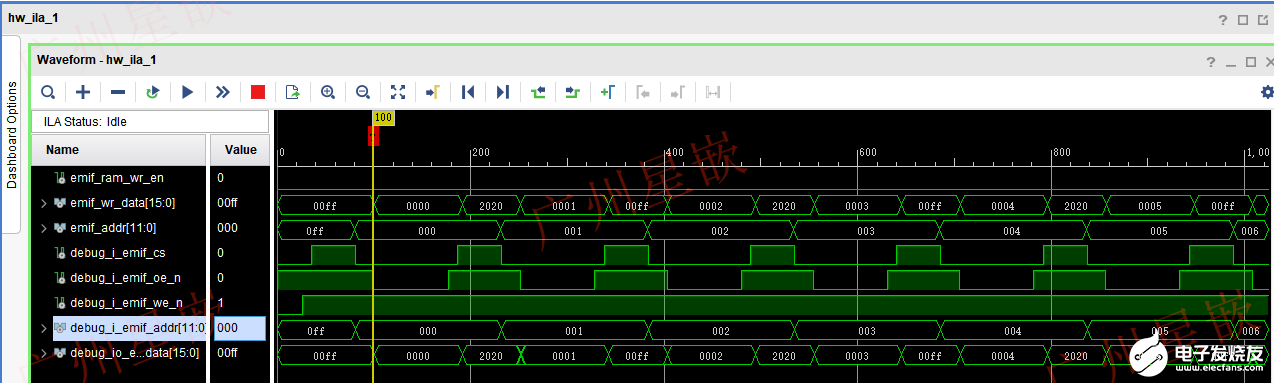

ZYNQ PL端提供的ILA调试窗口,可以实时抓取采集EMIF16总线信号时序波形。

DSP通过EMIF16总线接口发送数据(即写ZYNQ PL端RAM)示例如下图所示:

DSP通过EMIF16总线接口读回数据(即读ZYNQ PL端RAM)示例如下图所示:

1.1.3.4 退出实验

CCS软件窗口上,点击Terminate断开DSP仿真器与板卡的连接。

Vivado调试界面Hardware Manager窗口,右键单击localhost(1),在弹出的菜单中点击Close Server,断开ZYNQ JTAG仿真器与板卡的连接。

最后,关闭板卡电源,实验结束。

文章来源:星嵌电子

审核编辑:汤梓红

-

ZYNQ(FPGA)与DSP之间GPIO通信实现2023-06-16 1910

-

ZYNQ与DSP之间EMIF16通信介绍说明2023-03-21 1772

-

ZYNQ与DSP之间EMIF16通信2023-03-08 1298

-

ZYNQ与DSP之间SRIO通信的设计实现2023-02-21 1595

-

DSP+ZYNQ多核例程使用手册-XQTyer【开源】2022-12-27 21397

-

XQ6657Z35-EVM 的DSP + ZYNQ核心板,SRIO通讯2022-12-05 1360

-

6678 EMIF16 Nor Flash多核boot2019-05-14 5509

-

请问C6655的EMIF16与DDR EMIF有什么区别?2019-01-15 4274

-

基于C66x平台DSP与FPGA通信测试2018-10-31 3148

-

通过EMIF16将外接FPGA输出的信号传给DSP,请问下能不能提供个EMIF的例程?2018-06-25 3409

-

c6678 emif162018-06-24 2471

-

C6678 EMIF16 NOR FLASH BOOT2018-06-21 3823

-

C6678 EMIF16 地址空间只有32M bytes 这个疑惑怎么理解?2018-06-20 4914

-

请问6678的EMIF16支持32MB norFLASH不?2018-05-25 3224

全部0条评论

快来发表一下你的评论吧 !