Xilinx FPGA CFGBVS 引脚以及BANK电压硬件设计注意事项

电子说

1.4w人已加入

描述

配置组电压选择(CFGBVS)引脚必须设置为高电平或低电平,以确定I/O电压支持的引脚在bank0,以及多功能引脚在bank14和15在配置时使用。CFGBVS是一个逻辑输入,VCCO_0和GND之间的引脚引用。当CFGBVS引脚为高(例如,连接VCCO_0提供3.3V或2.5V),在bank0上的配置和JTAG I/O支持在配置期间和配置后,在3.3V或2.5V下运行。

当CFGBVS引脚为Low时(例如,连接到GND),bank0的I/O支持1.8V或1.5V运行。

在1.2V时不支持配置。

CFGBVS引脚设置决定I/O电压支持bank0在任何时候,和配置中的bank14和bank15。VCCO为每个配置组提供,如果在配置过程中使用CFGBVS,必须匹配CFGBVS的选择,如果CFGBVS与VCCO_0绑定,电压选择为2.5V或3.3V,若CFGBVS与GND绑定,则为1.8V或1.5V。

关于FPGA的配置模式。

注意:无论如何,在VCCO_0电压级别的bank0中始终支持JTAG接口配置模式。

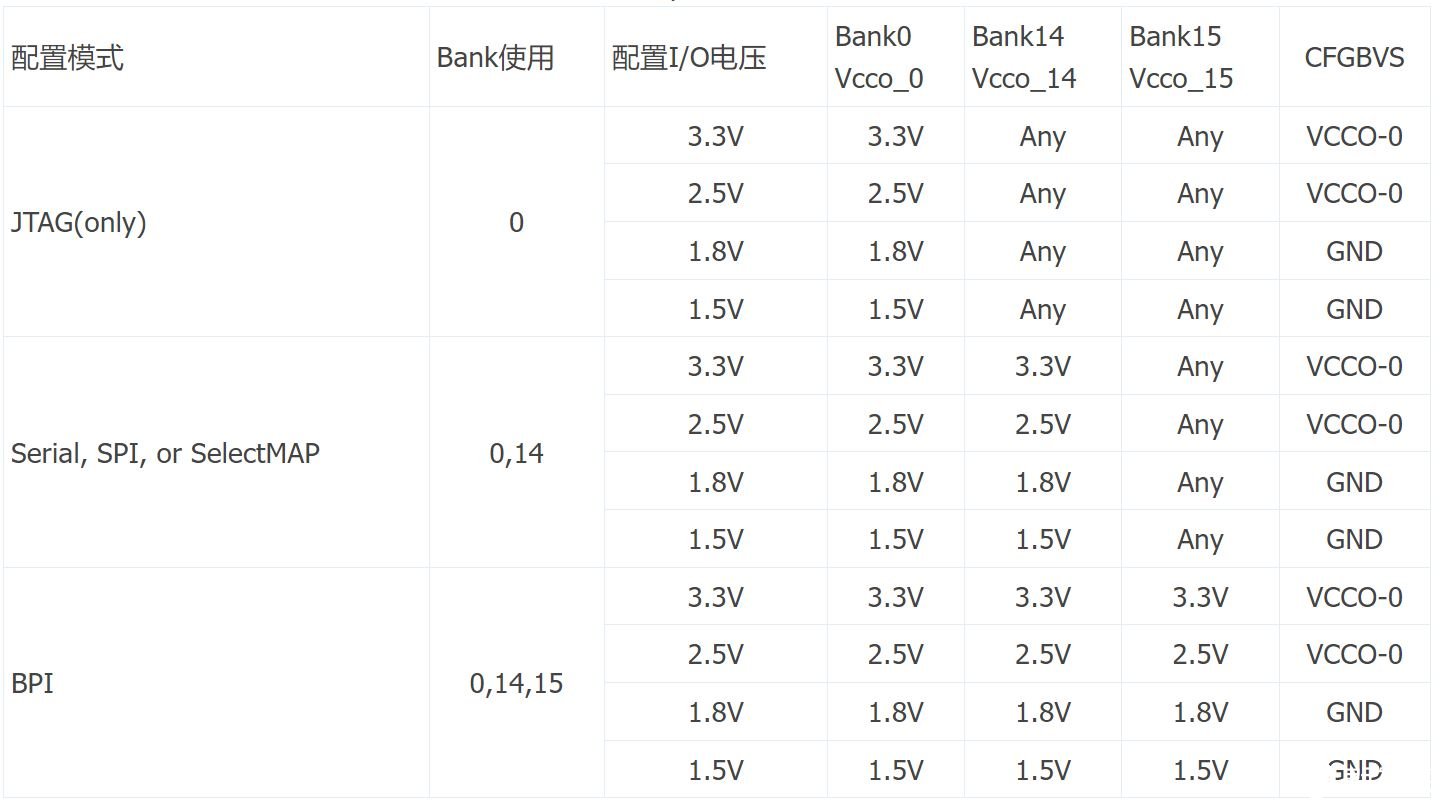

设置CFGBVS引脚支持所需的配置I/O电压。(仅支持Spartan-7、Artix-7和Kintex-7 FPGA配置模式)见下表:

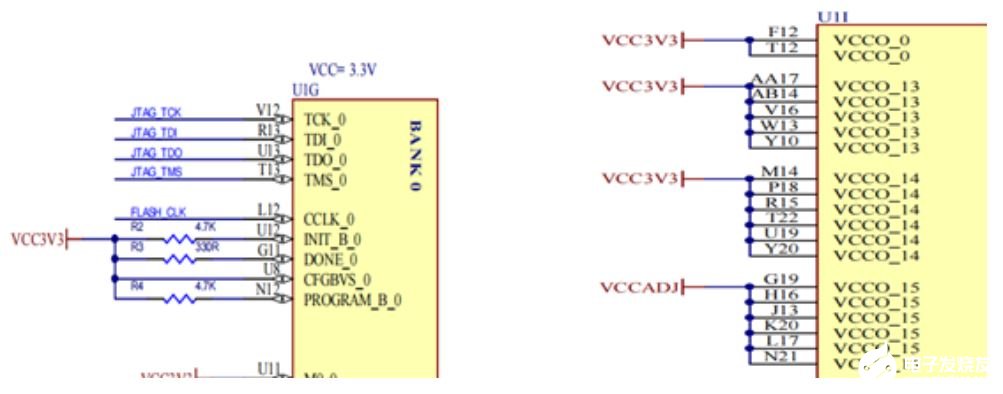

下图所演示的为米联客MA703核心板中,CFGBVS接入3.3V后bank0和bank14、15可接入的电压,由于使用的是QSPI FLASH BANK14必须和BANK0是相同电压,这里设置的是3.3V。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

xilinx FPGA IOB约束使用以及注意事项2025-01-16 2085

-

先进FPGA的电源设计注意事项(电源设计器121)2024-08-26 413

-

xilinx的FPGA,BANK引脚VREF,VRN,VRP都是什么意思?2023-11-28 1302

-

FPGA的有源电容器放电电路注意事项2023-07-25 681

-

安全光幕选型方法以及注意事项2023-06-28 1719

-

FPGA管脚调整的注意事项2023-06-20 1861

-

Xilinx FPGA电源设计与注意事项2023-01-17 3462

-

硬件开发流程及注意事项是什么2021-04-27 1865

-

【MiniStar FPGA开发板】配套视频教程——浅谈高云硬件设计注意事项(干货分享)2021-04-16 4924

-

Xilinx XC7A35T-CSG325(Artix 7)和CFGBVS引脚疑问的解答?2020-07-25 5151

-

RTL8316D硬件设计注意事项pdf2018-03-08 1389

-

STM32硬件电路学习注意事项2015-05-05 7885

-

FPGA学习及设计中的注意事项2011-09-08 1074

-

FPGA设计的注意事项2010-04-10 1193

全部0条评论

快来发表一下你的评论吧 !