如何开启Versal的XilSEM功能

电子说

描述

Versal器件不再有传统的SEM IP;Soft Error Mitigation功能在Vitis套件中以library形式出现,称为XilSEM。XilSEM基本功能和之前的SEM IP类似:通过不断地扫描,检测出PL CRAM中出现的SEU翻转,上报,再根据系统需要决定是否做纠正或者重新配置PL。根据Versal器件的特点,XilSEM的扫描范围进一步扩大,还可选择是否扫描NPI寄存器,对PL之外的其他功能模块的配置数据做监测。

这篇文章介绍了如何开启Versal最基本的XilSEM功能。

Vivado/Vitis 2022.1

Board used: VCK190

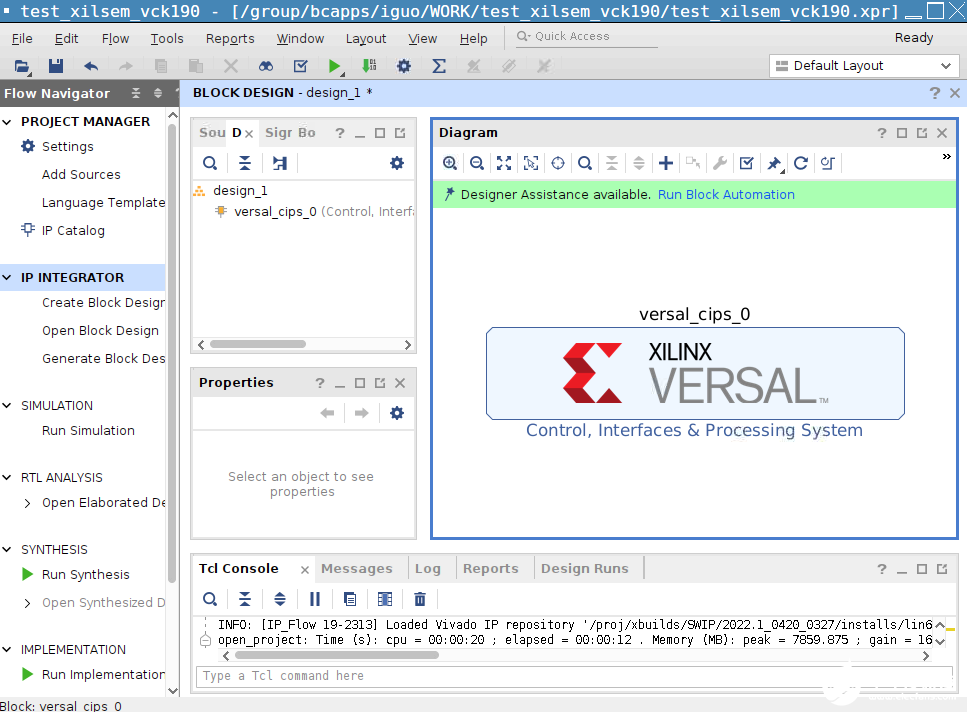

1. 首先基于VCK190开发板,建立一个project. 创建Block Design并添加CIPS IP:

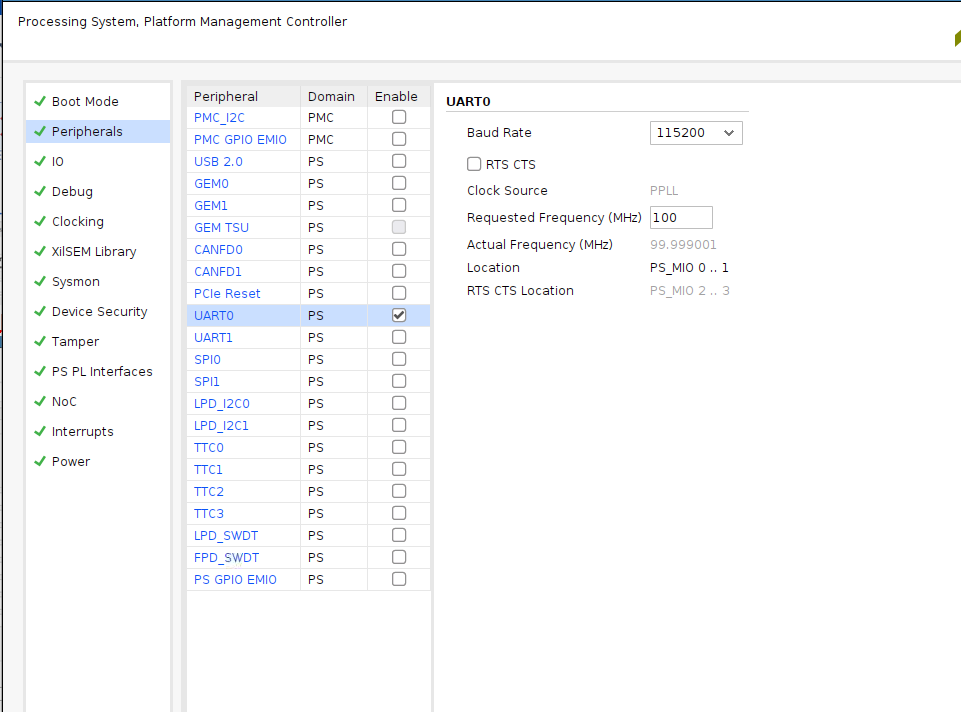

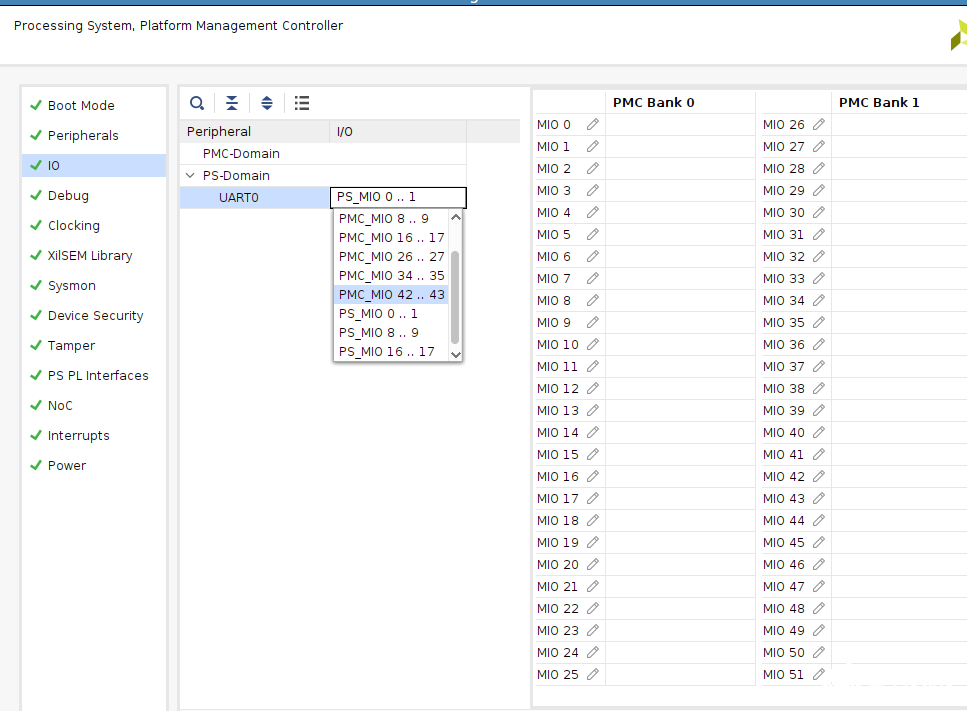

按照下图配置PS PMC,使能串口以输出XilSEM的log:

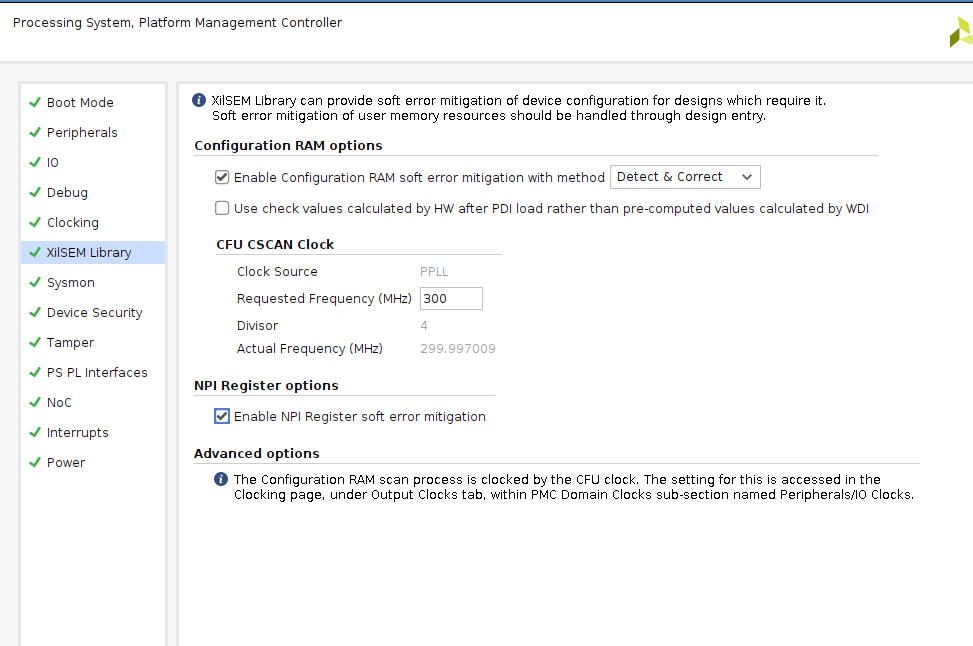

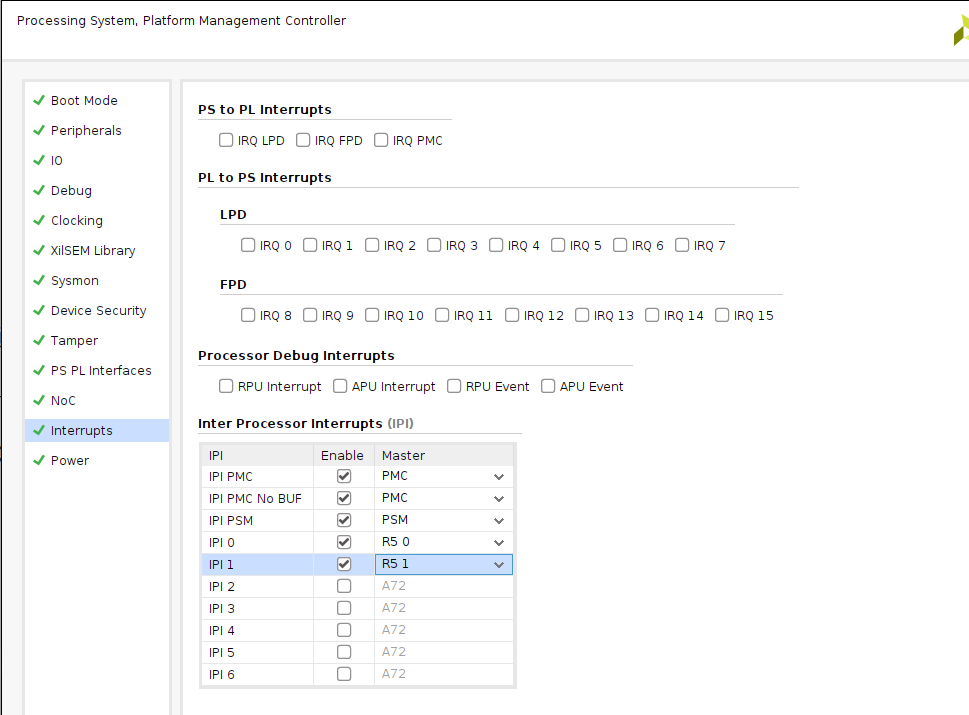

从左侧选项中找到并使能XilSEM库,并添加中断:

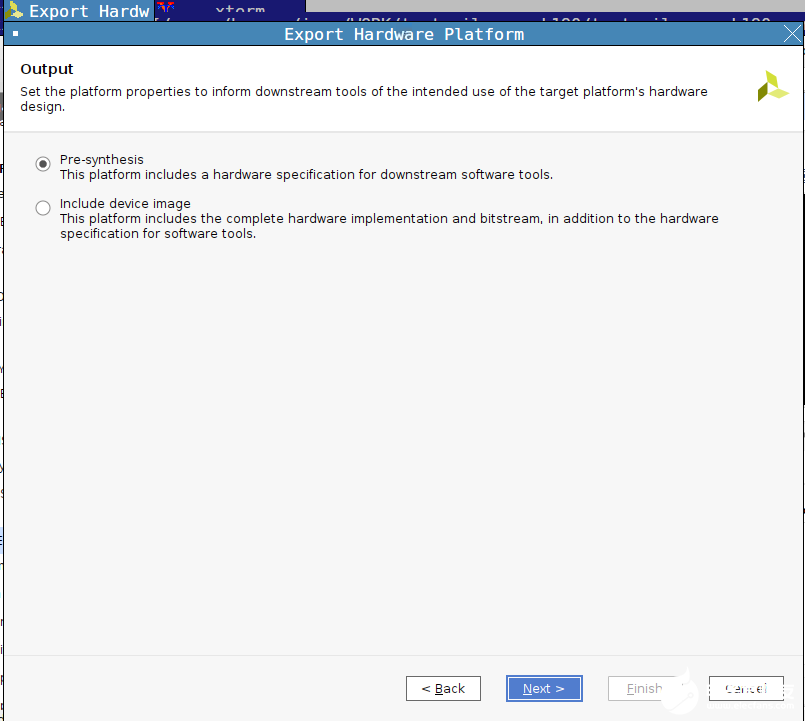

生成HDL Wrapper以及pdi文件,并将设计导出到Vitis中。导出时,选择‘Pre-synthesis’或‘Include device image’均可。

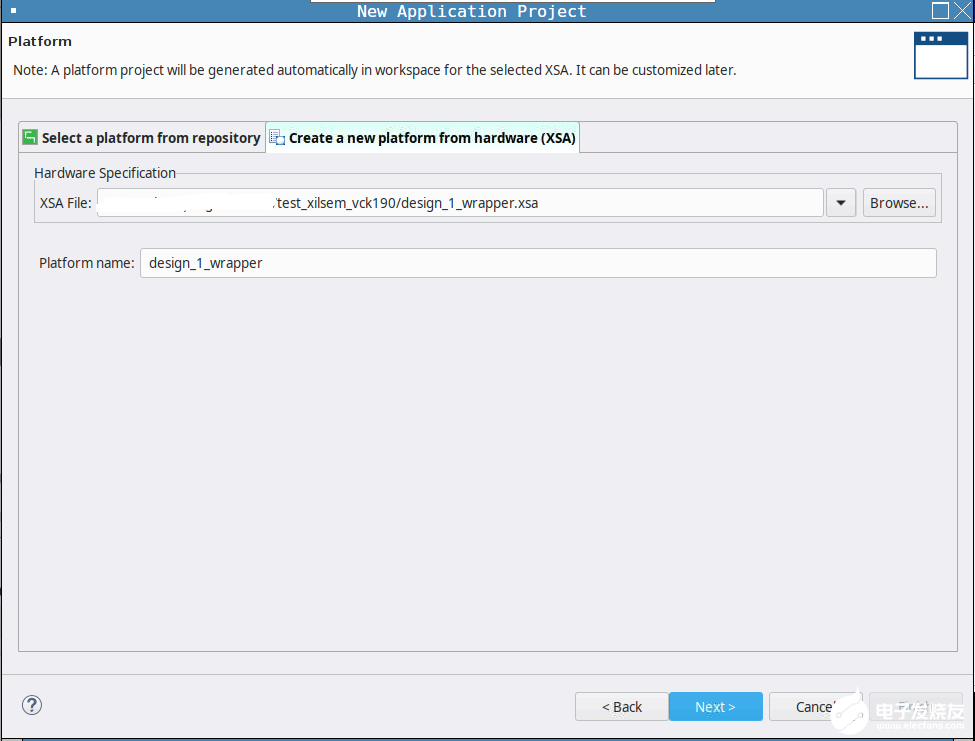

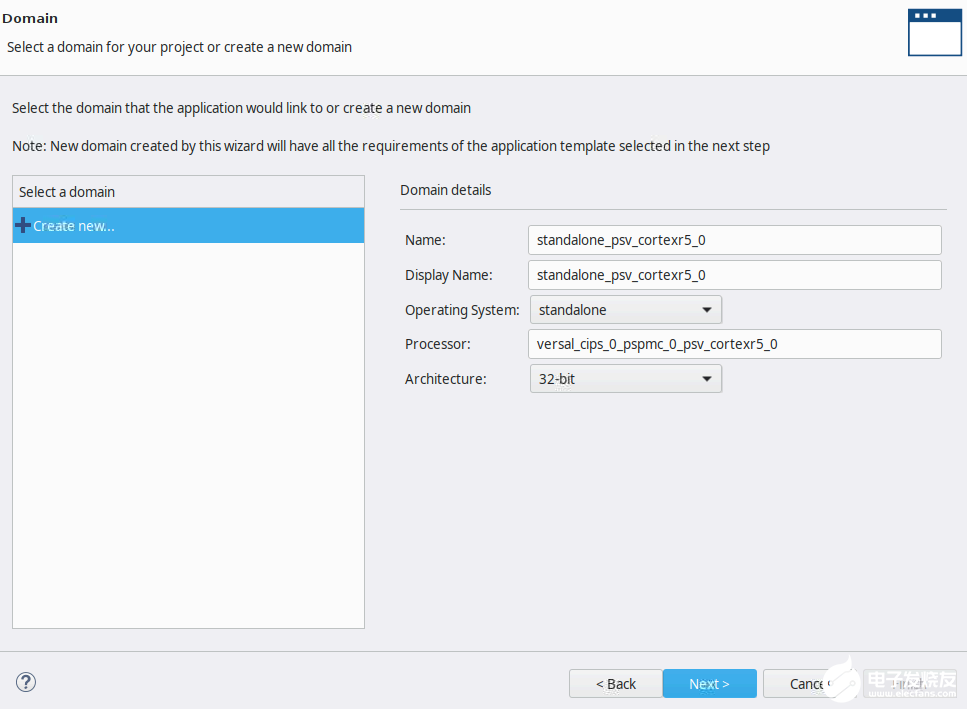

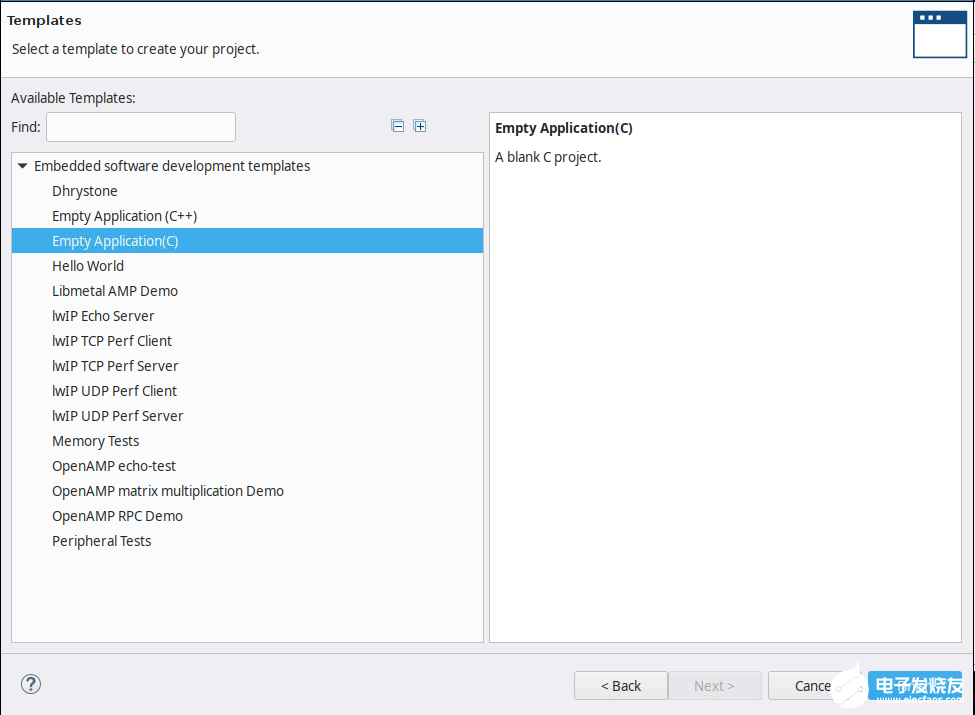

2. 打开Vitis,基于之前生成的.xsa,建立一个新的application工程:

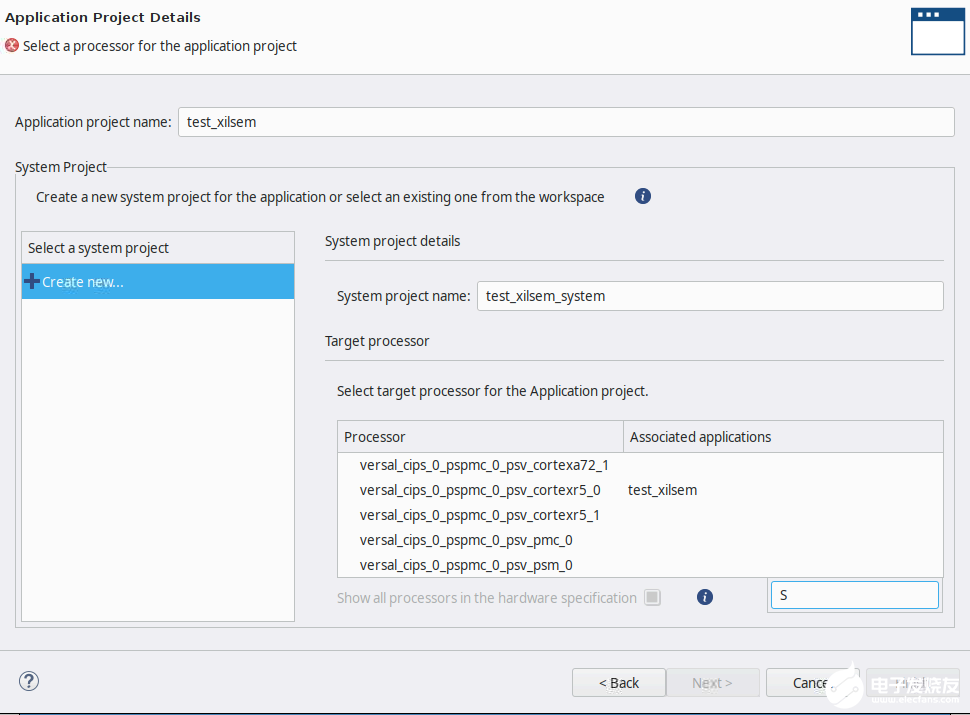

基于R5,建立一个空白Application:

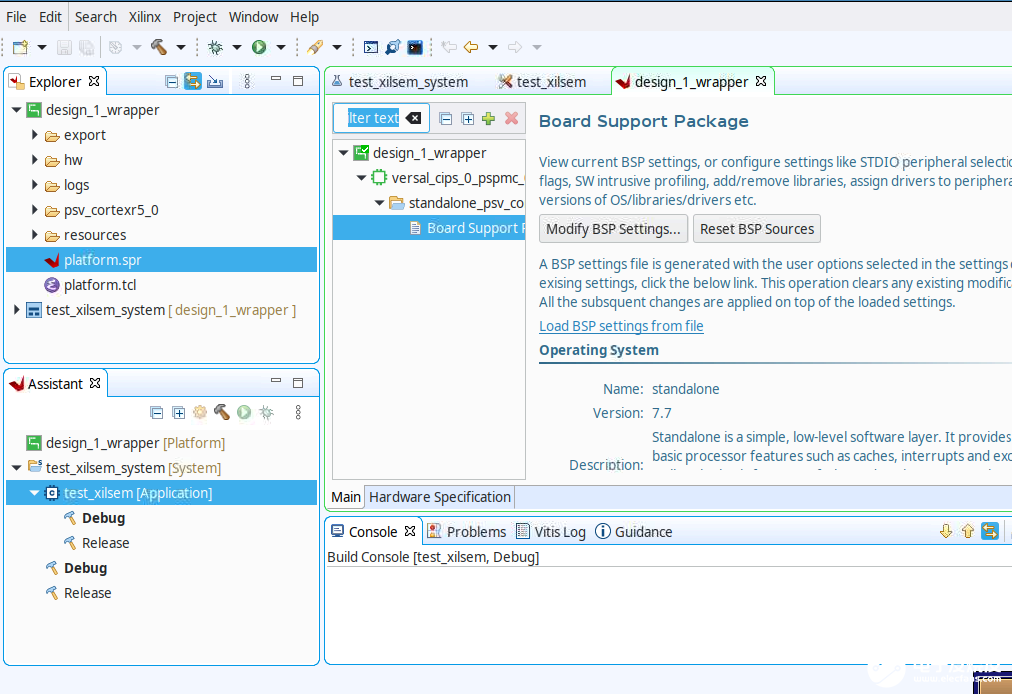

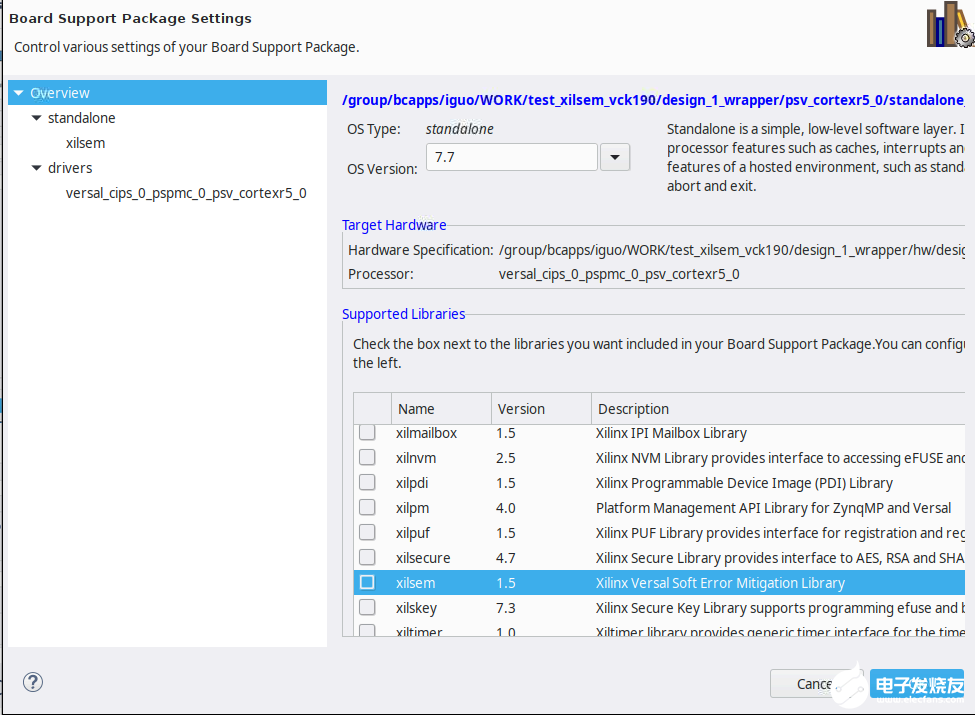

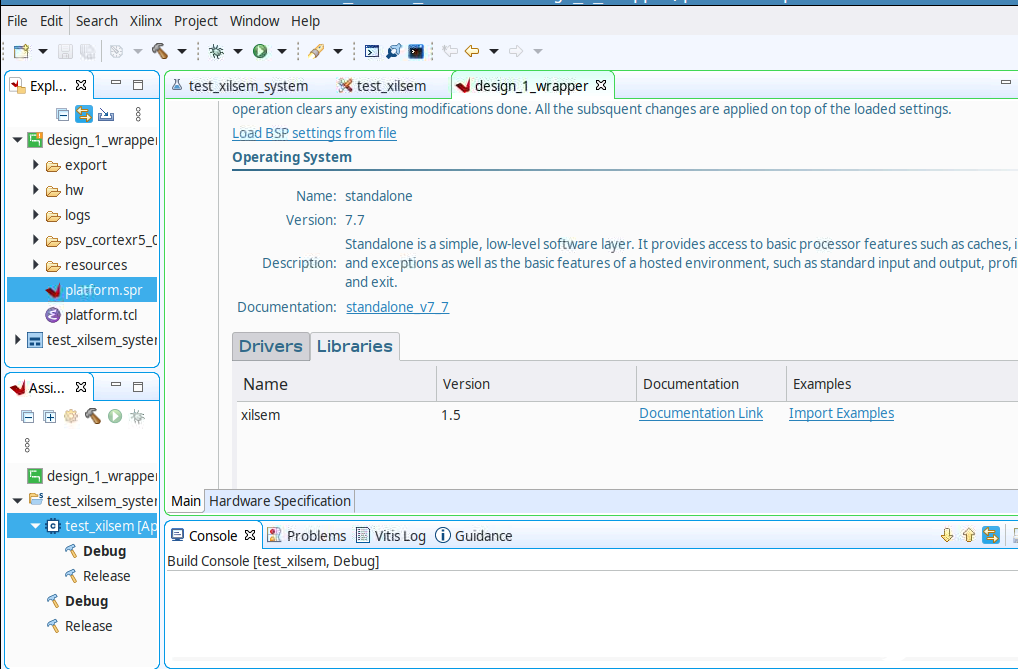

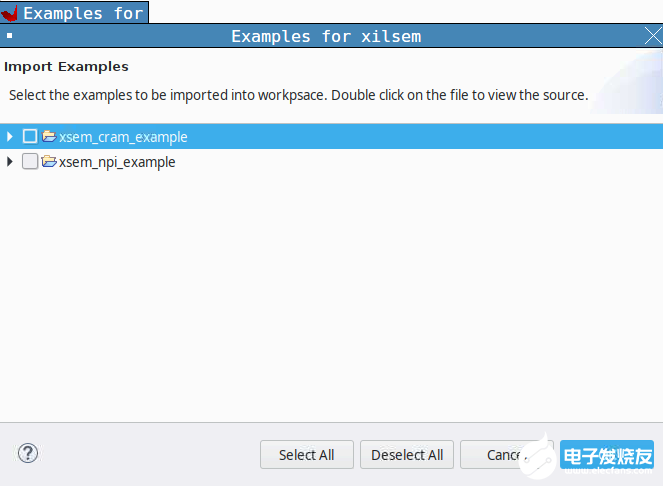

修改BSP设置,找到XilSEM库,点击 ’Import Examples’, 导入其example:

sem_cram_example,点击OK。

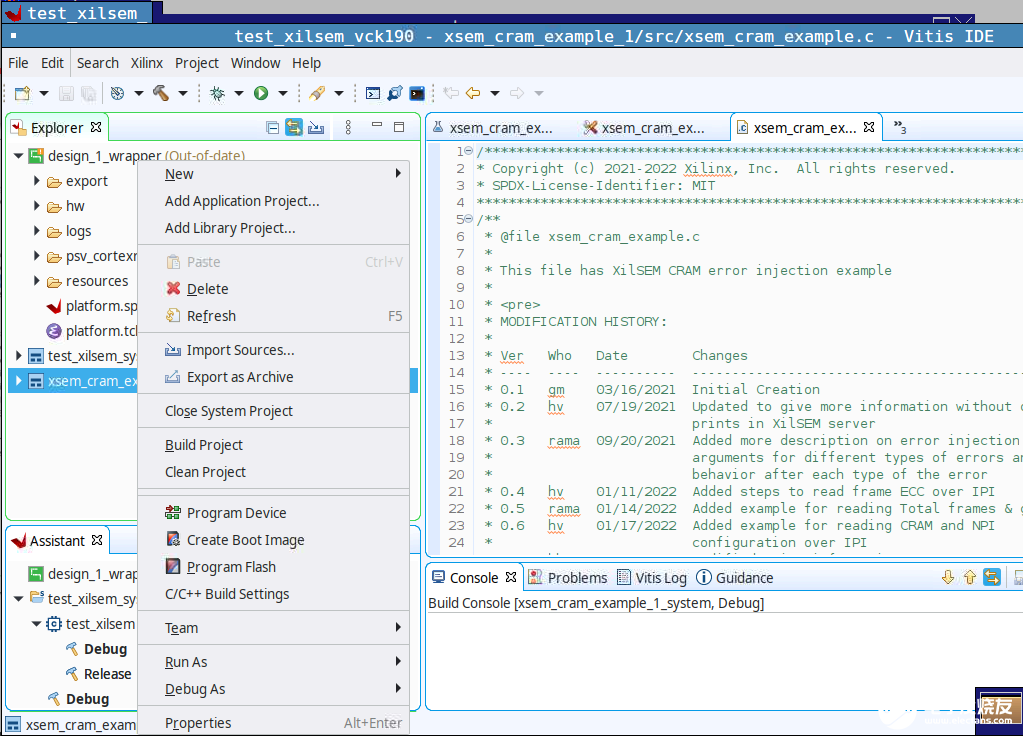

编译新建的xsem_cram_example_1工程,生成elf文件。

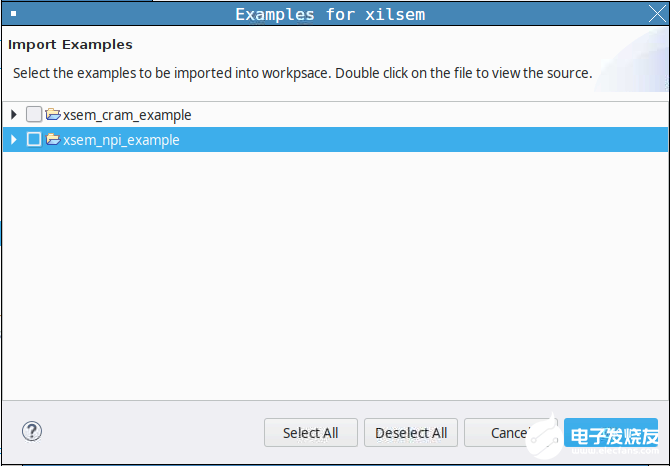

可以重复一样的步骤,再次选择xsem_npi_example, 则可以生成NPI扫描的elf文件。

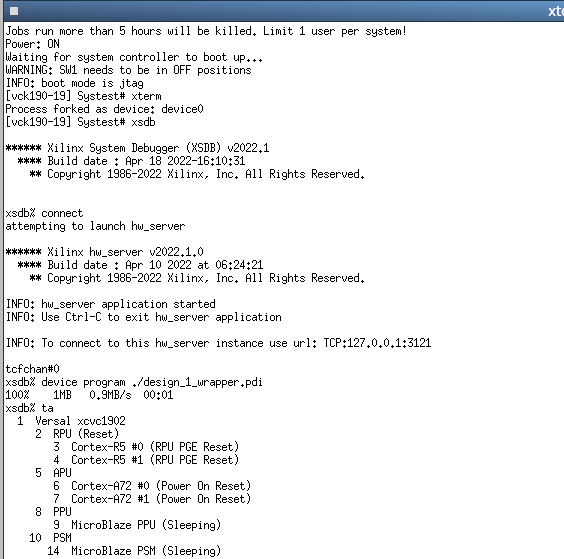

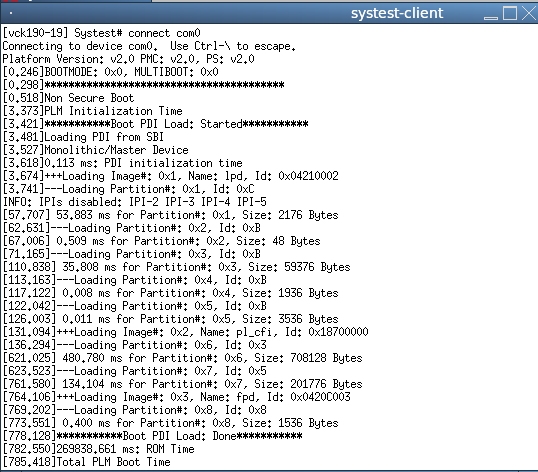

3. 连接VCK190开发板,打开串口显示窗。下载pdi文件。可以看到输出log如下:

执行如下指令序列进行cram elf文件的下载:

ta

ta 3

rst -proc

dow -force <.elf>

con

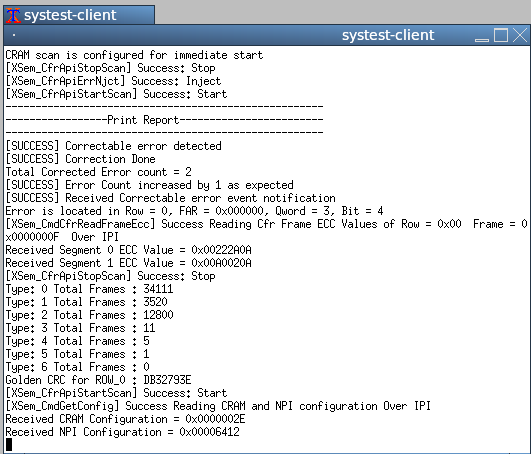

可观测到串口输出如下。此时XilSEM已经开启并运行了。注意example程序进行了一次插错测试。

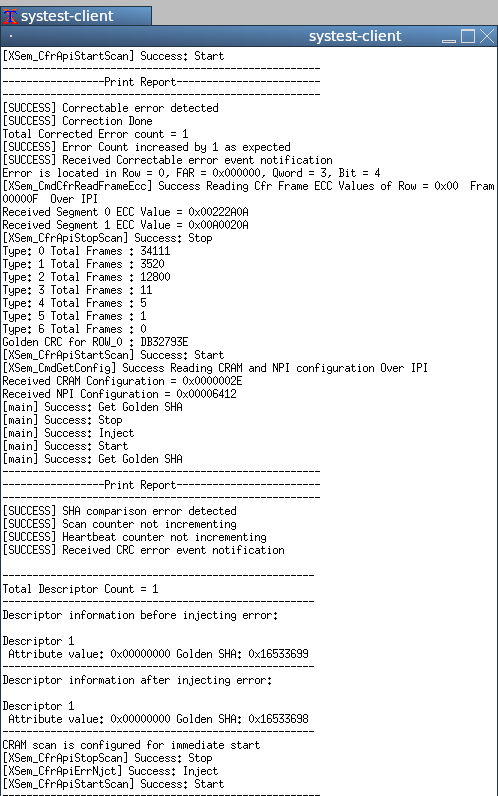

同样方式,下载NPI elf,log打印信息如下:

这篇文章介绍了在工程中如何开启最基本的XilSEM功能,可以添加任意自己的设计。但是对于某些高级功能比如DFX,还需要在将来版本中完成兼容。

审核编辑:汤梓红

-

基于AMD Versal器件实现PCIe5 DMA功能2025-06-19 2000

-

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)2024-03-07 2936

-

如何推迟XilSEM扫描功能的开始?(二)2024-03-13 1462

-

Proof of Life:Versal 诞生的证据2019-07-02 1950

-

Xilinx宣布7nm Versal AI Core和Versal Prime系列器件全面量产出货2021-04-28 4511

-

Versal ACAP中的配电系统2021-09-09 5224

-

基于Versal的图像恢复管道2023-06-14 628

-

Versal启动文件简述2023-07-07 2260

-

Versal平台的系统级优势2023-09-14 539

-

Versal ACAP设计指南2023-09-13 482

-

怎样开启javascript功能2023-12-03 6099

-

Versal 自适应SoC设计指南2023-12-14 541

-

ALINX VERSAL SOM产品介绍2024-08-05 1966

-

AMD第二代Versal AI Edge和Versal Prime系列加速量产 为嵌入式系统实现单芯片智能2025-06-11 2049

-

探索AMD XILINX Versal Prime Series VMK180评估套件,开启硬件创新之旅2025-12-15 773

全部0条评论

快来发表一下你的评论吧 !