S2C为Xilinx原型验证系统提供突破性验证模块技术

电子技术

描述

S2C日前宣布其Verification Module技术(专利申请中)已可用于其基于Xilinx的FPGA原型验证系统中。V6 TAI Verification Module可以实现在FPGA原型验证环境和用户验证环境之间高速海量数据传输。用户可以使用Xilinx ChipScope或者第三方调试环境,同时查看4个FPGA。另外,V6 TAI Verification Module还可以用于1.3M~4.7M ASIC门的原型设计。V6 TAI Verification Module具有PCIe Gen2、千兆串行收发器、SATA2和USB 3.0等高速接口。V6 TAI Verification Module硬件现已供使用。

S2C的董事长及首席技术官Mon-Ren Chene先生说:“我们在今年6月份首次发布的Verification module技术是为使用Xilinx原型验证系统的客户提供的技术。这是一种可以将用户的FPGA原型环境和用户验证环境接口的突破性技术。由于设计通 常被分割到多个FPGA中,用户可以有这项新能力同时对多个FPGA进行调试对他们来说非常重要。FPGA原型验证系统以系统速度或者接近系统速度运行。 通过高速接口,FPGA原型验证环境可以更容易地连接到实际目标系统环境。”

三种运行模式

通用的S2C V6 TAI Verification Module提供了三种使用模式:验证模式、调试模式和逻辑模式。 验证模式使用SCE-MI或定制的C-API通过一条 x4-lane PCIe Gen2通道实现海量数据和PC之间的传输。在调试模式中,V6 TAI Verification Module通过使用Xilinx ChipScope或者其它第三方工具从而实现了多个FPGA的同步调试且同时保持用户的RTL名。在逻辑模式中,用户可以原型化一个设计,其容量能达到 4.7M门。 所有对Verification Module的调试和验证设置都是在S2C 的TAI Player Pro™中完成。

验证模式

验证模式利用TAI Verification Module的高速PCIe Gen2接口将大量仿真数据在PC和TAI Logic Module之间进行双向快速地传输。该模式能将原型系统和仿真器直接连接进行同步仿真。用户可以利用下图所示的S2C提供的定制C-API或者符合行业 标准的SCE-MI接口:

调试模式

调试模式则利用了用户现有的Xilinx ChipScope或者其它第三方调试环境。V6 TAI Verification Module从Logic Module中的多个FPGA获取用户定义的信号并接收到V6 TAI Verification Module,通过JTAG接口与ChipScope连接。

V6 TAI Verification Module 使用Xilinx ChipScope Analyzer可同时对放在两块Dual V6 TAI Logic Module上的FPGA设计进行调试。

最高能见度

每个Virtex 6 FPGA的120信号都接到了V6 TAI Verification Module的FPGA中。用户能在4 个V6 FPGA中进行120 x N信号的路径选择。最初的发布中,N固定在4上,但今后将由用户定义。用户所需要做的是在设计综合前在RTL级选择Probes并且将它们按照每个 FPGA120个probe来进行分组。S2C的TAI Player Pro自动采用多路复用技术将来自多个FPGA的调试信号发送至V6 TAI Verification Module的单个Xilinx ChipScope,并保留RTL名。将使用Xilinx ChipScope调试过程中的调试数据存储在V6 TAI Verification Module的存储器中直到满足预先设置的触发条件为止,再将这些调试数据读取出来。

逻辑模块

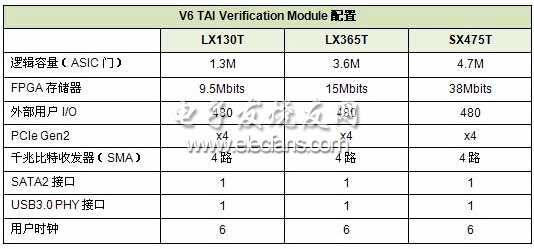

V6 TAI Verification Module可以作为单个原型板,为高达4.7M门容量的小规模SoC或ASIC设计使用。V6 TAI Verification Module可以配备Xilinx LX130T、LX365T 或者SX475T FPGA上,而且在4个LM连接器上共有480个外部I/O,x4 PCIe Gen2接口,4路通过SMA连接器的千兆串行收发器、一个SATA2接口以及一个USB3.0 PHY接口。

配置详情显示在下表:

-

思尔芯S2C:硅谷到中国,20年的坚守和持续创新,只为让验证更高效2024-01-26 3674

-

国微思尔芯助力新基讯完成5G芯片系统的原型验证2022-07-22 2377

-

S2C推出基于Intel的业界最高容量FPGA的Prodigy ™原型解决方案2019-11-20 2765

-

高频RFID芯片的FPGA原型验证平台设计及验证2019-05-29 2847

-

怎么采用FPGA原型系统加速物联网设计?2018-08-07 2613

-

2018全球十大突破性技术发布2018-03-27 4157

-

S2C新增的Prodigy™原型就绪接口子板库使得FPGA原型变得更加精准2017-02-08 1206

-

S2C为Virtex7 2000T FPGA快速ASIC原型验证系统组建Prototype ReadyTM接口库2013-01-30 2103

-

S2C发布最新ASIC原型验证平台Quad V72013-01-23 3526

-

TAKUMI公司:图象IP核参考设计可用于S2C原型验证平台2012-07-03 3440

-

S2C发布最新Prototype Ready ARM11和ARM9模块2012-06-06 1809

-

S2C开发出原型验证产品Verification Module2011-06-16 2542

-

S2C发表最大容量SoC/ASIC原型系统2011-04-26 1487

-

S2C与Japan Circuit合作,共同开发下一代超高速2009-08-07 753

全部0条评论

快来发表一下你的评论吧 !