开发板中的存储

电子说

描述

日常生活离不开各类电子产品,我们常见的电子产品通常以电路板作为载体,包含信息采集,信息处理,存储,执行等功能。

对于工程师来说,比起电路板,说开发板可能更亲切一些。由于工程师在研发初期,大都在开发板上验证功能,可以说开发板是所有电子设备最原始的状态。开发板与存储之间有什么样的关联呢?

开发板:MCU类VS Linux类 不同的存储方式

根据处理器类型,开发板一般分为两类:MCU类和 Linux 类。它们二者的存储方式还是有很大的差异的。

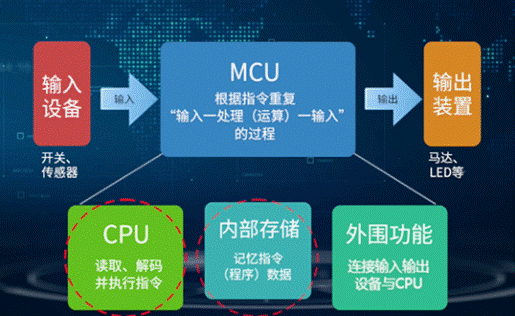

首先是MCU类开发板,MCU就是工程师口中的单片机,采用MCU的系统一般仅需要简单的操作或者控制,比如接收按钮或按键的输入信号,按照事先编好的程序,指挥马达和LCD的外围功能电路动作。

下图就是一个MCU系统的主要组成部分:

可以很明显的看出来MCU类的开发板它的存储功能靠内部存储就足够了。

内部存储分为ROM和RAM两大类,存储空间大小在几十到几百KB不等。如果不运行操作系统和图形系统,MCU控制指令和代码就会相对简单,内部ROM和RAM可以满足大多数应用的系统存储要求。

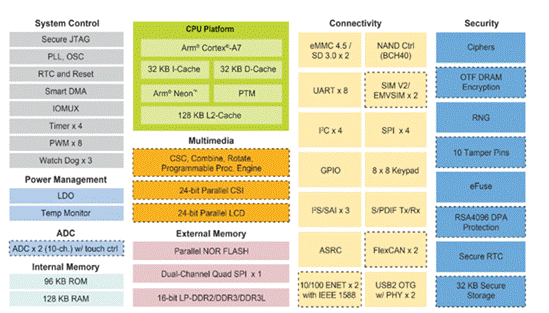

另外一类是Linux类开发板,这类开发板的处理器我们最常见的有Arm Cortex A系列。

目前主流Linux开发板运行的是Linux系统,采用的多是Arm Cortex A系列的处理器。同Windows操作系统一样,Linux是一种开放源代码,功能强大、可靠、稳定性强、灵活而且具有极大的伸缩性的操作系统。

从下图可以看出,Arm Cortex A处理器的内部存储有96KB的ROM和128KB的RAM。

如果不跑操作系统,做一些简单的输入输出控制,代码量不多的话,自带的内部存储ROM和RAM是够用的。但是Arm Cortex A处理器的运算资源很强大,通常是使用在嵌入式产品上,嵌入式产品的软件是需要跑Linux操作系统的。

它的软件方面主要分为两大块:Linux内核和用户应用程序。如果Linux使用比较轻量级的busybox来做文件系统,使用版本比较低的内核kernel 3.2最终编译完后,Linux内核镜像大小在4-10M,最精简的文件系统就在16M左右,除此之外,用户另外用户肯定会在这个系统之上搭建自己的复杂的业务逻辑,要想支撑起比较复杂的用户应用程序,仅靠处理器的内部存储空间显然是不够的。

大家看看手边的Linux开发板,不难发现他们都额外增加了独立的存储芯片:SDARM和FLASH。

Linux开发板上的外部存储芯片

典型的Linux开发板,比如大家都很熟悉的树莓派4,使用的外部存储芯片就是美光的8GB LPDDR4 SDRAM。

或许有人就疑惑了:为什么是外接存储芯片,而不是直接在处理器芯片内置大容量Flash和RAM?

原因有很多,比如成本问题。如果单纯的加大RAM会占用很多硅片面积,这也会直接导致芯片价格的增加。在同样的硅片上,占用硅片面积大会使得切割出来的芯片晶圆数量减少。再者,RAM的工艺繁杂,RAM所占硅片的面积大,就会容易产生缺陷,导致芯片的整体良品率下降。

外部存储芯片如何与处理器进行工作的呢?

把Linux开发板看成一个大工厂,处理器是加工车间,外部的存储芯片则相当于仓库。为了提升工厂的产能,一是提高处理器的性能,这样可以提升加工车间的效率;二是缩短原材料从仓库到加工车间的时间,中间的临时小仓库,堆放目前专门生产的产品的原材料,可以大大缩短制造时间。小仓库相当于存储芯片中的DDR SDRAM,大仓库则相当于存储芯片中的Flash。

开发板上的DDR SDRAM用来保存用户程序在运行时使用到的数据。而Flash,负责存储应用程序等,就如电脑中的硬盘作用。

处理器,DDR SDRAM和Flash之间是如何进行数据传输的?

以运行用户程序为例,程序会以二进制码的形式存在Flash中。当想要运行某个用户程序时,处理器会先从Flash中读取待运行的程序放入DDR中。处理器与DDR实时进行数据传输,保证运行的速度。

开发板上的DDR SDRAM用来保存用户程序在运行时使用到的数据。

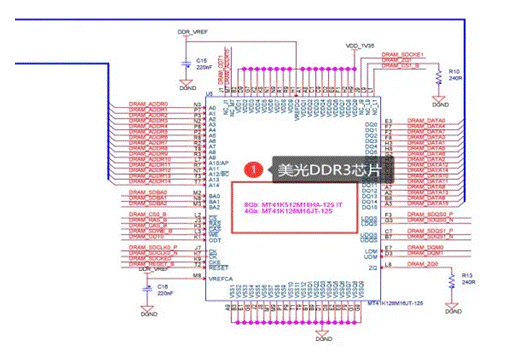

以美光的MT41K128M16JT-125 芯片(DDR3芯片)为例,速度可达800MHz的2GB DDR3 SDRAM。DDR3芯片的管脚较为复杂,不过大体上可以分成5类:电源线,时钟线地址线,数据线,控制线(在不同的容量芯片当中地址线和数据线的数目是变化的)。

下图的DRAM_ADDR[0:15],这是16根地址线,让处理器可以准确的访问DDR3芯片。然后是DRAM_DATA[0:15],我们可以看到16位的并行数据线,用于DDR3和处理器之间的数据传输。

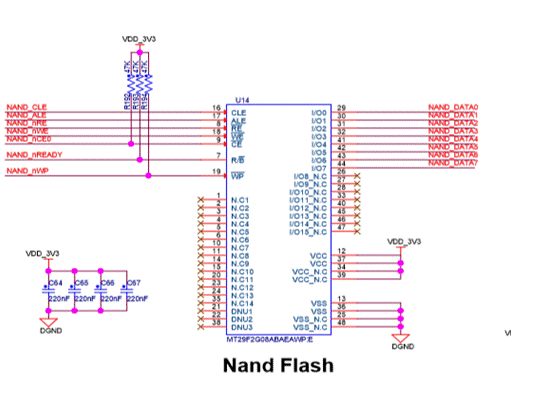

开发板上的Flash,负责存储应用程序等,就如电脑中的硬盘作用,直接与处理器相连。

以美光的MT29F2G08ABAEAWP芯片为例,这是一颗Nand Flash芯片虽然有48个管脚,但是实际上使用到的管脚也就十多个,比如有:

复用的数据管脚,用于数据、地址、命令等信息;CLE:命令锁存使能,在输入命令之前,先要拉高CLE;ALE:地址锁存使能,在输入地址之前,先要拉高ALE;CE#:芯片使能,在操作Nand Flash之前,先要拉低CE#;RE#:读使能,在读取数据之前,先要拉低RE#;WE#:写使能,在写取数据之前,先要拉低WE#;WP#:写保护,拉低WP之后,将无法对芯片进行写操作;R/B#:Ready/Busy Output,平时R/B为高电平状态,但当NAND进行编程、随机读或擦除操作时变为低电平状态,操作完成后又变为高电平状态。

处理器与Nand Flash芯片通过8 bit的并行总线进行连接,操作CLE和ALE,可以实现对8个IO管脚的数据类型复用。这样做有一个好处,就是可以大大简化的硬件电路的设计,避免了繁琐的硬件连线。同时,为了加强处理器对Nand Flash读写操作的稳定性,图中CE,R/B和WP三个控制管脚被电阻上拉到高电平。

NAND Flash的操作通过一系列的命令来完成。命令一共分成9大类,包括复位操作、识别操作、配置操作、状态操作、地址操作、读操作、写(编程)操作、擦除操作以及写回操作。

最先进的DDR5时代已来

工程师们执着于增加电子产品的运行速度及存储空间,使得开发板上的存储芯片容量正不断增加。决定电子设备性能的核心除了处理器之外,存储芯片的读取速度也成为一个非常重要的因素。

迄今为止技术上最为先进的 DDR5 ,比上一代DDR4提升至少 85%,已经出现在工程师的手中了。

审核编辑:汤梓红

-

普中PZ6806开发板入门教程2023-06-09 1107

-

普中开发板原理图分享2023-05-15 1724

-

普中6开发板原理图2022-10-24 955

-

开发板的常见分类有哪些2022-01-25 10191

-

FPGA开发板中几种不同的存储器2020-10-09 4037

-

开发板是什么_开发板有什么用_开发板怎么用(使用步骤教程)2017-12-09 119628

-

fpga开发板用途,fpga开发板价格2017-10-23 4926

-

普中开发板原理图2017-07-04 3876

-

USB大容量存储开发板CPLD代码2016-06-07 670

-

嵌入式开发板_iTOP-4412开发板linux系统存储空间2016-02-29 826

-

stm32开发板开发板原理图2015-12-21 1923

-

高速SDRAM存储器接口电路设计(Altera FPGA开发板)2012-08-15 3648

-

USB大容量存储开发板带CPLD的代码D的源码2010-08-19 522

全部0条评论

快来发表一下你的评论吧 !