基于PXI总线的数据传输接口设计与实现方案

嵌入式设计应用

描述

使用PCI9054 提供的DMA 传输方式,并由其Local 端配置和启动DMA 传输来完成数字频谱数据的传输,达到用PXI 总线实现数字频谱分析仪与工控机的高速数据传输的目的。

随着无线通信业务的飞速发展,频谱资源显得越来越缺乏,而实际中像广播电视等频段的频谱利用率却并不高,提高频谱的利用率成为一种共识。认知无线电是一种按伺机方式充分利用频谱的共享频谱技术,因此可以用来提高频谱利用率。快速准确的数字频谱分析对认知无线电的频谱感知有非常重要的影响。在认知无线电系统中,数字频谱分析仪与下一级的处理模块的数据传输速率是制约认知无线电系统处理速度的一个瓶颈,因此需要选择一种高速稳定的数据传输接口技术。

本文利用 PXI 总线技术来实现数字频谱分析仪与下一级处理模块的数据传输接口。PXI是CompactPCI extend for Instrumentation 的简称,即面向仪器系统的PCI 扩展,由NI(美国国家仪器公司) 于1997 年10 月率先推出。它将CompactPCI 规范定义的PCI 总线技术发展为适合于工业控制、测量、数据采集和试验应用的电气、机械和软件规范,从而形成了新的虚拟仪器体系结构。PXI 总线是一种高性能的32 /64 位地址数据复用总线,支持突发传输,是一种坚固的基于PC 的测量和自动化平台, 它的数据传输速率的峰值于33 MHz、32 bit 的总线上可达132 MB/s; 于66 MHz、64 bit 的总线上则可高达528 MB/s,远高于GPIB (General-Purpose Interface Bus,通用接口总线)与VXI (VME bus eXtension for Instrumentation,面向仪器系统的VME 总线的扩展)接口的传输速率。基于PCI 总线发展而来的PXI 系统具有较好兼容性、存取延时小、成本低等优点。PXI 总线数据传输接口以其高传输速率和稳定可靠的传输性能得到了越来越广泛的应用。

PXI 总线协议比较复杂, 工程应用中一般采用两种方式, 一是采用FPGA(FieldProgrammable Gata Array,现场可编程门阵列)来设计控制接口, 缺点是控制接口难度较大、开发周期长、成本大; 二是采用接口芯片, 将复杂的PXI 总线接口转换为相对简单的用户接口, 用户只要设计转换后的总线接口。本文采用PXI 总线专用接口芯片PCI9054 来实现PXI总线的数据传输。

PCI9054 是PLX 公司提供的一款PCI 专用接口芯片,它兼容PCI V2.2 的协议规范。其内部结构图如图1 所示。由图可知,PCI9054 实现的是PCI Bus 端和Local Bus端的信号转换,使得Local Bus 端不需要进行复杂的PCI 协议逻辑的设计,只需要进行简单的数据传输逻辑的设计就能实现符合PCI 协议规范的信号生成。

传输方式、PCI Target 传输方式以及PCI DMA 传输方式。PCI Initiator 传输方式下,PCI9054 成为PCI Bus 端的主机,同时是Local Bus 端的从机,由Local Bus 端主动发起数据传输,PCI9054 被动后再主动向PCI Bus 发起传输。PCI Target 传输方式下PCI9054 的角色刚好与PCI Initiator 方式相反,成为PCI Bus端的从机以及Local Bus端的主机。而在PCI DMA方式下PCI9054同时是PCI Bus端和Local Bus 端的主机。在PCI9054 内部分别提供了这三种传输方式下的内部寄存器,方便设计者来对每一种传输方式进行配置。

PCI9054 的本地端支持可编程的特点,通过两个模式选择管脚MODE[1:0]来设置LocalBus 端分别工作在C 模式、J 模式、M 模式。这样可以使得PCI9054 的Local Bus 可以挂载不同类型的其他设备。

PCI9054 提供了两个独立的可编程DMA (Direct Memory Access,直接存储器存取) 控制器;每个通道均支持块和分散/集中的DMA 方式;在PCI 总线端支持32 位的数据位宽,时钟速率达到33MHz;本地端可以编程实现8、16 或32 位的数据宽度;传输速率最高可达132MB/s;本地总线端时钟最高可达50MHz 支持复用/非复用的32 位地址数据。

2 接口电路设计

PXI 总线接口电路的设计主要是对PCI9054 芯片的外围电路进行设计,主要包括四个部分:电源方案的设计、时钟方案的设计、EEPROM 电路的设计,Local 端的连线方案设计。

PCI9054 芯片的正常工作电压是3.3V,而在上位机的PXI 接口中,提供了三种电压,3.3V、5V 和12V,因此PCI9054 的供电完全可以由上位机来提供。设计中,可以增加一个外部电压的接入接口,方便开发过程中的调试。

PCI9054 芯片需要两个工作时钟,一个是PCI Bus 端的工作时钟,一个是Local Bus 端的工作时钟,这两个工作时钟是独立的,均需要外部逻辑输入。PCI Bus 端的工作时钟由上位机的PXI 接口提供,主要在PCB(Printed Circuit Board, 印刷电路板);布线的时候需要对该时钟线进行蛇形走线处理。Local Bus 端的工作时钟由晶振提供,本方案中采用50MHz 的晶振。

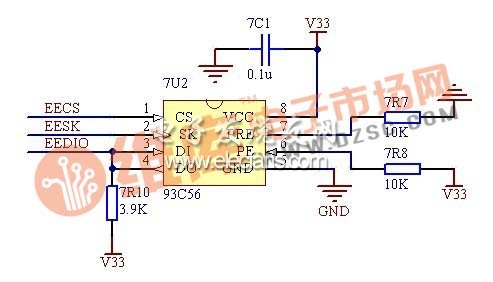

EEPROM 电路的设计中需要注意EEDI 和EEDO 两个管脚的连接,电路原理图如图2所示。注意在没有挂载Local 端的设备同时又没有EEPROM 时,EEDI 和EEDO 需要通过一个1KΩ的电阻拉低。设计中,往往需要加上一个EEPROM 用来存储对PCI9054 芯片的内部寄存器的设置。这些设置在每次上电时自动进行加载,对PCI9054 芯片的内部寄存器进行配置,使得每次上电后,PCI9054 能按事先所配置的方式工作。因此,在设计电路完成之后还需要对EEPROM 的内容进行设置,并通过PlxMon 工具写入。

图 2 EEPROM 电路设计原理图

在 Local 端的连线方案设计中,需要注意两点:一是本地时钟的接入,本地时钟作为PCI9054 识别Local 端是否有设备的依据,若在EEPROM 的EEDI 和EEDO 没有下拉的情况下,一定要接入本地时钟,不然连接上位机后,上位机进入不了系统。二是若需要用到PCI Initiator 传输方式,则必须将LBE[3:0]#全部拉低,否则就会造成读写出现上位机死机现象。

3 接口程序设计

由于数据传输接口涉及到数字频谱仪和上位机,其程序设计也包括两个部分:一部分是数字频谱仪端的程序设计,即PCI9054 Local 端的程序设计,由于本项目中在PCI9054 的Local端挂载的是FPGA 芯片,需要在FPGA 中进行Local 端的接口逻辑程序设计;另一部分是上位机端的程序设计,主要是基于操作系统的驱动程序以及上层应用程序设计。

3.1 FPGA 程序设计

FPGA 程序的设计主要是对PCI9054 的Local 端时序逻辑进行设计。由图2 可知,在PCI9054 内部的Local 端存在三种传输方式状态机:PCI Initiator 方式、PCI Target 方式、PCIDMA 方式。因此,在对Local 端的控制进行设计时,可以用不同的状态机来匹配PCI9054的内部状态机,达到实现各种方式的数据传输。

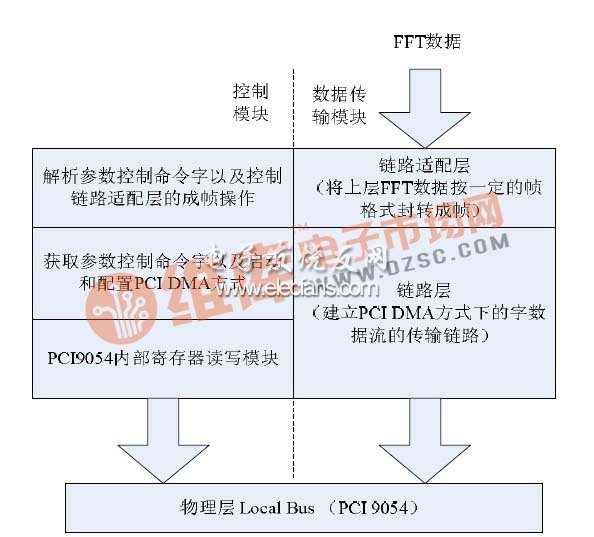

本文根据系统的特点,选择使用PCI DMA的传输方式。在FPGA端的程序采用层次化和模块化的设计,分为上下两层结构:下层是链路层,实现PCI DMA 方式下,长字(4Bytes)数据流的双向传输链路的建立;上层是链路适配层,实现数字频谱仪的数据按照一定的帧格式封转成帧。PCI DMA 方式的设置和启动也在FPGA 中完成,程序采用模块化的设计方式,将数据传输模块与控制模块区分。在控制模块中,分成三层:第一层是寄存器读写层,实现对PCI9054 内部寄存器的读写操作;第二层是参数获取与PCI DMA 方式配置层,实现从PCI9054 内部消息寄存器获取数字频谱仪的控制参数以及对PCI DMA 方式进行配置与启动控制;第三层是上层控制层,用来解析控制参数以及控制生成数据帧。整个程序结构图如图3 所示。

图3 FPGA程序结构图

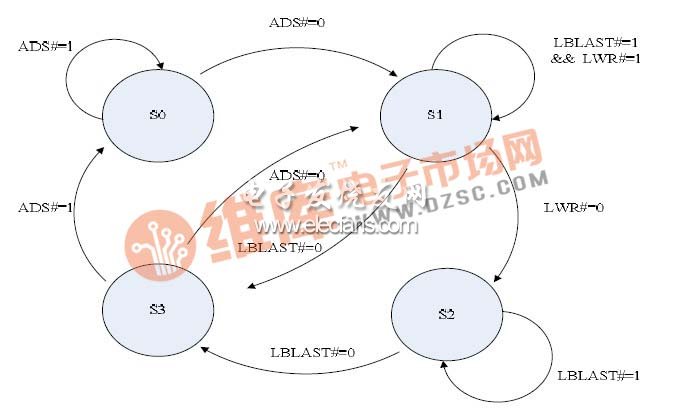

上述 FPGA 程序中主要包括了两个状态机的设计,一个PCI DMA 数据传输方式的状态机设计,一个是PCI 9054 内部寄存器读写操作的状态机设计。它们的状态转移图分别如图4和图5 所示。

图4 PCI DMA 数据传输状态转移图

图 4 中,S0 为空闲状态;S1 若在PCI9054 对Local Bus 进行写的操作中为数据接收状态,若在PCI9054 读Local Bus 的操作中为数据准备状态;S2 为PCI 9054 读Local Bus 的操作中的数据发送状态;S3 为读写操作的终止状态。图中各状态转移触发信号均为PCI 9054Local Bus 端的控制信号。

图 5 PCI 9054 内部寄存器读写操作的状态转移图

图 5 中,S0为空闲状态,在读写启动信号en_rwreg=1的情况下进入工作状态;S1为读写周期开始状态,有效Local Bus 端的读写周期开始信号;S2 为读写周期等待状态,等待PCI9054 的LREADY#有效;S3 为突发读写方式下的响应状态,突发读写方式下,PCI9054的LREADY#有效后,使能内部逻辑进行相应的响应;S4 为读写周期响应状态,在非突发读写方式下或者突发读写的终止周期中的响应状态。

在实现了上述两个状态机模块后,FPGA的程序还需要包括对FFT处理器的输出数据进行数据帧封装,即给每一次FFT 处理器根据相应的配置参数进行处理输出的数据加上帧头,帧头中包含了此次传输的FFT 数据所覆盖的频段以及数据的长度信息。这样做的好处是上位机不需要额外的同步信息,只需要根据帧头中的频段信息以及长度信息就可以判断当前数据帧所表示的频谱信息。利用PCI9054 内部寄存器中的MailBox 寄存器组来实现数字频谱仪与上位机之间的参数传递。由于数字频谱仪需要的参数信息比较少,只需要频段选择信息,以及开始和结束数字频谱仪的控制信号,选择MailBox 寄存器组中的第七个位宽为32 位的寄存器来传递控制信息。

整个 FPGA 程序的流程示意图如图6 所示。

图6 FPGA程序流程示意图

3.2 接口驱动程序的设计

接口驱动程序的设计可以通过两种方式实现,一种是通过专用的驱动程序开发工具进行驱动程序的设计,如DDK、DriverStudio 和WinDriver 等,另外一种方式是通过PLX 公司提供的PCI软件工具包SDK(Software Development Kit)实现接口的驱动设计,它提供了能够实现各种传输方式所需要的基本API 函数。

为了缩短开发周期,本文采用由PLX 公司提供的SDK 工具包进行驱动程序的开发。运用其SDK 提供的工作API 函数实现Block DMA 模式下的Burst Forever(无限突发)方式的数据传输。主要用到的函数如表1 所示。

由于本系统的特殊应用,还需要增加一些上层的应用程序,才能实现整个数字频谱仪数据的正常工作,主要包括数字频谱仪的参数控制字的生成和写PCI9054 内部寄存器MailBoxReg7,以及对接收的数据帧进行解封装的相关程序开发。

表1 Block DMA 模式下的SDK API 函数应用列表

本文使用了 PCI9054 的DMA传输方式,并且在Local端发起DMA传输,在上位机上采用中断的形式进行响应,可以减少占用上位机CPU 处理时间,使得上位机在进行数据传输的同时可以进行其他的操作。PXI 接口加上PCI9054 的开发模式,使得开发周期缩短了很多,避免了复杂的PXI 总线协议的逻辑设计和验证工作。本系统采用的PXI 总线的传输位宽32 位,采用无限突发的传输方式,在数据传输周期中的数据传输速率为132MB/s,但是由于增加了额外的控制周期以及其他的一些控制逻辑,使得数据的平均传输速率并没有达到这个值,但是完全可以匹配目前FFT 处理器的处理速率,可以保证数据传输的实时性。

-

CAN总线数据传输速率设置2024-11-12 3905

-

医疗设备CAN/CANopen总线数据传输解决方案2024-03-18 3399

-

DMA进行数据传输和CPU进行数据传输的疑问2023-05-25 1175

-

光纤接口转为以太网接口数据传输系统的实现方法2022-02-09 7391

-

怎样去设计RS-485远距离通信接口和数据传输接口?2021-06-03 1527

-

汽车行驶记录仪的数据传输设计2018-12-04 2735

-

SPI总线接口实现数据传输的实现方法2017-11-16 903

-

基于1553B总线的数据传输设计方案2017-11-11 1368

-

一种基于双层总线架构的数据传输方案_陈瑾2017-03-19 728

-

SOPC实现的PCI总线高速数据传输系统2012-02-10 1703

-

基于PCI总线的数据传输系统2011-04-25 1985

-

基于USB2.0的红外数据传输系统的设计与实现2010-03-13 1912

-

基于USB接口的无线数据传输系统设计2009-09-24 820

-

PCI总线高速数据传输系统设计2009-09-21 933

全部0条评论

快来发表一下你的评论吧 !