LWIP物理接口实现的设计方案

接口/总线/驱动

描述

介绍

LWIP(Lightweight IP)是一个轻量级的开源TCP/IP协议栈,它专为嵌入式系统和小型设备而设计。LWIP旨在提供TCP/IP网络协议支持,使嵌入式系统能够与其他设备通过网络进行通信

LWIP特点:

- 轻量级:LWIP被设计为占用较少的内存和处理器资源,使其能够在嵌入式系统中高效运行。

- 可裁剪性:LWIP允许根据具体需求进行裁剪,只包含必要的协议和功能,以减小存储空间和处理器开销。

- 高性能:LWIP使用了一些性能优化技术,如零拷贝和事件驱动机制,以提高网络通信的效率和吞吐量。

- 可移植性:LWIP具有良好的可移植性,可以在多种操作系统和硬件平台上运行。 支持多种应用层协议:除了TCP/IP协议栈,LWIP还提供了一些常用的应用层协议实现,如HTTP、SNMP和MQTT。

以太网简介

STM32中可以通过以太网按照 IEEE 802.3-2002 标准发送和接收数据。以太网提供了可配置、灵活的外设,用以满足客户的各种应用需求。它支持与外部物理层(PHY) 相连的两个工业标准接口:默认情况下使用的介质独立接口 (MII)(在 IEEE 802.3 规范中定义)和简化介质独立接口 (RMII)。

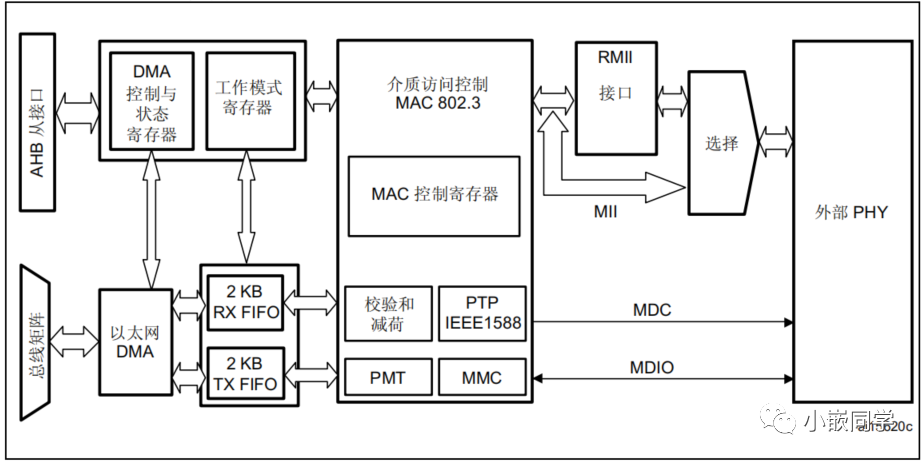

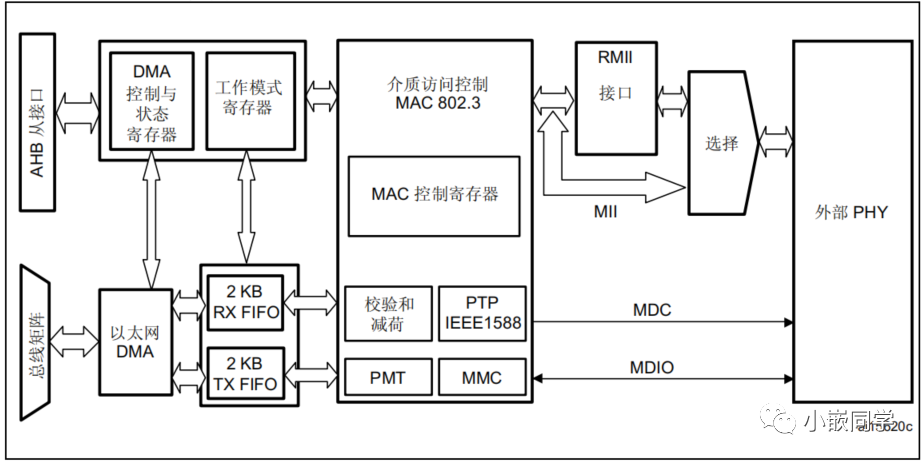

stm32 以太网框图

当进行发送数据的时候,首先系统存储器以DMA的方式发送至发送FIFO(Tx FIFO)进行缓冲,再通过MAC内核进行发送。同样,接收 FIFO (Rx FIFO) 则存储通过线路接收的以太网帧,直到这些帧通过 DMA 传送到系统存储器。

以太网外设还包括用于与外部 PHY 通信的 SMI。通过一组配置寄存器,用户可以为 MAC 控 制器和 DMA 控制器选择所需模式和功能。

上面的主要需要分析的模式是:MAC内核、RMII/MII介质接口、外部的PHY.

MAC内核

MAC内核是以太网控制器的关键组件,负责处理以太网帧的发送、接收、解析、封装、错误检测和流控制等功能。它与PHY层紧密协作,实现了STM32F4微控制器与以太网之间的可靠数据通信。

- 帧处理:MAC内核负责处理以太网数据帧的发送和接收。它与PHY层进行接口连接,将主机发送的数据封装为以太网帧并发送到网络上,同时从网络接收数据帧并传递给主机进行处理。

- 帧解析和封装:MAC内核负责解析接收到的以太网帧,提取其中的目标MAC地址、源MAC地址、帧类型和数据等信息。同时,它也负责封装主机发送的数据为以太网帧,添加必要的控制信息。

- 错误检测和处理:MAC内核执行帧的校验和错误检测。它会验证接收到的帧的完整性和正确性,通过校验和字段检查是否存在错误。如果帧出现错误或校验失败,MAC内核会丢弃或丢弃该帧,并通知主机。

- 帧的重传和丢弃:MAC内核负责处理发送失败或接收错误的情况。在发送时,如果未收到帧的确认响应或检测到冲突,MAC内核会触发重传机制。在接收时,如果帧出现错误或无效,MAC内核会丢弃该帧并通知主机。

- 帧流控制:MAC内核支持流控制机制,用于控制数据帧的发送速率。它可以根据接收端的缓冲区状态和网络流量情况,自动调整发送速率,以避免数据丢失或网络拥塞。

上面是MAC内核功能的描述,了解一下即可。我们主要是要关注Mac内核与PHY的物理接口看MAC是如何管理PHY.

站管理接口:SMI

描述

站管理接口(Station Management Interface,SMI)是用于与物理层(PHY)设备进行通信和配置的接口。SMI接口提供了主机(STM32)与PHY设备之间的通信通道,使得主机能够控制和监控PHY设备的操作。主要功能如下:

- 寄存器访问:通过SMI接口,主机可以读取和写入PHY设备的寄存器。这些寄存器包含了控制PHY设备功能和配置参数的信息。主机可以通过读取和写入寄存器的值来配置PHY设备的工作模式、速度、双工模式等。

- PHY设备配置:主机可以使用SMI接口来配置PHY设备的各种参数。通过读取和写入寄存器的值,主机可以设置PHY设备的工作模式、速度、自动协商等。这样可以适应不同的网络环境和需求。

- 状态查询:通过SMI接口,主机可以查询PHY设备的状态信息。主机可以读取PHY设备的状态寄存器,以获取连接状态、速度状态、工作模式等信息。这些状态信息可以帮助主机监测网络连接和PHY设备的工作状态。

- 错误处理:SMI接口还提供了错误处理的能力。主机可以读取PHY设备的状态寄存器以检测错误标志,并根据错误类型采取适当的措施。例如,重新配置PHY设备、进行错误恢复等,以确保网络通信的可靠性。

主要是关注SMI对PHY设置:如工作模式、速度、双工模式、自动协商设置。

SMI 站管理接口

如上图,SMI与PHY硬件接口由两根组成:MDC[时钟线]、MDIO[数据线]。通过这两根线可以访问多达32个PHY。SMI可以从 32 个 PHY 中选择一个 PHY 。PHY里面包含了一个 32 个寄存器。这个寄存器中主要是对发送数据进行控制\\接收状态信息。任意时间只能访问一个PHY。它的帧结构如下。

帧格式

- 报头:SMI帧以4个报头字节(0xFFFFFFFF)开始,在发送\\写入操作时,用于主机与PHY设备的之间建立同步通信。

- 起始:帧起始由 [01] 模式定义,用于验证线路从默认逻辑“1”状态变为逻辑“0”状 态,然后再从逻辑“0”状态变为逻辑“1”状态。

- 操作:定义正在发生的事务(读取[10]或写入[01])的类型。

- PHY地址:PHY 地址有 5 位,可构成 32 个唯一 PHY 地址。最先发送和接收地址的 MSB 位。

- 寄存器地址:寄存器地址有 5 位,从而可在所选 PHY 设备中对 32 个不同的寄存器进行寻 址。最先发送和接收地址的 MSB 位。

- TA:周转字段在 RADDR 和 DATA 字段间定义了一个 2 位模式,以避免在读取事务期间 出现竞争现象。读取事务时,MAC 控制器将 TA 的 2 个位驱动为 MDIO 线上的高阻态。 PHY 设备必须将 TA 的第一位驱动为高阻态,将 TA 的第二位驱动为“0”。 写入事务时,MAC 控制器针对 TA 字段驱动 [10] 模式。PHY 设备必须将 TA 的 2 个位 驱动为高阻态。

- 数据:数据字段为 16 位。最先发送和接收的位必须为 ETH_MIID 寄存器的位 15。

- 空闲:MDIO 线驱动为高阻态。三态驱动器必须禁止,PHY 的上拉电阻使线路保持逻辑 “1”状态。

写操作

当应用程序将 MII 写入位和繁忙位置 1 时,SMI 将通过传输 PHY 地址、PHY 中的寄存器地址以及写入数据。来触发对 PHY 寄存器进行写操作。事务进行期间, 应用程序不能更改 MII 地址寄存器的内容或 MII 数据寄存器。在此期间对 MII 地址寄存器或 MII 数据寄存器执行的写操作将会忽略(繁忙位处于高电平状态),事务将无错完成。写操 作完成后,SMI 将通过复位繁忙位进行指示。

写操作

读操作

当用户将以太网 MAC MII 地址寄存器 (ETH_MACMIIAR) 中的 MII 繁忙位置 1、MII 写入位清 零时,SMI 将通过传输 PHY 地址和 PHY 中的寄存器地址在 PHY 寄存器中触发读操作。事 务进行期间,应用程序不应更改 MII 地址寄存器的内容或 MII 数据寄存器。在此期间对 MII 地址寄存器或 MII 数据寄存器执行的写操作将会忽略(繁忙位处于高电平状态),事务将无 错完成。读操作完成后,SMI 将复位繁忙位,然后用从 PHY 中读取的数据更新 MII 数据寄存器。

读操作

时钟选择

MAC 启动管理写/读操作。SMI 时钟是一个分频时钟,其时钟源为应用时钟(AHB 时钟)。 分频系数取决于 MII 地址寄存器中设置的时钟范围。

时钟选择

介质接口

上面我们提到过一个MII的概念。MII其实就是一种介质接口。STM32除了MII介质接口外还有RMII介质接口。介质接口是配合SMI对PHY进行控制的。比如:SMI什么时候发数据、什么时候收数据、发写操作帧还是发读操作帧都是需要介质接口上的寄存器的值进行控制的。为此,MAC内核与PHY的物理接口其实就是SMI+RMII/MII 组成,后面分析都是基于这两者结合体。

介质独立接口:MII

介质独立接口 (MII) 定义了 10 Mbit/s 和 100 Mbit/s 的数据传输速率下 MAC 子层与 PHY 之间的互连。

介质独立接口信号

- TX_CLK:连续时钟信号。该信号提供进行 TX 数据传输时的参考时序。标称频率为: 速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。

- TXD(Transmit Data):TXD信号是主机向PHY设备发送数据的并行输出信号。主机通过TXD线将以太网帧的数据发送给PHY设备。

- TX_EN:发送使能信号。该信号必 须与报头的前半字节进行同步 (MII_TX_CLK)

- RX_CLK:连续时钟信号。该信号提供进行 RX 数据传输时的参考时序。标称频率 为:速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。

- RXD[3:0]:数据接收信号。该信号是 4 个一组的数据信号。

- RX_ER:接收错误信号。该信号必须保持一个或多个周期 (MII_RX_CLK),从而向 MAC 子层指示在帧的某处检测到错误。

- RX_DV:接收数据有效信号。该信号表示 PHY 当前正针对 MII 接收已恢复并解码的半字节。

- CRS:载波侦听信号。当发送或接收介质处于非空闲状态时,由 PHY 使能该信号。

- COL:冲突检测信号。检测到介质上存在冲突后,PHY 必须立即使能冲突检测信号, 并且只要存在冲突条件,冲突检测信号必须保持有效状态。该信号无需与 TX 和 RX 时 钟保持同步。在全双工模式下,该信号没意义。

- MDIO(Management Data Input/Output):MDIO信号用于主机与PHY设备之间的管理数据的双向传输。主机通过MDIO信号线向PHY设备发送配置和控制命令,并从PHY设备读取状态和配置信息。

- MDC(Management Data Clock):MDC信号是MDIO信号的时钟信号,用于同步MDIO数据的传输。MDC信号的频率由主机控制,用于提供时序同步。

TX 接口信号编码

RX 接口信号编码

MII时钟源

要生成 TX_CLK 和 RX_CLK 时钟信号,必须向外部 PHY 提供 25MHz 时钟,如下图示。除了使用外部 25 MHz 石英晶体提供该时钟,还可以通过 STM32F4xx 微控制器的 MCO 引脚输出该信号。这种情况下,必须对 PLL 倍频进行配置,以通过 25 MHz 外部石英晶体在 MCO 引脚上获得所需频率。

精简介质独立接口:RMII

精简介质独立接口 (RMII) 规范降低了 10/100 Mbit/s 下微控制器以太网外设与外部 PHY 间的 引脚数。根据 IEEE 802.3u 标准,MII 包括 16 个数据和控制信号的引脚。RMII 规范将引脚 数减少为 7 个(引脚数减少 62.5%)。

RMII 接口是 MAC 和 PHY 之间的实例化对象。这有助于将 MAC 的 MII 转换为 RMII。RMII 具有以下特性:

- 支持 10-Mbit/s 和 100-Mbit/s 的运行速率

- 参考时钟必须是 50 MHz

- 相同的参考时钟必须从外部提供给 MAC 和外部以太网 PHY

- 它提供了独立的 2 位宽(双位)的发送和接收数据路径

RMII时钟源

时钟源方案

MII与RMII除了在IO接口不同外,还存在着发送位宽的不同。介质MII接口一个周期发送位宽位4位,RMII的是2位。但是由于他们发送周期不同。如果在相同的时间内,RMII发送了两次而MII发送了一次。所以最终的速率是一样的。

PHY

描述

上面分析的过程中,我们知道了。Mac内核的数据最终,是通过PHY发送出去的。那么PHY是什么?这里主要是对LAN8720A这款PHY进行分析。如下图就是LAN8720A的内部框图

LAN8720A内部框图

PHY在计算机网络中起着关键作用,负责将数字数据转换为物理信号,并在物理介质上进行可靠的传输。它处理信号的编码、调制、传输和解调过程,同时支持时钟同步、错误检测和纠正,以及自动协商功能。PHY的正确操作和配置对于实现高速、可靠的数据通信至关重要。

LAN8720A

PHY内部包含了32个寄存器,都是通过MAC的SMI上的MDC与MDIO这两根线进行PHY的寄存器的读写。上面我们知道我们主要是通过这两根线实现PHY的速度与双工模式确定。

LAN8720A的32个内部寄存器如下

LAN8720A内部寄存器

而控制双工模式以及速度的模式主要存在于第3 1个寄存器也称为BCR寄存器,其寄存器设置如下。

双工与模式设置寄存器

如下图是前面提及的MDIO数据帧格式

对于2:4字段。最高位为1的时候表示是全双工、0的时候表示半双工。第二第三位代表的速度。01 表示10Mbit/s、10表示100Mbit/s如果我想把当前的第一个PHY假如为0x00[有多个PHY]设置为100Mbit/s 与全双工模式。该如何操作?

首先,确定时PHY的地址。那么PHY的地址就是0x00。接下来就是寄存器的地址,这里的寄存器是最后一个寄存器地址:0x1F.最后是数据位:100Mbit/s 全双工。对应上面表的110,所以数据位为0000000000011000.

MAC 802.3 帧格式

上面的分析其实都是在物理层于数据链路层的内容。既然是在物理层那么就应该有物理层的数据帧结构标准。这个帧标准就是MAC 802.3 帧格式。这个帧结构分为:有标记MAC帧格式与无标记MAC帧结构

无标记MAC帧格式

- 报头:MAC帧以7个字节的报头(10101010...)开始,用于同步接收方的时钟。

- 帧起始定界符(Start Frame Delimiter,SFD):紧接着前导码是一个字节的SFD(10101011),用于标识帧的起始。

- 目标MAC地址(Destination MAC Address):6个字节,指示数据帧的目标设备的MAC地址。该字段唯一标识了数据帧的接收方。

- 源MAC地址(Source MAC Address):6个字节,指示数据帧的发送设备的MAC地址。该字段唯一标识了数据帧的发送方。

- 长度/类型(Length/Type):2个字节,指示数据字段的长度或指示数据字段的类型。当长度小于等于1500时,它指示了上层协议类型。

- 数据字段(Data):46-1500个字节,包含了上层协议(如IP或ARP)传输的数据。

- 帧校验序列(Frame Check Sequence,FCS):4个字节,用于检测数据帧在传输过程中是否发生了错误。FCS字段使用循环冗余校验(CRC)算法计算得出。

带标记的 MAC 帧格式

带标记的MAC帧格式和不带标识符的MAC帧之间的区别在于是否包含了标识符字段。下面是它们的区别:

- 带标记的MAC帧格式(Tagged MAC Frame):带标记的MAC帧格式是在不同的网络技术中使用的一种扩展帧格式。它包含了一个额外的标识符字段,用于标记帧所属的虚拟局域网(VLAN)。标识符字段是一个特定的VLAN标签,用于将帧与相应的VLAN关联起来。带标记的MAC帧格式通常用于实现虚拟局域网的划分和管理。

- 不带标识符的MAC帧格式(Untagged MAC Frame):不带标识符的MAC帧格式是最常见的以太网帧格式,也被称为普通以太网帧格式。它不包含额外的标识符字段,只包含了目标MAC地址、源MAC地址、长度/类型、数据字段和帧校验序列。不带标识符的MAC帧格式适用于普通的以太网通信,不涉及虚拟局域网的划分和管理。

以太网DMA描述符

如下框图,已经分析了MAC内核、PHY。而最后我们需要对以外网DMA与TxFiFo、RxFiFo 这部分进行分析。

stm32 以太网框图

以太网DMA控制器操作过程:

DMA 具有独立的发送和接收引擎以及相应的 CSR(控制和状态寄存器)空间。发送引擎将 数据从系统存储器传送到 Tx FIFO,而接收引擎将数据从 Rx FIFO 传送到系统存储器。DMA 可以在 CPU 完全不干预的情况下,通过描述符有效地将数据从源传送到目标。DMA 专为面 向包的数据传送(如以太网中的帧)而设计。该控制器经过编程后,可在完成帧发送和接收 传送操作时以及其它正常/错误条件下产生 CPU 中断。DMA 和 STM32通过以下两种数 据结构进行通信:

- 控制和状态寄存器 (CSR)

- 描述符列表和数据缓冲区。

什么是以太网DMA描述符

DMA 既可将接收到的数据帧传送到 STM32F4xx 存储器中的接收缓冲区,也可以传送 STM32 存储器的发送缓冲区中的数据帧。位于 STM32F4xx 存储器中的描述符用作指向这些缓冲区的指针。共有两个描述符列表:一个用于接收,一个用于发送。两个列表的基址分别写入 DMA 寄存器 3 和寄存器 4。最后一个描述符会指回第一个描述符以构成环形结构。可通过配置接收和发送描述符 (RDES1[14] 和 TDES0[20])中链接的第二个地址来完成描述符的显式链接。

简单来说就是TxFiFo与RxFiFo缓冲区内存的管理是通过链表实现。不然怎么叫FIFO先入先出不就是一个队列数据结构嘛。

DMA 既可将接收到的数据帧传送到 STM32F4xx 存储器中的接收缓冲区,也可以传送 STM32 存储器的发送缓冲区中的数据帧。位于 STM32F4xx 存储器中的描述符用作指向这些缓冲区的指针。

描述符

描述符主要分两种:常规描述符、增强描述符

常规描述符:管理缓冲区常规描述符:在常规描述符基础上开启时间戳和 IPv4校验和减荷这里主要分析常规的描述符,其结构框图如下

常规 Tx DMA 描述符

其中需要比较注意的位为

- TDES0[31]置0:CPU可将数据拷贝到描述符中,拷贝完成之后把该位置1,告诉DMA可以发送数据

- TDES0[20]置1:描述符中的第二个地址是下一个描述符地址

- TDES1[28:16]:如果TDES0[20] 位置1,则该字段无效

- TDES3[31:0]:取决于TDES0[20]的值,为1,则指向下一个描述符地址

常规 Rx DMA 描述符结构

- RDES0[31]置1:MAC将数据从RX FIFO传输到RX描述符中,拷贝完成之后该位置0,告诉CPU可以接收数据

- RDES0[14]置1:描述符中的第二个地址是下一个描述符地址

- RDES1[28:16]:如果RDES0[14]位置1,则该字段无效

- RDES3[31:0]:取决于RDES0[14]的值,为1,则指向下一个描述符地址

描述符结构

其中根据RES3/TDES3字段来判断是什么结构,如果是指向下一个缓冲区地址那么就是链接结构,如果是第二个缓冲区就是1环形结构。

-

利用I2C通信接口实现测温的设计方案2015-10-13 5259

-

使用正常的window API接口实现的程序连接上服务器就断开了2019-07-04 1961

-

分享!基于Zynq-7010/7020的多路千兆网口实现方案2021-10-22 8347

-

如何使用编码器接口实现定位?2022-02-11 1354

-

利用Ethernet通信接口实现在应用编程的解决方案2022-12-01 645

-

如何使用AT32F407以太网通信接口实现在应用中编程(IAP)的解决方案2023-10-24 616

-

如何使用AT32F437以太网通信接口实现在应用中编程(IAP)的解决方案2023-10-25 745

-

Lwip协议栈的设计方案2011-09-16 855

-

基于FPGA的VGA接口实现和字符显示2015-10-29 1253

-

ARM与FPGA的接口实现的解析2021-07-22 1205

-

C#-Interface接口实现2021-09-28 791

-

通过标准的CAN接口实现的测试台自动化解决方案2022-10-11 3103

-

AN3384_基于microcontrollers接口的LwIP在应用编程实现2022-11-24 466

-

基于FreeRTOS+LwIP的SNMP实现方案V02022-10-18 963

-

基于XML语言描述的接口实现方法2023-11-06 459

全部0条评论

快来发表一下你的评论吧 !