STM32的FSMC外设简介

电子说

描述

01

FSMC特点

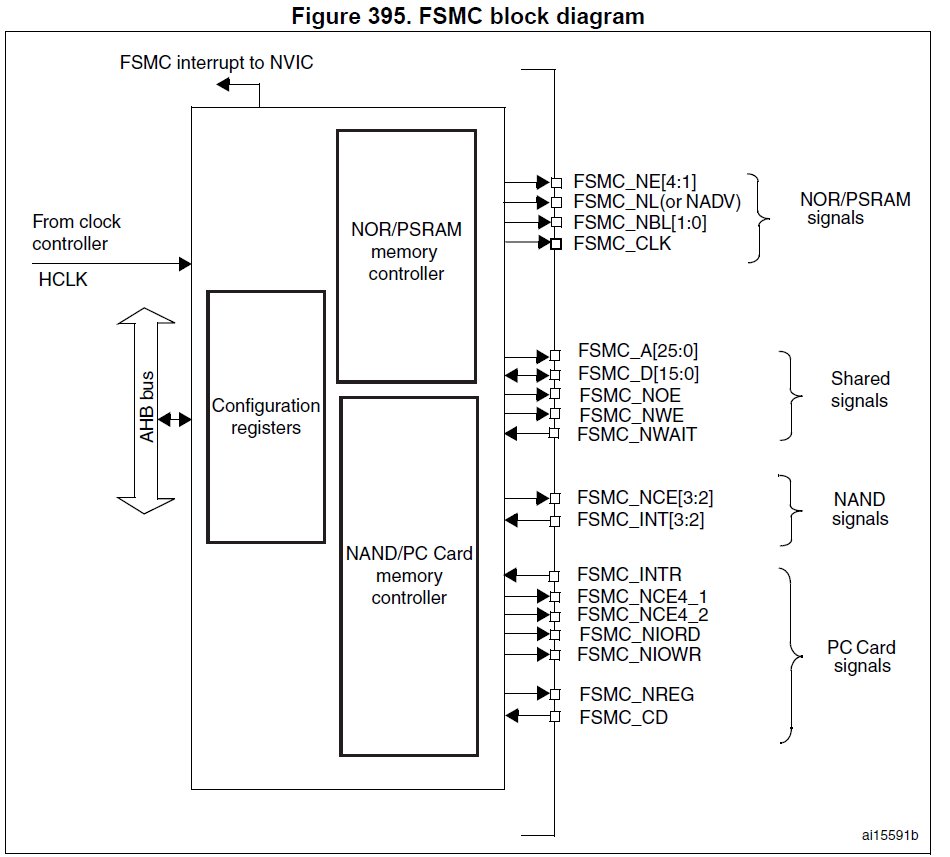

Flexible static memory controller(FSMC)灵活的静态存储控制器。FSMC可以连接异步或同步存储器或16位PC存储卡,主要用途有:

- 将 AHB 数据通信事务转换为适当的外部器件协议

- 满足外部器件的访问时序要求

所有外部存储器共享地址、数据和控制信号,但有各自的片选信号。FSMC 一次只能访问一个外部器件。

FSMC,即灵活的静态存储控制器,能够与同步或异步存储器和16位PC存储器卡连接,STM32的FSMC接口支持包括SRAM、NANDFLASH、NORFLASH和PSRAM等存储器。

△FSMC框图示意

02

AHB接口

AHB设备接口可以使内部CPU和其他主总线外设去访问外部存储器。AHB事务可以传输外部设备协议。特别是当外部存储器被选择位8位或16位,32位的AHB传输传输事务会被划分为多个连续的8位或16的传输事务。片选会在每次访问时切换。

通用事务规则要求AHB传输数据宽度必须是8位、16位或32位。但是访问外部数据必须有个固定的数据宽度。这可能导致不一样的传输。

因此必须遵循一些简单的事务规则:

- AHB事务数据宽度必须和存储器数据宽度相同。在这种情况下不会出问题;

- AHB事务数据宽度大于存储器数据宽度,在这种情况下,FSMC会将AHB事务分为多个连续的存储器访问,这样符合外部存储器访问数据宽度;

- AHB事务数据小存储器宽度,在这种情况下,异步传输可能一致,也可能不一致,这取决于外部设备的类型。

对设备的异步访问要具有字节选择功能(SRAM,ROM,PSRAM),①FSMC 允许写入事务通过其字节选择通道 NBL[1:0] 访问恰当的数据,②允许读取事务。会读取所有存储器字节,并将丢弃无用的存储器字节。 NBL[1:0]在读取事务期间保持为低电平。

对不具有字节选择功能的器件( 16 位 NOR 和 NAND Flash)进行异步访问,当请求对 16 位宽的 Flash 存储器进行字节访问时会发生此情形。

显然,不能在字节模式下访问此器件(只能针对 Flash 存储器读取或写入 16 位字),因此①不允许写入事务,②允许读取事务。会读取所有存储器字节,并将丢弃无用的存储器字节。 NBL[1:0]在读取事务期间保持低电平。

03

外部设备地址映射

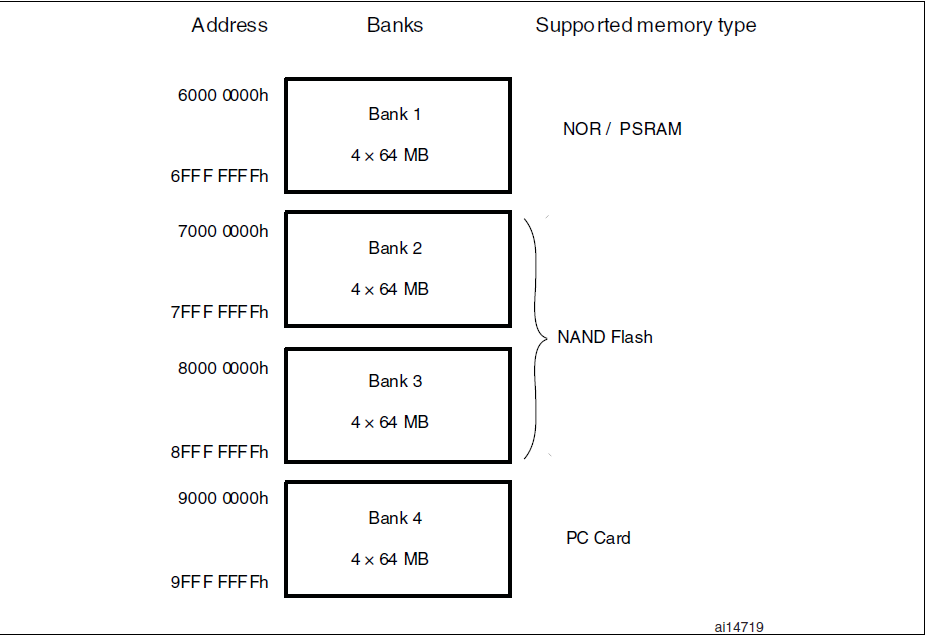

FSMC的外部设备地址映像,STM32的FSMC将外部存储器划分为固定大小为256M字节的四个存储块:

- 块1被用于4个NORflash或者PSRAM内存设备。块1被划分为4块NORflash/PSRAM带有独立的片选信号。

- 块2和块3用于连接NANDflash(一个块驱动一个设备)

- 块4用于连接PC块设备

对于每个存储区域,所要使用的存储器类型由用户在配置寄存器中定义

NOR/PSRAM地址映射

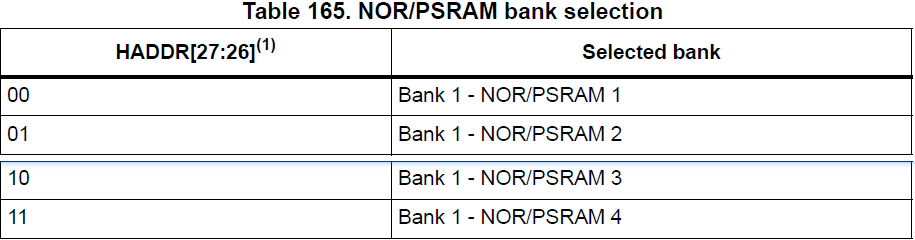

Bank1的256M字节空间由28根地址线(HADDR[27:0])寻址。这里HADDR,是内部AHB地址总线,但也会参与对外部存储器的寻址,其中,HADDR[25:0]来自外部存储器地址FSMC_A[25:0],而HADDR[26:27]对4个区进行寻址。如下表所示:

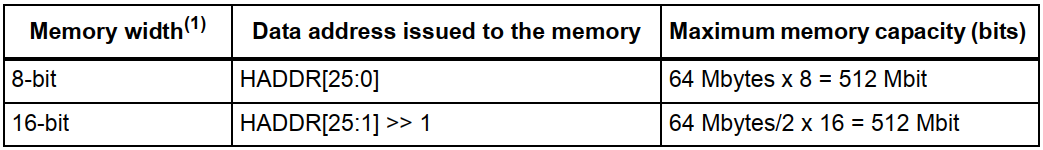

HADDR[25:0] 包含外部存储器地址。由于HADDR为字节地址,而存储器按字寻址,所以根据存储器数据宽度不同,实际向存储器发送的地址也将有所不同,如下表所示:

当Bank1接的是16位宽度存储器的时候:HADDR[25:1]->FSMC_A[24:0];

当Bank1接的是8位宽度存储器的时候:HADDR[25:0]->FSMC_A[25:0];

不论外部接8位/16位宽设备,FSMC_A[0]永远接在外部设备地址A[0]。

04

NOR/PSRAM控制器

FSMC 会生成适当的信号时序,以驱动以下类型的存储器

- 异步 SRAM 和 ROM,8位、16位或者32位

- PSRAM,异步模式,突发模式,复用或非复用

- NOR Flash,异步模式或突发模式,复用或非复用

FSMC每个块输出独立的片选信号NE[4:1]。其他信号(读,数据和控制)是共享的;

对于同步访问,FSMC仅仅在读写事务时给选择的外部设备发出时钟。HCLK时钟频率是该时钟的整数倍。每个块的大小固定64M字节。

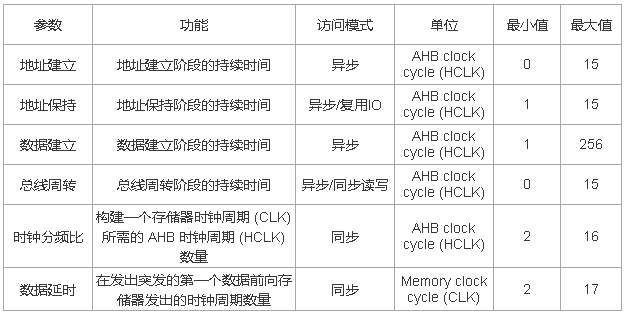

存储器的可编程参数包括访问时序(详见下图)和对等待管理的支持(用于在突发模式下访问NOR Flash 和PSRAM)。

NOR/PSRAM 的可编程访问参数

05

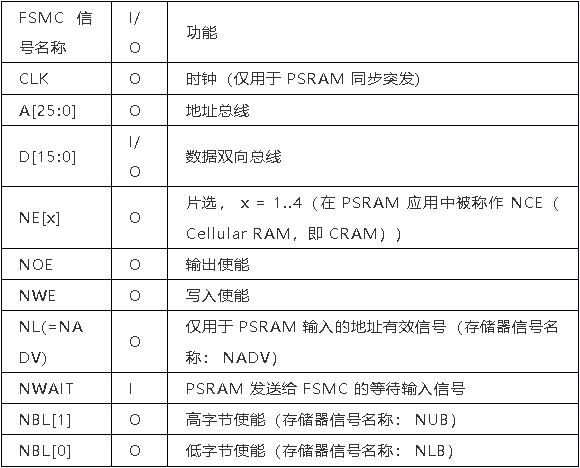

外部存储器接口信号

非复用 I/OPSRAM/SRAM

注意:前缀“N”表示相关的信号为低电平有效

06

NOR/PSRAM控制器异步事务

异步静态存储器(NOR Flash、PSRAM、SRAM)

- 信号通过内部时钟 HCLK 进行同步,不会将此时钟发送到存储器;

- FSMC 总是会先对数据进行采样,而后再禁止片选信号 NE。这样可以确保符合存储器数据保持时序的要求(数据转换的芯片使能高电平,通常最低为 0 ns。);

- 如果使能扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位置 1),则最多可提供四种扩展模式( A、 B、 C 和 D)。可以混合使用 A、 B、 C 和 D 模式来进行读取和写入操作。例如,可以在模式 A 下执行读取操作,而在模式 B 下执行写入操作;

- 如果禁用扩展模式(FSMC_BCRx 寄存器中的 EXTMOD 位复位),则 FSMC 可以在模式 1 或模式 2 下运行,如下所述①当选择 SRAM/CRAM 存储器类型时,模式 1 为默认模式( FSMC_BCRx 寄存器中MTYP = 0x0 或 0x01)②当选择 NOR 存储器类型时,模式 2 为默认模式( FSMC_BCRx 寄存器中 MTYP =0x10)

对于这5种模式,总结如下:

模式1/A:SRAM/PSRAM(CRAM)OE翻转,模式A与模式1的区别是NOE的变化和相互独立的读写时序。

模式2/B:NOR闪存,模式2/B与模式1相比较,不同的是NADV的变化,且在扩展模式下(模式B)读写时序相互独立。(只有当设置了扩展模式时(模式B),FSMC_BWTRx才有效,否则该寄存器的内容不起作用。)

模式C :NOR闪存- OE翻转,模式C与模式1不同的是,NOE和NADV的翻转变化,以及独立的读写时序;

模式D:带地址扩展的异步操作,模式D与模式1不同的是NADV的翻转变化,NOE的翻转出现在NADV翻转之后,并且具有独立的读写时序。

07

模式1

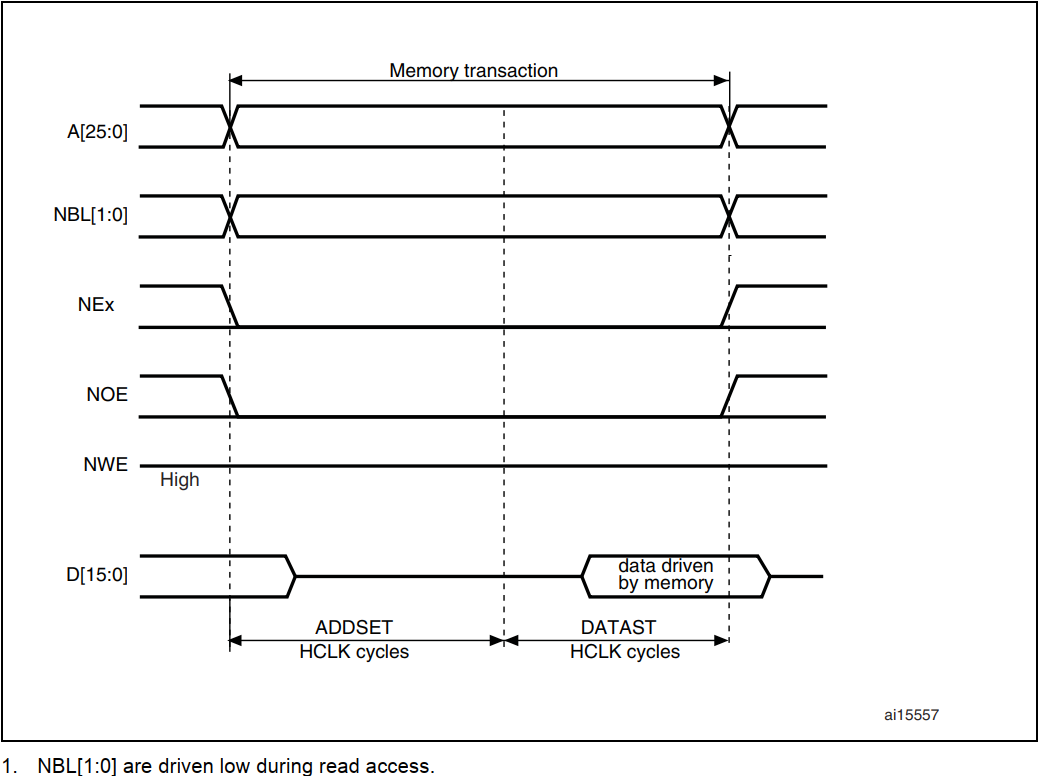

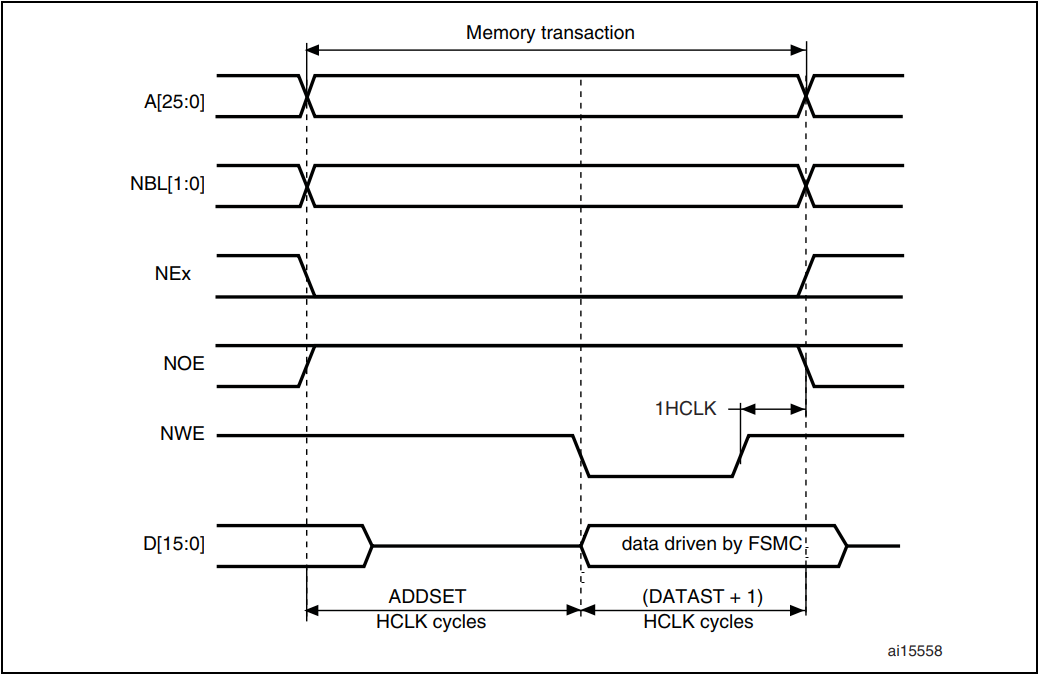

模式 1 -SRAM/PSRAM (CRAM)

下图显示了所遵循的受支持模式的读写事务通过配置FSMC_BCRx, and FSMC_BTRx/FSMC_BWTRx寄存器

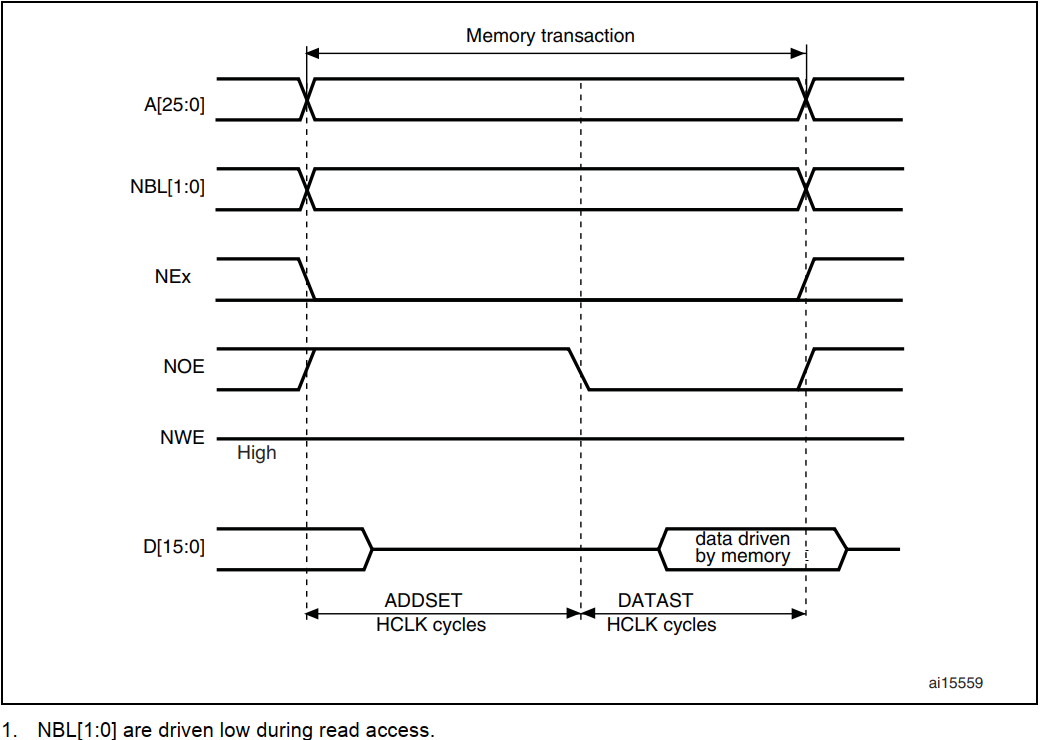

▽模式1读访问

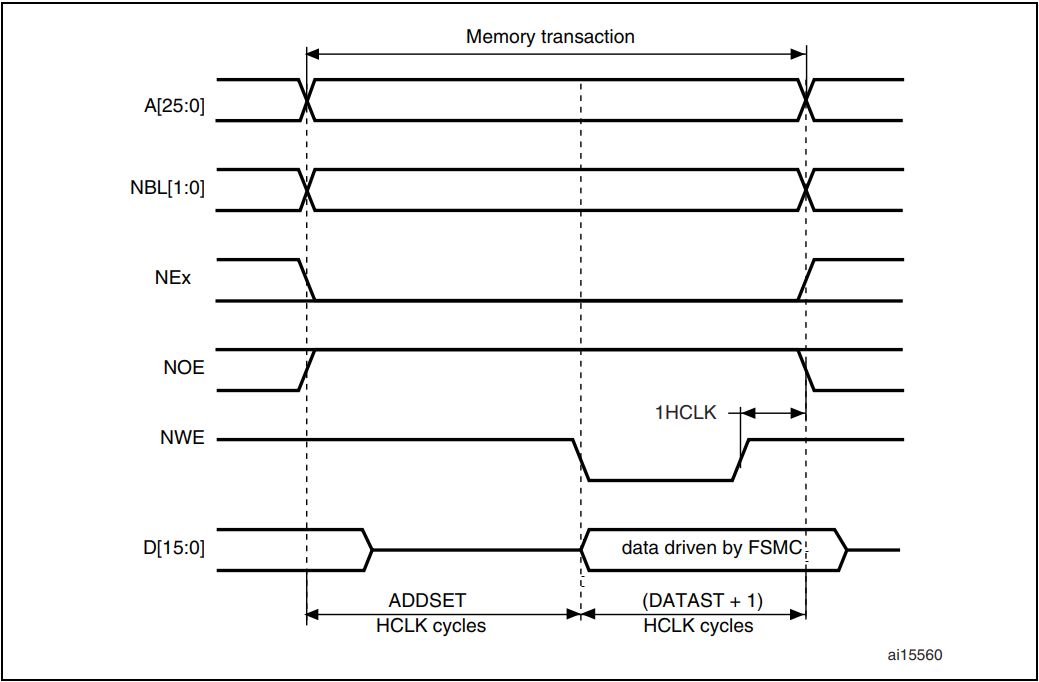

▽模式1写访问

位于写入事务末尾的一个HCLK 周期有助于确保NWE 上升沿之后的地址和数据保持时间。由于存在此HCLK 周期,DATAST 值必须大于零(DATAST > 0)。

08

模式A

模式 A -SRAM/PSRAM (CRAM) OE 切换

▽模式A读访问

▽模式A写访问

与模式1的不同之处在于NOE 的切换与独立的读取和写入时序

对于模式A,

ADDSET就是NWE的高电平时间,也就是地址建立时间

DATAST就是NWE的低电平时间,也就是数据保持时间

09

代码说明

readWriteTiming.FSMC_AddressSetupTime = 0x02; //地址建立时间(ADDSET)为2个HCLK 2*1/120M=16ns

readWriteTiming.FSMC_AddressHoldTime = 0x02; //地址保持时间(ADDHLD),16ns

readWriteTiming.FSMC_DataSetupTime = 0x06; //数据建立时间,50ns

readWriteTiming.FSMC_BusTurnAroundDuration = 0x00;//总线恢复时间

readWriteTiming.FSMC_CLKDivision = 0x00;// 时钟分频因子

readWriteTiming.FSMC_DataLatency = 0x00;//数据产生时间

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A; //模式A

FSMC_AddressSetupTime: 这些位定义地址的建立时间,适用于SRAM、ROM和异步总线复用模式的NOR闪存操作。

FSMC_AddressHoldTime : 这些位定义地址的保持时间,适用于SRAM、ROM和异步总线复用模式的NOR闪存操作。

FSMC_DataSetupTime: 这些位定义数据的保持时间,适用于SRAM、ROM和异步总线复用模式的NOR闪存操作。

F SMC_BusTurnAroundDuration: 这些位用于定义一次读操作之后在总线上的延迟(仅适用于总线复用模式的NOR闪存操作),一次读操作之后控制器需要在数据总线上为下次操作送出地址,这个延迟就是为了防止总线冲突。如果扩展的存储器系统不包含总线复用模式的存储器,或最慢的存储器可以在6个HCLK时钟周期内将数据总线恢复到高阻状态,可以设置这个参数为其最小值。

FSMC_CLKDivision : 定义CLK时钟输出信号的周期,以HCLK周期数表示。

FSMC_DataLatency: 处于同步成组模式的NOR闪存,需要定义在读取第一个数据之前等待的存储器周期数目。这个时间参数不是以HCLK表示,而是以闪存时钟(CLK)表示。在访问异步NOR闪存、SRAM或ROM时,这个参数不起作用。操作CRAM时,这个参数必须为0

FSMC_AccessMode : 访问模式

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1;// 这里我们使用NE1 ,也就对应BTCR[6],[7]。

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;// 不复用数据地址

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;// FSMC_MemoryType_SRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_8b;//存储器数据宽度为8bit

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait = FSMC_AsynchronousWait_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;// 存储器写使能

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;// 读写使用相同的时序

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming;//读写时序

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &readWriteTiming;//写时序

FSMC_Bank: nor被分为四块,其中这个参数是说明对那个块编程

FSMC_DataAddressMux: 地址\\数据是否复用

FSMC_MemoryType: 存储器类型

FSMC_MemoryDataWidth: 数据总线宽度8位/16位

FSMC_BurstAccessMode: 是否进行成组模式访问

FS MC_WaitSignalPolarity: 等待信号有效级性

FSMC_WrapMode: 该位决定控制器是否支持把非对齐的AHB成组操作分割成2次线性操作;该位仅在存储器的成组模式下有效。

FSMC_WaitSignalActive: 当闪存存储器处于成组传输模式时,NWAIT信号指示从闪存存储器出来的数据是否有效或是否需要插入等待周期。该位决定存储器是在等待状态之前的一个时钟周期产生NWAIT信号,还是在等待状态期间产生NWAIT信号。

FSMC_WriteOperation: 该位指示FSMC是否允许/禁止对存储器的写操作。

FSMC_WaitSignal: 当闪存存储器处于成组传输模式时,这一位允许/禁止通过NWAIT信号插入等待状态。

FSMC_ExtendedMode:该位允许FSMC使用FSMC_BWTR寄存器,即允许读和写使用不同的时序。

FSMC_WriteBurst: 对于处于成组传输模式的闪存存储器,这一位允许/禁止通过NWAIT信号插入等待状态。读操作的同步成组传输协议使能位是FSMC_BCRx寄存器的BURSTEN位。

FSMC_ReadWriteTimingStruct: 读时序配置指针

FSMC_WriteTimingStruct: 写时序配置指针

-

FPGA与STM32通过FSMC总线通信的实验2024-11-12 6406

-

TFT LCD与FSMC的硬件连接大容量STM32F10xxx FSMC接口2023-09-21 805

-

存储控制器FSMC与触摸屏介绍2023-07-27 6004

-

AN4761_通过STM32L476、486的FSMC外设驱动外部存储器2022-11-21 694

-

stm32_FSMC机制2022-02-21 939

-

STM32的FSMC详解2021-12-06 1995

-

STM32的CAN外设简介2021-08-19 1528

-

STM32是如何驱动LCD的2021-08-04 1774

-

STM32学习教程之FSMC模块2021-03-16 1335

-

基于FPGA和STM32的FSMC通信2018-07-28 12782

-

STM32接口中FSMC/FMC难点问题理解2018-04-19 18857

-

最全STM32外设资料汇总2017-12-08 30669

-

如何使用STM32的FSMC接口驱动LCD屏2016-09-22 2002

-

TFT_LCD与FSMC的硬件连接大容量STM32F10xxx_FSMC接口2016-01-08 1375

全部0条评论

快来发表一下你的评论吧 !