小伙手工制作了一款32位CPU

描述

一个国外小伙制造出了自己的CPU,从设计 CPU、制作原型机、最终成品到软件编程,19 岁极客小伙用了整整两年的时间。

RISC-V是一个基于精简指令集(RISC)原则的开源指令集架构(ISA),它是对应开源软件运动的一种「开源硬件」。该项目于 2010 年始于加州大学伯克利分校,项目贡献者是该大学以外的志愿者和行业工作者。

RISC-V 指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计。与大多数指令集相比,RISC-V 指令集可以自由地用于任何目的,允许任何人设计、制造和销售 RISC-V 芯片和软件。

2021年4月初,一位热衷于自制CPU的19岁极客小伙Filip Szkandera自己设计和制造出了32位功能性RISC-V CPU,并构建了与其他自制计算机不同的个人计算机,命名为菠萝一号(Pineapple ONE)。从设计、调试和安装CPU和所有硬件,Filip整整花了两年时间。Filip还受邀在东京举办的RISC-V Days Tokyo 2021 Spring上做了演示,他也成为了该会议自2017年举办以来最年轻的演示者,下图是创建者Filip Szkandera与他的作品。

整体来看,「菠萝一号」是由8块正方形打印电路板垂直堆叠组成,每块边侧高度约为10厘米,外加一个VGA显示接口卡。一共使用了230多个集成电路,大多数是74HCT系列逻辑芯片。

32 位 RISC-V CPU 的规格如下:

最大时钟速度:500kHz

程序内存:512kB

内存 512kB

闪存 512kB

VGA 输出:200×150px(黑白)

2 个 8 位输入端口

2 个 8 位输出端口

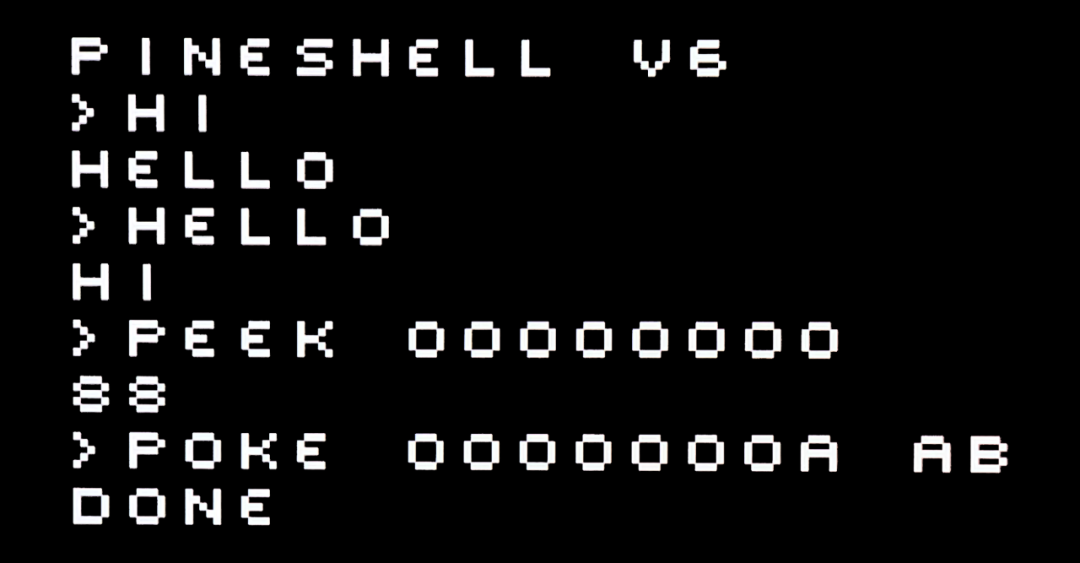

目前,「菠萝一号」计算机支持的命令包括:HELLO、HI、PEEK 《ADDRESS》、POKE 《ADDRESS》 《DATA》、SYSTEM INFORMATION、CLEAR 等。

此外虽然 CPU 的运行速度仅有 500kHz,但玩个贪吃蛇游戏还是绰绰有余的,贪吃蛇游戏界面如下。

Filip 在一篇博客中介绍了他从设计 CPU、制作原型机、输入 / 输出端口、最终成品到软件编程的技术细节。-

设计自己的 RISC-V CPU

此前,我在 Youtube 上发现了电子爱好者 Ben Eater 自制 CPU(构建著名的 8 位计算机和经典的 6502 微处理器)的相关教程,所以非常着迷,也就有了自制 CPU 的想法。然而,我觉得对于 CPU 基础知识了解的还不够,因此又观看了 Google Robotics 软件工程师 Robert Baruch 的教程视频,他只使用了基本逻辑元件构建了 32 位 RISC-V CPU。

之后,我便开始在一个名为「Logisim-Evolution」的项目中制造自己的 RISC-V CPU。我给自己设定的目标是不使用任何微控制器或 FPGA,只使用基本的分立逻辑元件。编译器支持的最基础 RISC-V CPU 必须包含扩展「整数(I)」且至少为 32 位。此外,我还需要安装一个 VGA(视频图形阵列)输出卡。

我花了整整 6 个月的时间在 Logisim 项目上,终于得到一个可运行的程序模拟。下一步绘制所有模块的原理图、从 JLCPCB 网站上购买所有的 PCB(印制电路板)并重新设计。由于这是我首次购买 PCB,担心搞砸一切,于是决定在设计过程中分模块处理,一次选购几个,以免自己应接不暇。

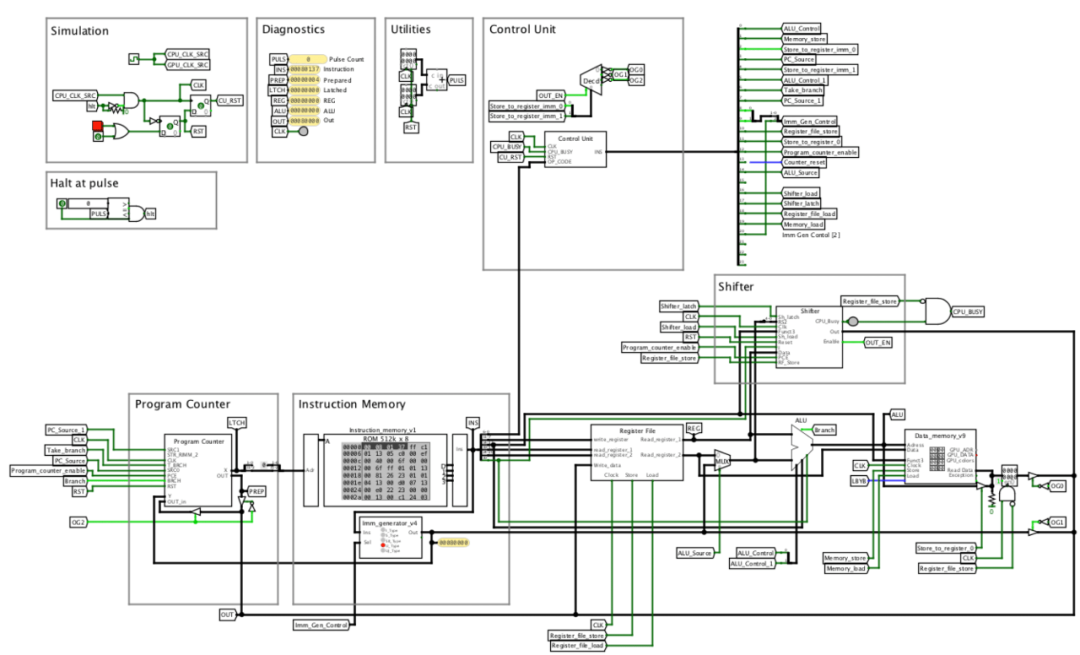

Logisim-Evolution 项目中的模拟原理图如下:

经过了两轮设计,最后只剩下几个模块需要处理,其中一个是直接生成器(immediate generator)。当我绞尽脑汁想将它从模拟转化为合适的原理图时,发现自己犯了一个致命错误:完全不清楚模拟是如何运行的。幸运的是,修复起来也没有那么困难,于是对已经制作完成的 PCB 做了改进。

原型机

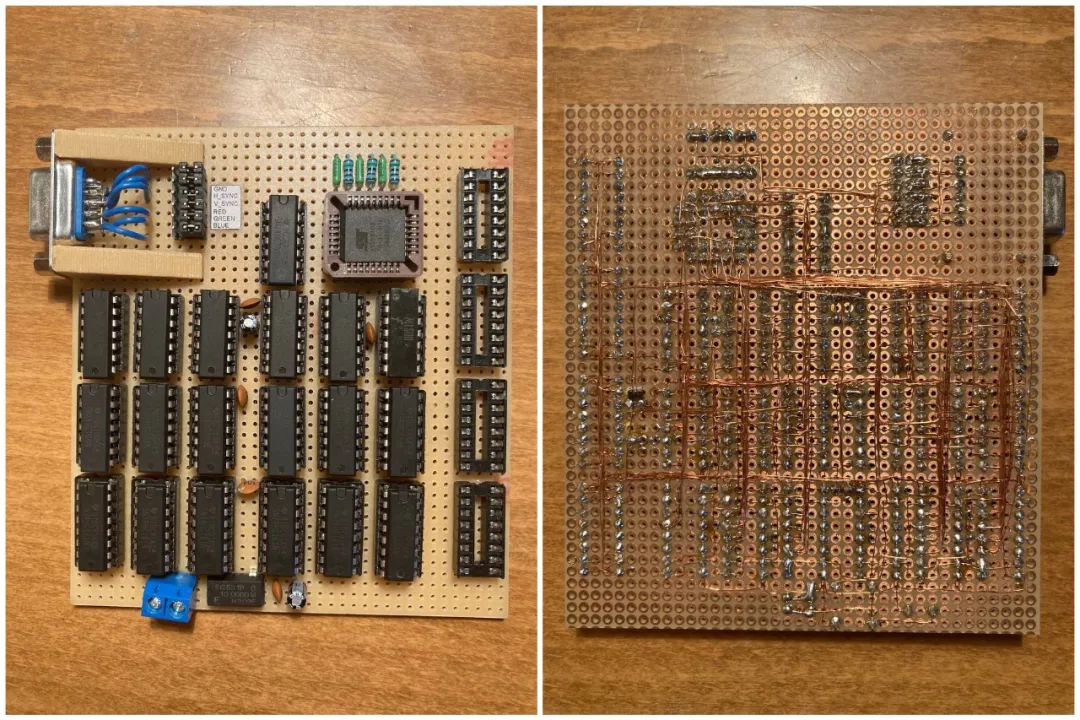

接下来,我将开源电子原型平台 Arduino 连接到每个 PCB 的输入端、同时监控输出端并与预测端(prediction)做对比,从而对这些 PCB 进行测试。设置好之后,一切就可以自动运行了。每次测试都至少持续数个小时。

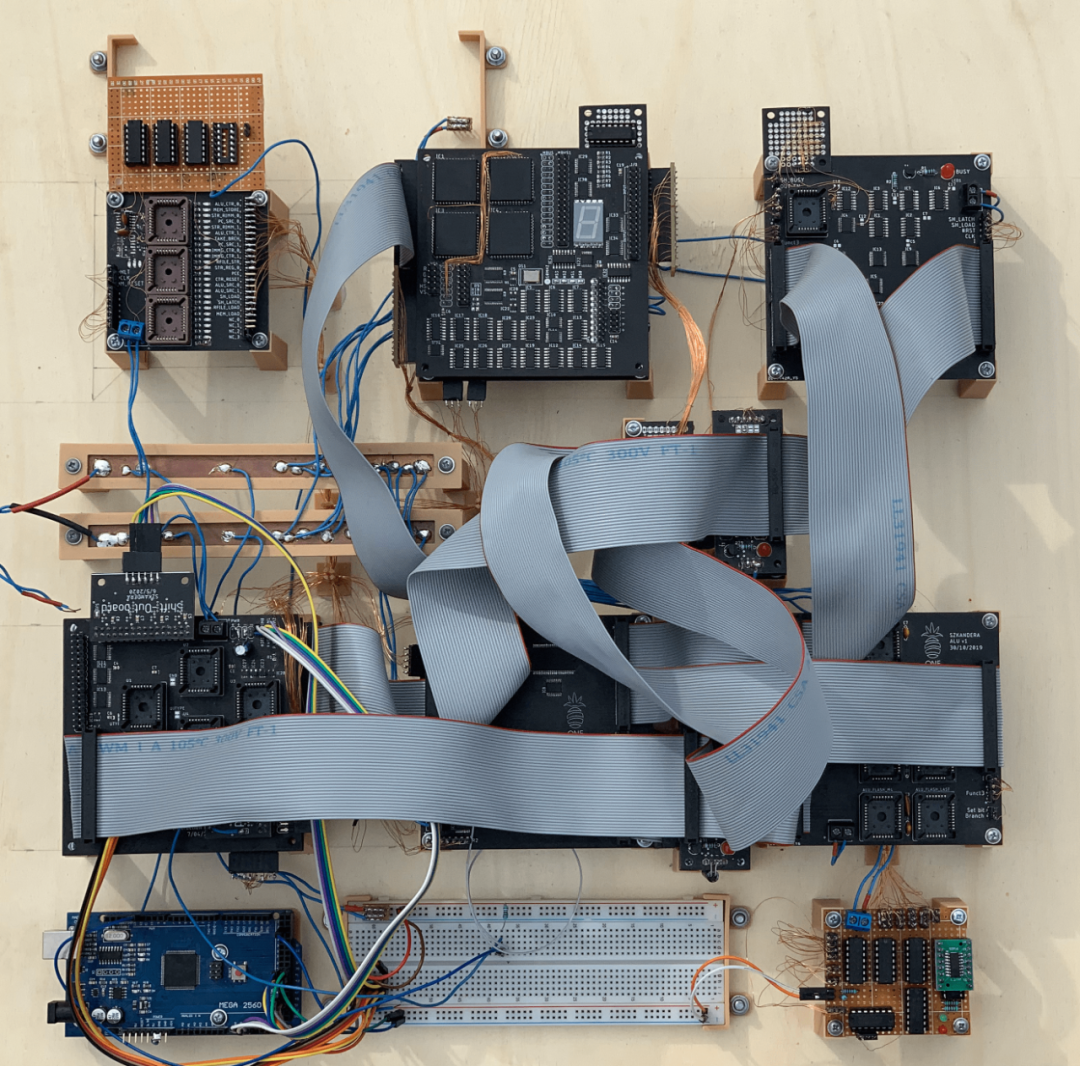

当我准备好将所有 PCB 整合到一块时,模块也已经间隔地安装在了木头上,并使用 3D 打印垫片(spacer)来固定。接着上传了一个测试程序并开始测试,原型机示意图如下:

Arduino 平台仅用来调试,没有在最终成品中使用。

尽管我单独测试了每个 PCB,但首次尝试还是失败了,这不足为奇。我又不得不花费大量时间来找失败的原因,找出了一些错误,如很难发现的时序问题。

输入 / 输出端口

我构建的 RISC-V CPU 拥有两个 8 位输入端口和两个 8 位输出端口,你可以通过 RJ50 连接器在前板上访问。此外,顶部模块上有一个 7 段式显示器(7-segment display),它与一个可以通过程序访问的寄存器相连。

至于与 VGA 显示器的连接,我受 Ben Eater 的启发构建了一个 VGA 卡。VGA 的输出分辨率是 200×150 像素,黑白显示。虽然我想实现彩色显示,但需要使用大型 V-RAM,太贵了,也就放弃了。

下板(board)将显示存储在 EEPROM(带电可擦可编程只读存储器,型号 39SF010A)中的静态图像。我在最终成品中使用到了双端口 SRAM(静态随机存取存储器)。

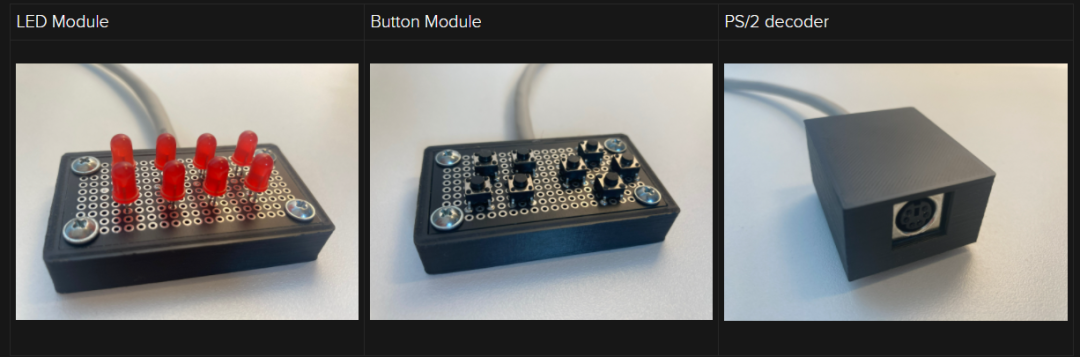

构建了一些演示用的 I/O 模块,它们在末端都有 RJ50 连接器。

PS/2 解码器是买的现成的,我没有时间自己制作。

最终成品

让原型机运行不太容易,在大约 5 个月的时间后,我终于成功了。

我又重新设计了所有的 PCB电路板,修复错误,并将这些 PCB 以塔状结构堆叠,所以每个模块仅用针座(pinheader)相连接。重新设计 PCB 大约花了 3 个月的时间,然后对最终的 PCB 进行有序排列。

此外,我还设计并使用 Prusa i3 3D 打印机打印了一个圆柱体外壳,足以容纳所有的 PCB 和 I/O 连接器,这样也可以将键盘和 VGA 显示器直接连接到计算机。

最终成品的组件拆卸如下图所示。

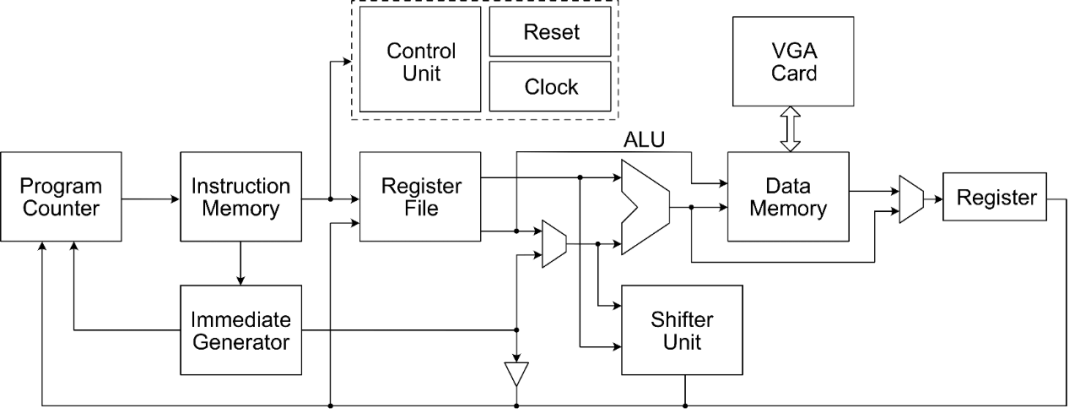

架构图如下所示。

编程

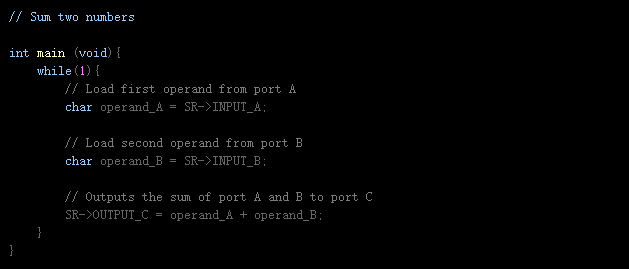

最后,在经过了数百小时的设计、焊接和调试,我终于看到了成功的曙光。在好友 Jan Vykydal 的帮助下,我设置了一个兼容 RISC-V 且运行良好的编译器,使用 C 语言编写了一些系统软件和 demo 程序。这个编译器可以生成机器代码,我使用一个 Python 脚本来接收代码,并写入 CPU 内存。

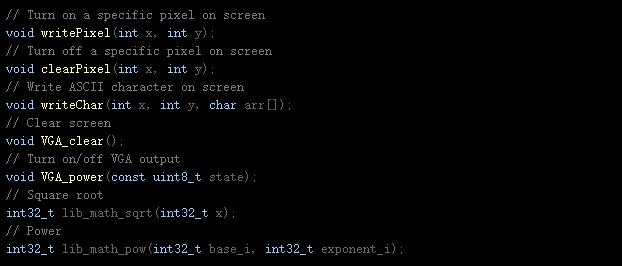

我还创建了一个具有一些有用函数的库,代码如下:

利用这个库,我创建了一个简单的 shell 程序,这样可以通过「与其中一个输入端口相连的 PS/2 键盘」来实现与该程序的交互。我使用带有模块的 PS/2 键盘将输入信号解码为 8 位。

-

怎么制作一款基于RT-Thread和PSoC的光照监测仪呢?2023-08-02 881

-

制作了一个GlobLED2022-11-14 431

-

自制一款PCB吉他2022-07-15 2174

-

手工制作了一款32位CPU2022-03-22 2789

-

自己制作一款CMSIS-DAP调试器2022-02-28 1412

-

如何制作一款HID键盘?2022-01-18 1091

-

如何自己制作一款AD转换模块2021-07-27 1125

-

调光小台灯制作过程2018-10-03 24420

-

一款简单的存储器读写仪制作2018-01-29 1325

-

我制作了一个智能小车,不知道用哪款软件?2015-11-06 4065

-

电子制作手工焊接技术基础2012-01-31 31600

-

用废旧电路板制作一款超低价音响2012-01-12 8078

-

神州龙芯——中国第一款CPU2011-12-23 6726

-

一款32位嵌入式CPU的定点加法器设计2010-07-19 730

全部0条评论

快来发表一下你的评论吧 !