亮相DAC!芯华章发布新一代高速仿真器GalaxSim Turbo 助力千亿门超大规模芯片敏捷验证

制造/封装

描述

7月12日,在一年一度的全球电子设计自动化盛会DAC 2023 上,面向来自世界各地的顶级EDA公司和芯片、系统厂商,国内领先的系统级验证EDA解决方案提供商芯华章,隆重推出新一代高速仿真器GalaxSim Turbo,并以指数级的数字仿真加速优势、千亿门级的超大验证容量,在DAC上收获专业用户的广泛青睐。

GalaxSim Turbo

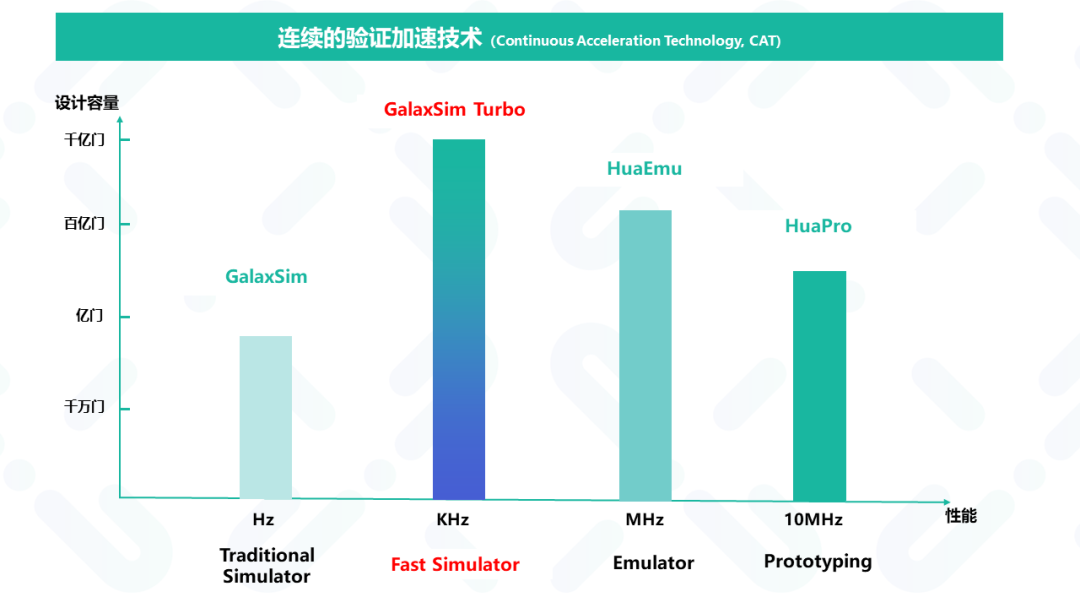

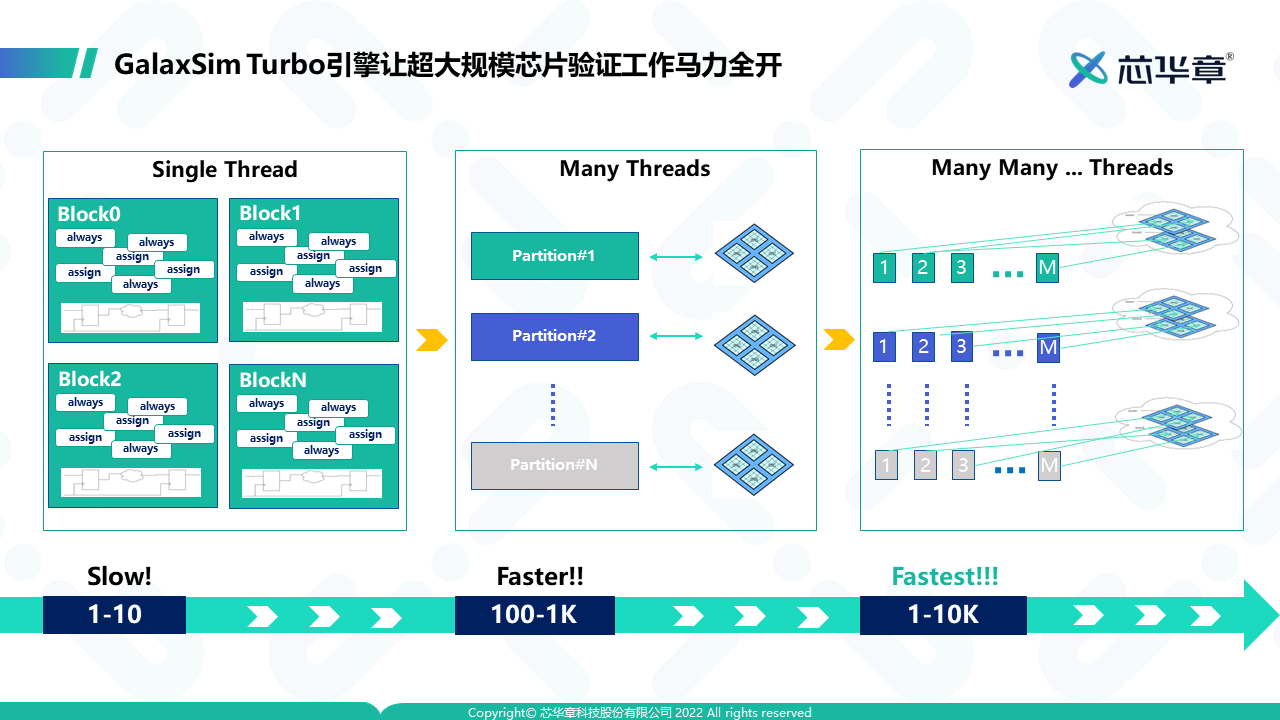

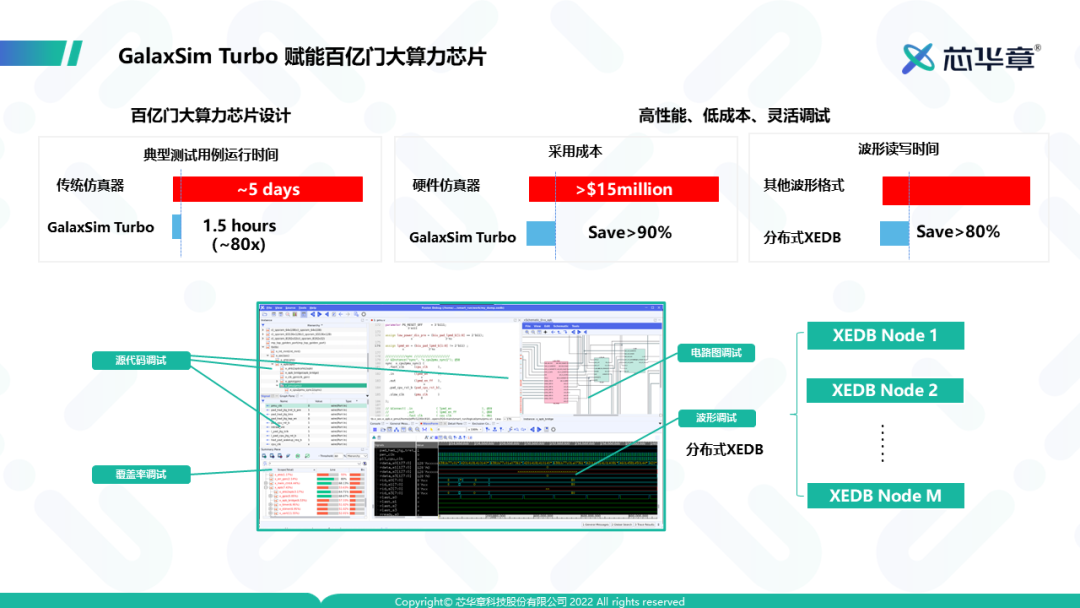

基于超大规模分布式仿真技术,GalaxSim Turbo通过打造多种仿真引擎,实现多核、多服务器并行算力,在大幅提高运行速度的同时,可以有力支持千亿门级的超大规模芯片敏捷验证与开发。这一技术的应用,对于打破传统逻辑仿真器的验证容量限制,在芯片设计早期引入系统级验证,实现芯片设计和验证的持续集成及设计(CICD)具有至关重要的作用,填补了传统逻辑仿真器和硬件仿真器(Emulator)之间的空白。

日益细分的应用场景需求、紧迫的研发创新周期、规模大而复杂的系统级芯片,都在呼唤着EDA行业带来更多的颠覆和革新。作为芯片验证必不可少的一个环节,仿真主要是通过计算机结合测试激励来模拟芯片在真实环境下的运行状况,帮助工程师来判断运行结果是否符合预期, 并提供仿真数据以便进一步调试。传统的逻辑仿真器产品,在很多场景下受限于事件的异步行为,设计的分割(Partition)和线程同步有较大的限制,往往无法支持高速的并行仿真,从而大大限制了验证的场景和规模。RTL验证也成为了整个验证流程中耗时最多,人力成本投入最大的环节。

2021年,芯华章率先发布支持国产服务器架构的数字仿真器穹鼎GalaxSim,全面支持IEEE1800 SystemVerilog语法、IEEE1364 Verilog 语法以及IEEE1800.2 UVM方法学。针对敏捷验证需求,芯华章本次推出数字仿真器系列创新之作——GalaxSim Turbo高速仿真器(Fast Simulator),解决传统逻辑仿真器无法满足的超大规模系统级验证需求。

产品亮点:

◉ 自带事件级(Event-based)和周期级(Cycle-based)仿真引擎

◉ 支持SystemVerilog等多种设计与验证语言,对IEEE最新UVM标准提供原生态支持

◉ 支持超大规模集成电路设计,最高可支持千亿门

◉ 智能编译分割技术、自动化分布式仿真技术,充分发挥多服务器多核并行算力

◉ 提供开放架构,支持与其他仿真器、原型系统和硬件加速器进行联合仿真

◉ 提供灵活的交互式仿真模式以及完整的调试方案

通过自有专利支撑的逻辑分割和分布式仿真解决方案,GalaxSim Turbo融合CAT技术(Continuous Accelerating Technology),具备传统仿真器没有的并行计算能力,带来更快的仿真速度,将逻辑仿真器的应用场景拓展到了系统级层面,可以帮助大规模设计在RTL阶段就提早进行系统级验证,实现高效率、高效益的迭代,从而帮助客户大大提高验证效率。 在大算力芯片设计的实测中,完全同等条件下,传统仿真器进行典型测试需7天的时间,GalaxSim Turbo使用了400多个计算线程,将仿真时间缩短到2小时以内,取得相较于传统仿真器近百倍的突破性效率提升。

智能汽车计算芯片引领者

黑芝麻智能创始人兼CEO单记章表示:

“为了满足智能网联汽车的差异化需求,新一代车规芯片的开发需要满足大算力、高集成以及更快的迭代要求,服务整车主机厂商实现更高的性价比以及更快的产品上市需求。芯华章GalaxSim Turbo独有的智能分割以及分布式仿真技术,帮助我们优化了验证资源的投入,通过提前引入软硬件协同的系统级验证,极大地缩短了开发周期,降低了研发成本和各项安全风险,从而更快将产品推向市场。”

芯华章科技董事长兼CEO王礼宾表示:

“我们很高兴能够助力黑芝麻完成智能汽车计算芯片设计和大规模量产的突破。随着集成电路设计规模日趋庞大,SoC级芯片验证复杂性不断提升,对于敏捷验证和创新效率的要求也日益增高。基于自主知识产权的高性能数字仿真技术,芯华章致力于帮助芯片设计及系统公司不断提高研发创新效率。未来,我们希望继续与黑芝麻紧密合作,助力汽车智能化发展,赋能社会经济数字化转型高质量发展。”

- 相关推荐

- 热点推荐

- 芯华章

-

芯华章仿真器GalaxSim荣登“国产EDA工具口碑榜”2025-12-10 4305

-

芯华章 HuaEmu E1 四大技术打通超大规模验证核心瓶颈2025-12-04 2994

-

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升2025-11-17 2209

-

芯华章RISC-V敏捷验证方案再升级2025-07-21 1255

-

国产EDA公司芯华章科技推出新一代高性能FPGA原型验证系统2024-12-10 2221

-

芯华章发布国内首台超百亿门大容量硬件仿真系统 完备数字验证全流程工具平台2023-06-16 978

-

芯华章正式发布国内首台设计上支持超百亿门大容量的硬件仿真系统2023-06-15 1391

-

芯华章敏捷验证赋能Chiplet系统级大规模芯片设计2023-05-25 1578

-

芯华章强强联手加速打造系统级数字验证解决方案2022-09-26 1240

-

瞬曜EDA发布RTL高速仿真器ShunSim,大幅提升超大规模集成电路验证效率2022-06-24 2410

-

创新引领|芯华章联手芯来科技提升RISC-V处理器设计验证2022-03-03 2327

-

更快更强!芯华章HuaPro-P1助力加特兰新一代芯片产品设计验证2022-02-10 2146

-

超大规模集成电路的生产工艺流程2019-07-29 3318

-

Veloce平台在大规模SOC仿真验证中的应用2010-05-28 2346

全部0条评论

快来发表一下你的评论吧 !