如何遍历force多位宽信号的每一比特?

电子说

描述

大家在构建测试激励时,经常会遇到需要使某个信号强制变成某个值,此时我们经常会用到Verilog和SystemVerilog中的force实现这样的功能。但是有时候在对多位宽的信号进行force时有时会出现编译错误,这是为什么呢?本文将对此类情况进行示例说明。

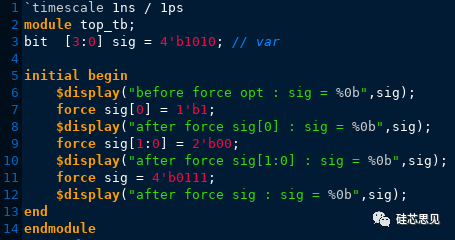

【示例】

【仿真结果】

示例中,通过三种方式对sig中的部分位选进行了force。通过force将sig中的第0位force为了1,从显示信息可以看到sig[0]已经被修改;通过force将sig中的第0位和第1位force为了00,从显示信息可以看到sig[1:0]已经被修改;通过force将sig整体force为了0111,从显示信息可以看到sig[1:0]已经被修改;

可以看到,我们可以通过force对于变量、变量中的某一位或者某一个片段进行改变,那么可能有些人觉得这么一位一位的进行force太麻烦了,是否可以使用for循环对sig中所有位遍历进行force呢?请看下例。

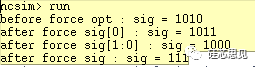

【示例】

【仿真结果】

编译错误!这是为什么呢?对比该示例和上一示例,可以发现当信号的索引为常值时,可以进行force,但是当索引为变量时,此时编译不通过。

也就是说在对信号进行force的时候,如果要对其中的某一位或者一个片段进行force时,其中的索引只能是常数不能是变量,否则将会导致便以失败。

那么如果想实现通过变量实现对于多位宽信号中每一位进行force还有什么办法吗?下面我们通过示例介绍几种。

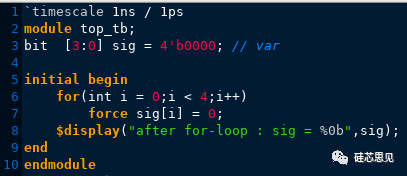

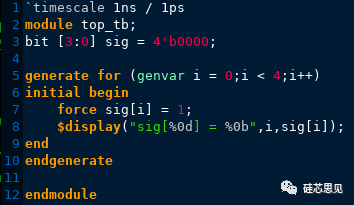

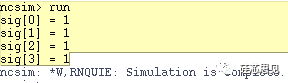

【示例】使用generate结构

【仿真结果】

示例中,使用generate结构实现了对于sig中每一位的遍历。这其实借助了generate是在仿真前的析构(elaboration)阶段完成的特性,即在仿真开始之前,相当于已经将sig被force的每一位的initial结构都已经生成好了,这样在仿真开始执行时(生成好的initial块开始被执行时),其中“force sig[i]”中的i都已经是确定的值了,因此就可以避免force信号中某一位时,索引为变量的情况。

除了这种在析构(elaboration)阶段就生成好语句结构的方式外,还可以想如下方式操作。

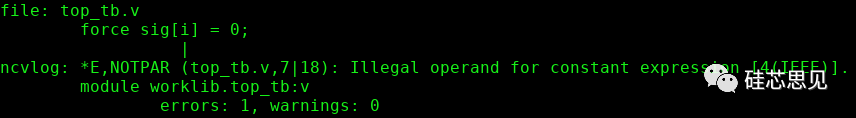

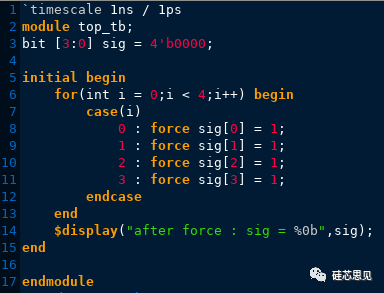

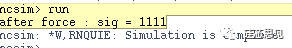

【示例】

【仿真结果】

示例中,实际上是将要force的信号每一位都单独写了出来,即保证了被force信号的索引都是常量,缺点是,如果这个信号比较宽,那么写起来比较枯燥,没有上一种使用generate结构方便。但是实际上两者之所有都没有问题,其实都是保证了被force信号的索引是个常值。

所以,如果在实际使用时,需要对多位宽信号的每一位或者某一个片段进行force,那么需要保证被force的那一位或者那一个片段的索引值在仿真运行开始时是常值。

审核编辑:刘清

-

多位宽数据通过握手方式跨时钟域2023-05-06 2372

-

同步从一个时钟域到另一个时钟域的多位信号怎么实现?2020-08-17 1959

-

I-Force410无铁芯直线电机2021-09-01 1521

-

LS1046 SDRAM多位错误注入怎么处理?2023-03-28 545

-

Design of Crimp force Monitor2009-08-25 708

-

Merkle树遍历技术的研究2010-03-01 777

-

存储百倍提升! IBM纳米技术1比特12原子2012-01-16 5535

-

二叉树的前序遍历、中序遍历、后续遍历的非递归实现2017-11-27 1384

-

jquery的each遍历方法2017-12-03 2964

-

螺旋遍历二维数组漫画讲解2020-11-26 2410

-

总结一下OpenCV遍历图像的几种方法2023-01-18 2441

-

HashMap遍历操作为什么不能一边遍历一遍删除呢?2023-02-10 1164

-

跨时钟域电路设计:多位宽数据通过FIFO跨时钟域2023-05-11 5313

-

对于多位的异步信号如何进行同步呢?2023-09-12 2381

-

python如何遍历列表并提取2023-11-23 2542

全部0条评论

快来发表一下你的评论吧 !