HDIO OBUFT和IOBUF用例简析

描述

问题描述:

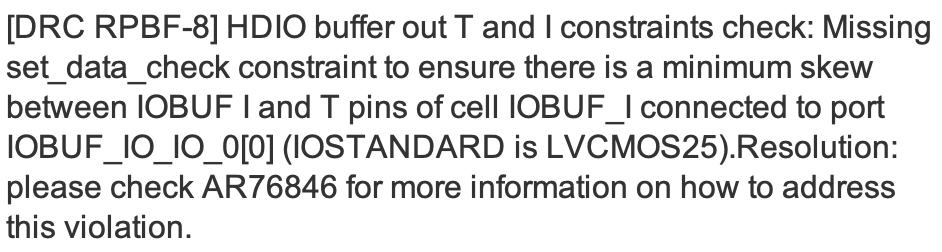

本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF) 的 HDIO 输出缓冲器的上电电压为 3.3 V 或 2.5 V 并且 Data(数据)控制信号与 Tristate(三态)控制信号的切换时间彼此相近,则可能会受到三态数据争用条件的影响。

仅当三态和数据开关彼此相反(例如,三态 0 -> 1 且数据 1 -> 0)时,此争用条件才会导致问题。当三态和数据开关同向(例如,三态 0 -> 1 且数据 0 -> 1)时,则不会导致问题。

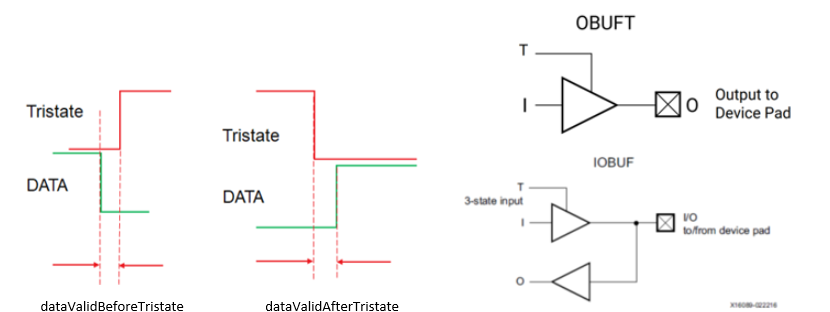

生成的输出可能会驱动错误的焊盘电压。焊盘可能保持在此错误电压下,直至三态(dataValidBeforeTristate 场景)或数据(dataValidAfterTrisate 场景)再次切换为止。

^dataValidBeforeTristate = 550 ps

dataValidAfterTristate = 200 ps^

受影响的器件: 除 VSVD1760 外的其他封装中的 VC1902、VC1802、VM1802、VM1402 和 VM1302。

仅限含 HD bank 的器件才会受到 HDIO IOBUF 和 OBUFT 用例的影响。VSVD1760 封装不含 HDIO bank,因此不受影响。

受影响的 IP 核:

虽然 IP 通常并不强制使用 HDIO,但以下 IP 核使用 HDIO 缓冲器的方式很可能使其受此问题影响。此处随附的 Tcl 脚本可用于帮助调整诸多场景下的数据到三态布线关系:

AXI 1G 以太网

AXI QSGMII

三模以太网 MAC

AXI QSPI

解决方法:

要解决该问题,请确保在有问题的窗口(dataValidBeforeTristate = 0.550ps 和 dataValidAfterTristate = 0.200ps)中,数据和三态不执行切换。

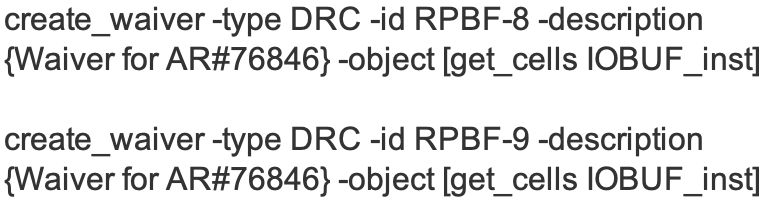

在 Vivado 2021.2 和更高版本中,DRC 将向用户标记此问题:

下列方法可用于确保在有问题的窗口中,数据和三态不执行切换:

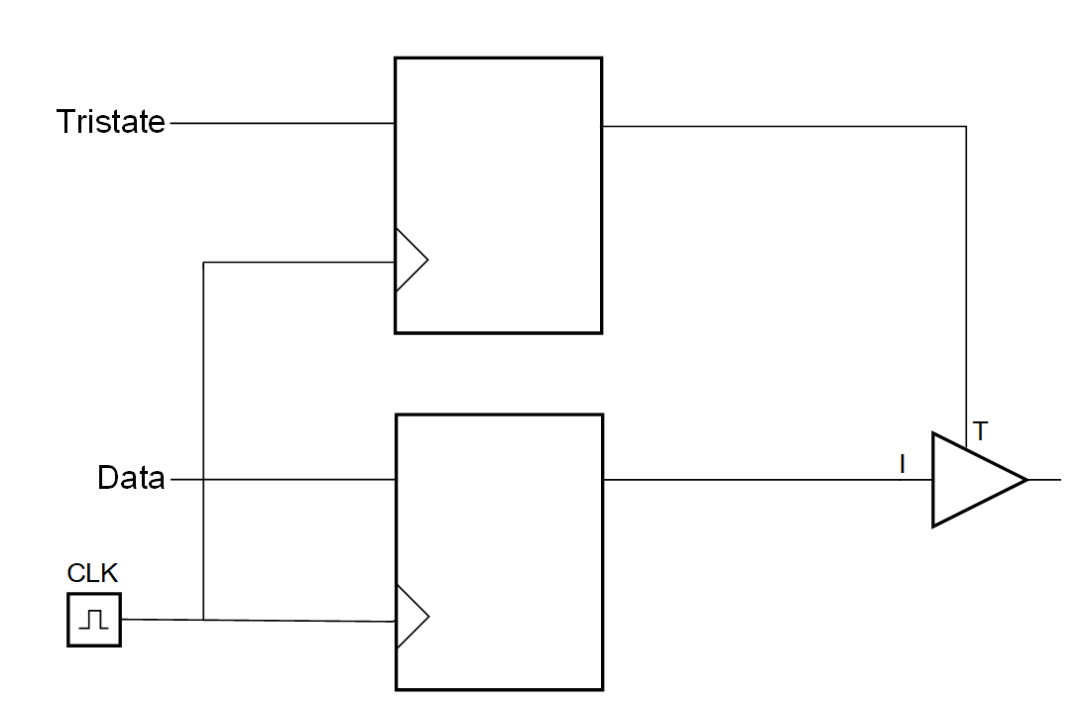

通过设计系统将三态和数据切换偏移一个周期。

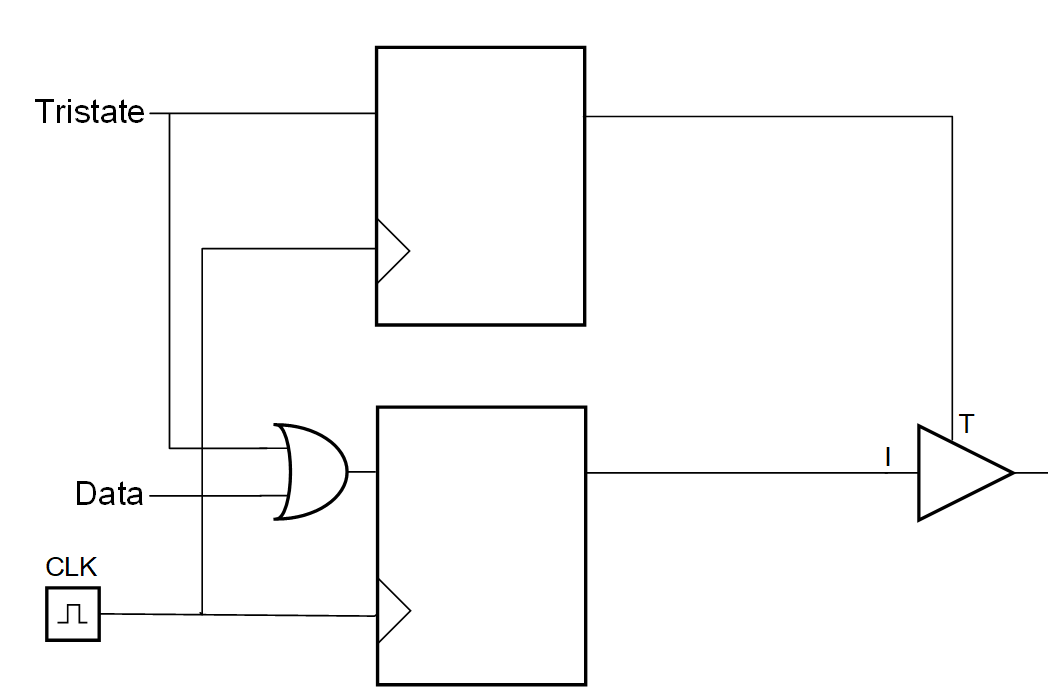

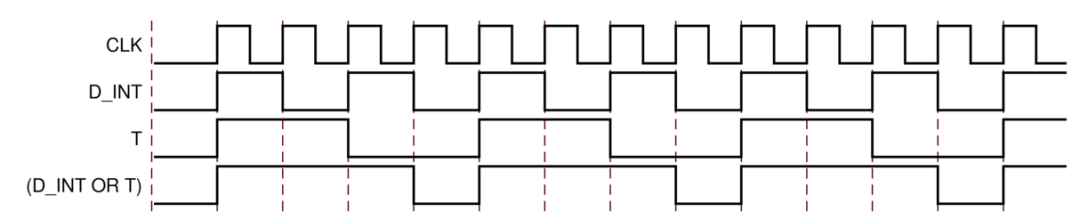

寄存的数据和三态信号可以在 IOL Flop 的 I 输入中利用数据和三态的逻辑 OR 来避免此问题。

将

替换为

时序图示例:

通过 Tcl 脚本使用 set_data_check 约束来确保数据和三态信号线的偏差足以确保数据和三态都能避免出现争用条件。

注释: 仅当数据和三态都发生切换时,才会发生此问题。在 Data 管脚上,Open Drain(开漏)接口保持常量“0”,因此常用 2.5 V 接口和 3.3 V 接口(如 I2C)将不受影响。

仅当数据或三态已绑定时,才能通过以下命令豁免 DRC。

对于 Vivado 2022.1 和更低版本,您可使用随附的 fixHDIO.tcl 脚本来评估影响,并且可能通过布线来修复此问题。

此脚本将检查 IOBUF 或 OBUFT 的设计,并检查三态与数据之间的延迟,确认在有问题的窗口内是否发生切换。

如果发生了切换,此脚本将通过 set_data_check 置位来取消这些信号线的布线,重新布线,并报告结果。

要运行该脚本,请打开已实现的设计或 DCP。

在 Tcl 控制台中,使用 source 命令找到该脚本:

source -quiet fixHDIO.tcl

找到 Tcl 脚本后,可运行多个过程来分析设计:

getHDIOTristateBuffers - 列出以 2.5 V 或 3.3 V 上电的 HDIO bank 中含三态控制的所有缓冲器,这些缓冲器可能会受到三态/数据争用问题的影响。

reportHDIOTristateBuffers - 报告以 2.5 V 或 3.3 V 上电的 HDIO bank 中含三态控制的所有缓冲器(可能受三态/数据争用问题影响),并描述用于报告这些缓冲器的原因的机制。

validateHDIOTristateBuffers - 该命令将分析设计,查看是否有足够的时序裕度能在尚未运行 fixHDIOTristateBuffers 时就避免出现争用条件。如果发生违例,则必须运行 fixHDIOTristateBuffers 来解决问题。

waiveHDIOTristateBuffers - 该命令应仅用于为下列已寄存的缓冲器豁免 DRC 违例:此类缓冲器在三态/数据管脚之间实现 OR 门控,或者已知不受影响(即,在设计中,数据和三态控制已偏移)。运行 fixHDIOTristateBuffers 后,应自动禁止显示这些缓冲器的 DRC 违例。 仅限在已知不存在问题的缓冲器上运行该过程。 fixHDIOTristate 缓冲器将通过更改时序来解决此问题,应将其用于有问题场景的所有缓冲器。

fixHDIOTristateBuffers - 为没有足够数据和三态偏差的缓冲器的数据和三态信号线执行重新布线。此命令不修复在三态/数据管脚之间需要 OR 门控的已寄存的缓冲器。此过程结束时会报告时序关系。此过程结束时,应在 Tcl 中运行“report_route_status”以验证脚本确实能够成功完成信号线的重新布线。 如不执行此操作,可能导致该脚本误报所有时序路径都已满足。

timeHDIOTristateBuffers - 报告数据与三态管脚之间的时序关系。应在 fixHDIOTristateBuffers 插入必要的时序约束后运行此命令。如果该工具能够找到布线解决方案,那么应仅存在正时序裕量。

分析结果:

fixHDIOTristateBuffers 和 timeHDIOTrisateBuffers 将报告所提供的缓冲器上的时序。裕量值为正表示脚本已成功完成 Data (I) 和 Tristate 控制 (T) 的重新布线。

在此场景下为了正确定时,将对数据或三态给予 1000 ns 的要求。预计将有一条信号线存在较大的偏差要求。 只要信号线均为正,就不会发生 HDIO 三态冲突。

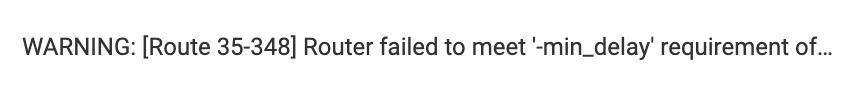

出现如下消息表示,如果 Tcl 脚本无法通过新的布线解决该问题,那么布线器就无法以充足的偏差完成设计的重新布线。

注释: 在此场景中,如果报告的裕量为正值,那么即使出现该警告也没问题。

该脚本将标记 IOB 触发器对数据和三态进行寄存的情况,但不会尝试解决。

这些管脚需实现与上述逻辑等效的电路更改,并对驱动 IOB 数据寄存器的输入管脚的数据和三态信号线执行 OR 逻辑。

如果 Tcl 脚本以避免出现该问题的方式成功完成数据和三态管脚的重新布线,则将需要修改设计。围绕此问题常见的修改包括:

寄存数据和三态控制信号,对数据控制和三态控制执行 OR 逻辑,如上所述。

调整设计,使三态和数据断言偏移一个周期。

如果出现该脚本无法解决此问题的罕见情况,请评估选项 1“将三态和数据切换偏移一个周期”和选项 2“对数据和三态执行逻辑 OR”,并对设计执行必要的更改。

审核编辑:刘清

全部0条评论

快来发表一下你的评论吧 !