ASIC设计约束与SDC命令介绍

可编程逻辑

描述

在数字IC设计中,重要的ASIC设计约束分为两类,主要是:

1.优化约束

2.设计规则约束(DRC)

根据ASIC逻辑设计,优化的约束是速度和面积。在物理设计中,我们需要对面积、速度和功率进行优化设计。根据所需的技术节点和策略进行更好的功耗规划,总是有助于获得芯片的布局。

DRC是晶圆铸造规则,主要是传输、扇出和容量。

约束可用于在逻辑和物理综合的各个综合阶段优化设计。

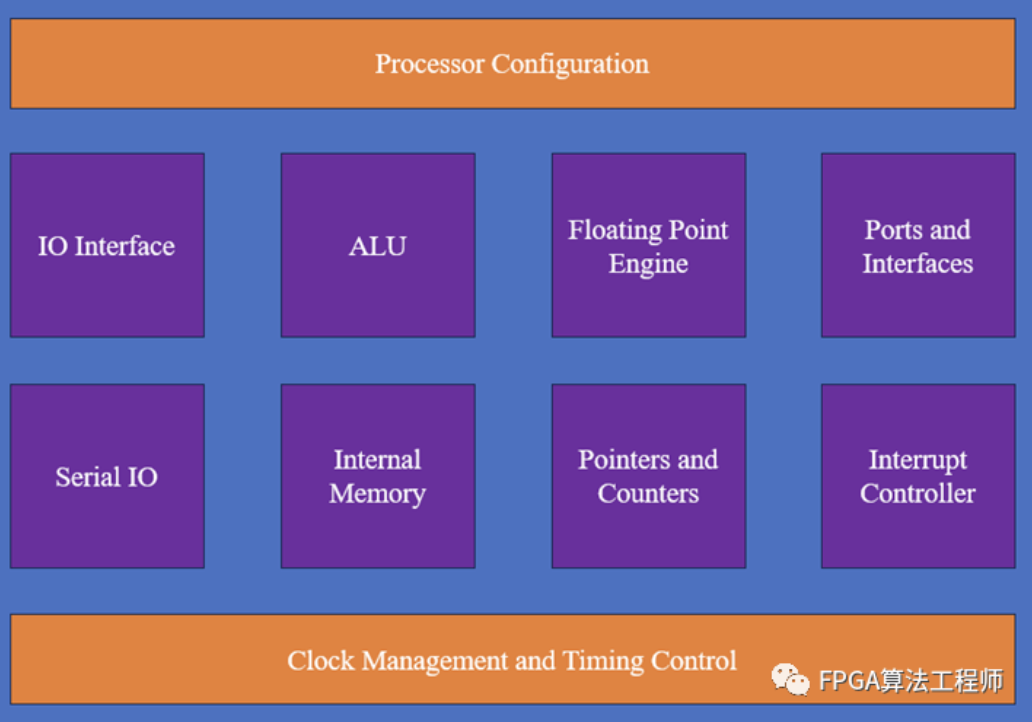

这些约束在设计的模块、顶层和芯片级别。例如考虑如图所示的处理器架构,可以为各种功能块指定块级约束,这些功能块包括ALU、浮点引擎、高速接口等。顶层约束将在综合过程中使用,它们用于集成所有功能块。

处理器顶层架构

如果满足模块级约束,并不意味着设计将满足顶层约束。在物理设计期间,需要满足干净布局的芯片级约束。

对于处理器的综合,以下可能是较好的策略:

- 为不同的时钟组执行综合。

- 使用自底向上的综合并提取模块级约束。

- 在模块级综合过程中优化设计,以满足面积和速度的要求。

- 指定顶层约束。

- 执行顶层综合并优化设计以满足顶层约束。

- 如果不满足约束条件,则使用策略来调整RTL架构。

1. 重要设计概念

1.1 时钟树

时钟树综合是在物理设计流程中进行的,而在逻辑设计流程中我们没有时钟分布的信息。也就是说,我们将尝试使用具有可用统计数据的Synopsys DC设置来指定时钟和时钟延迟。

1.2复位树

具有多个功能块初始化复位的设计需要与主复位同步。如果复位是在时钟的有效边缘期间产生的,则复位树可用于避免亚稳态输出。

要考虑的重要参数是:

1.复位恢复时间

2.复位移除时间

1.3 时钟和复位策略

在逻辑设计过程中,以下策略可能会对复位和时钟有所帮助。

1.对于多个时钟域,在数据和控制路径中使用同步器。

2.使用统计数据来引入时钟延迟,并指定逻辑综合过程中的设置和保持不确定性。

3.在逻辑设计期间手动实例化时钟。

4.使用复位同步器将复位与主复位同步。

1.4 影响设计性能的是什么?

ASIC设计应满足速度和面积的优化约束。我们将在物理设计期间使用功率限制和DRC。以下是在综合过程中需要解决的要点:

- 模块级约束 :对于复杂的ASIC设计,如果我们考虑多个功能块或IP,那么应该指定块级约束。功能块的块级约束应该满足。例如,处理器逻辑工作在250MHz的工作频率,但整个芯片工作在500MHz。在这种情况下,与顶层约束相比,设置和保持的总体不确定性是不同的。因此,应该在块级综合期间使用块级Tcl脚本。

- 顶层约束 :在完成所有功能块的综合后,对于自底向上的综合,进行顶层集成。需要为特定的时钟组指定顶层约束,主要在Tcl脚本中,应该使用以下命令:

(a)时延信息

(b)输入时延

(c)输出时延

(d)setup不确定性

(e)hold不确定性

如果满足模块级约束,但不能保证满足顶层约束。可能原因是这样的:

1. 如果设计分区不在顺序边界上,则会产生额外的延迟。

2. 数据到达速度快,且设计中存在缺陷。

3. 数据到达缓慢,并且设计存在设置冲突。

4. 如果在综合过程中,由于多循环和假路径,会出现定时异常。

5. 由于同步策略不佳导致数据完整性降低。

6. 如果设计有层次结构,并且DC不能优化粘合逻辑。在这种情况下,设计需要扁平化以提高优化。

2. 约束说明

需要为Verilog文件指定的模块和顶层综合的重要约束是面积、速度和功率。让我们排除功率,因为功率优化不是使用DC进行的。作为一名设计师和综合团队成员,我们的目标是对设计有功能性的理解,以及对设计的整体面积和速度要求。

2.1 面积约束

在逻辑综合期间,该区域是由于使用的逻辑和宏。标准单元信息在库中可用,并且需要特定的宏来实现设计的低级抽象。整体面积优化可以在过程中进行:

- RTL设计 :使用资源共享、资源分配、消除死区、使用括号和摸索等概念。

- 综合 :通过使用工具指定的命令和使用区域优化命令,可以优化区域。

2.2 速度约束

速度是特别重要的因素,因为它决定了设计的整体性能。设计的速度约束需要根据特定技术节点的库中可用的统计数据来制定,并且要满足这些约束。由于实际的布局布线在逻辑综合期间不可用,因此目标是仔细查看以消除块和顶层设计的设置冲突。综合和STA团队需要指定以下内容:

1. 时钟

2. 时钟延迟

3. 建立并保持不确定性

4. 输入和输出最大和最小延迟

5. 选择多周期路径

6. 指定伪路径

2.3 功率约束

功率是另一个约束条件,在功率规划中,我们将约束条件指定为漏电和动态功率。为了实现低功耗感知架构和设计,我们将在各个设计阶段使用统一功率格式(UPF)。以下是一些优化功率的策略:

- 架构设计 :具有低功耗架构设计,具有上电顺序和电源关闭策略。

- 使用低功率单元 :在设计过程中使用低功率单元,但设计师需要更好地了解单元的特性,因为这些单元的使用对设计速度有重大影响。

- RTL设计 :在RTL设计中,使用时钟门控单元来降低动态功率。

3. 设计中的问题

以下是ASIC综合过程中的重要挑战:

1. 逻辑的修改。

2. 未连接的端口和网络满足了模块级速度限制,但在顶层设计上失败了。

3. 虽然RTL验证成功,但设计的模块级连接存在缺失。

4. 综合期间的重要SDC命令

本节讨论在综合过程中使用的重要DC命令,这些命令对于指定约束很有用。

4.1 Synopsys DC命令

在ASIC综合过程中使用的一些SDC命令记录在本节中。

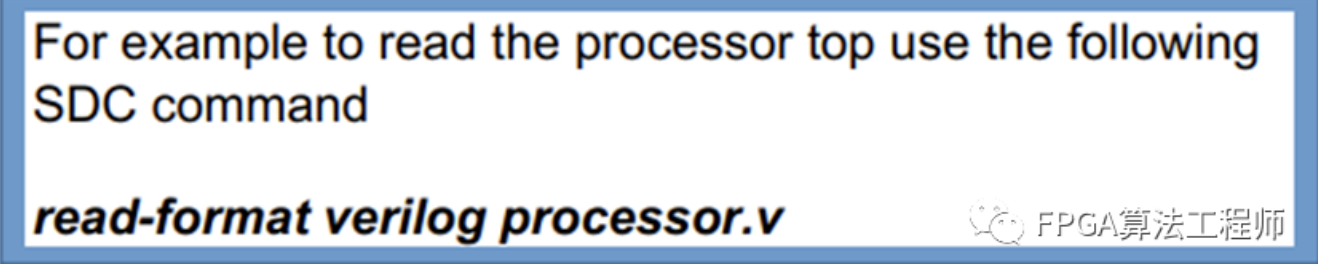

1.Reading the design(读取设计)

**read –format **

以上命令用于读取设计。

2. Analyze the design(分析设计)

**analyze –format < format_type > **

用于分析设计。它用于报告语法错误,并在拥有通用逻辑之前执行设计转换。通用逻辑是synopsys通用技术独立库的一部分。这些组件被命名为GTECH。这个逻辑是布尔函数的未映射表示。

3. Elaborate the design(细化设计)

**elaborate –format < format_type > **

用于细化设计,并可用于在细化过程中为相同的分析设计指定不同的架构。

重要的是要了解Read、Analyze和Elaborate命令的区别。以下是关键点:

1. 在进行细化设计的同时,通过分析和细化来传递所需的参数。

2. 在输入DC中预编译的设计或网络列表时使用读取。

3. 使用analyze和elaboration命令,可以在精化过程中为相同的分析设计指定不同的架构。

4. read命令不允许使用不同的架构。

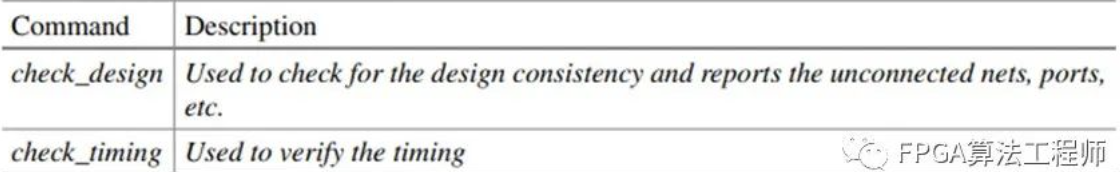

4.2 设计检查

在使用DC读取设计之后,使用check_design来检查设计问题,如短路、断路、多个连接、实例化和无连接。

4.3 clock定义

需要使用命令create_clock指定时钟,并且在时序分析期间将其用作参考时钟。使用create_clock命令定义时钟的示例如下。

**create_clock–name -period **

该命令用于为设计创建时钟,作为时序分析时的参考时钟。如果设计没有时钟,那么它将被视为虚拟时钟。

时钟有不同的占空比

如果设计者希望使用具有0.5 ns上升沿和2 ns时钟周期的可变占空比时钟,则create_clock命令可以修改为

create_clock –name clock - period 2 –waveform {0.5,2} –name processor_clock

虚拟时钟

如果设计没有时钟引脚,则使用以下命令创建虚拟时钟。

下列命令生成频率为500mhz,占空比为50%的虚拟时钟。

create_clock –name clock -period 2

下列命令生成频率为500mhz的虚拟时钟,具有可变占空比,上升沿为0.5 ns,下降沿为2 ns。

create_clock –name clock -period 5 –waveform {0.5,2}

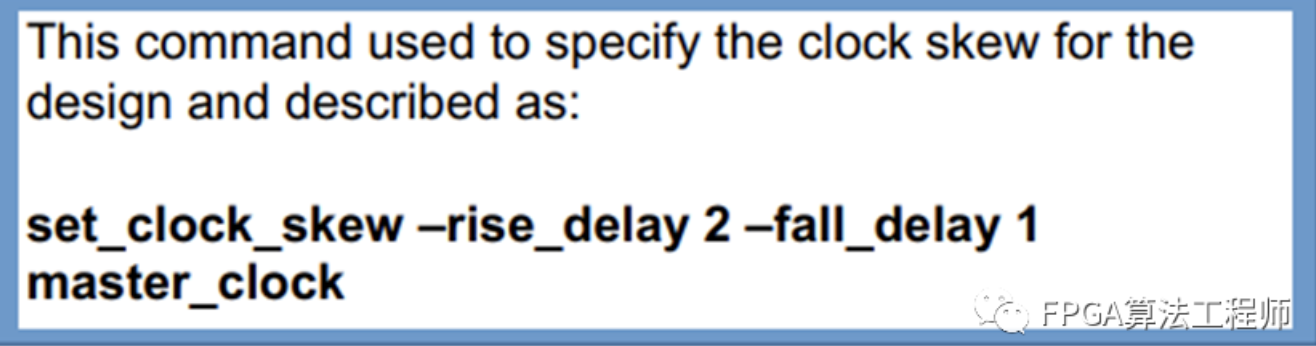

4.4 skew定义

正如前面的文章所讨论的,偏差是时钟信号到达之间的差异。如果源触发器的时钟相对于目标触发器延迟,则该偏差称为负时钟偏差,对hold有用。如果与源触发器相比,目标触发器的时钟延迟,则该偏差称为正时钟偏差,对setup很有用。原因是目标触发器的时钟延迟,数据可能由于偏差而延迟到达。

设计编译器将无法综合时钟树,所以为了克服这个问题,时钟倾斜是用来指定延迟的!

下列命令由设计编译器用于指定设计的时钟倾斜

**set_clock_skew –rise_delay -fall_delay **

4.5 Input /output delay 定义

可以分别使用set_input_delay和set_output_delay命令指定输入和输出延迟。用于指定输入和输出延迟的命令如下所示。

**set_input_delay –clock **

用于定义输入延迟。

**set_output_delay –clock **

用于定义输出延迟。

4.6 指定min/max delay

输入和输出延迟可以根据设计需要指定为最小或最大。

Maximum Input Delay

**set_input_delay –clock -max **

用于定义最大输入延迟。

Minimum Input Delay

**set_input_delay –clock -min **

用于定义最小输入延迟。

**set_output_delay –clock -max **

用于定义最大输出延迟。

Minimum Output Delay

**set_output_delay –clock -min **

用于定义最小输出延迟。

4.7 设计综合

compile命令用于执行设计综合。如前一节所讨论的,我们需要将设计约束、库和Verilog文件作为综合工具的输入。设计综合可以使用不同的努力水平(如低、中、高)来执行。

编译命令指定为:

**compile –map_effort **

4.8 保存设计

write命令用于保存设计。设计人员可以将综合输出保存为Verilog (.v)或数据库(.ddc)格式。该命令可以如下所示指定:

**write –format -output **

5. 约束验证

下表列出了用于验证设计的重要命令。

6. DRC、功率和优化约束

下表列出了用于指定设计规则、功率和优化约束的重要命令。

7. 本文总结

总结本文的要点:

- 设计约束包括优化约束和设计规则约束。

- 综合是从较高层得到较低层设计抽象的过程。

- 综合工具使用Verilog文件、库和约束作为输入。

- 综合工具的输出是门级网表。

- 模块级和顶层设计的约束应该记录在单独的Tcl文件中。

- Synopsys DC没有针对功率进行优化。

- 在逻辑综合过程中,目标是优化设计的面积和速度。

-

时序约束实操2024-04-28 3767

-

VIVADO时序约束及STA基础2022-03-11 11435

-

时序分析的设计约束(SDC)2022-11-08 10552

-

聊聊ASIC设计约束与SDC命令2023-07-11 1278

-

时序约束 专版2013-05-16 2751

-

FPGA的reset信号需要加什么SDC约束呢?2023-04-23 2362

-

请问时序约束文件SDC支持哪些约束?2023-08-11 778

-

介绍系统接口sdc2018-02-03 12194

-

Vivado设计套件TCL命令资料参考指南免费下载2018-08-09 1274

-

如何将Altera的SDC约束转换为Xilinx XDC约束2018-11-27 6071

-

时序分析的设计约束SDC怎么写呢?2023-06-18 6596

-

如何在Vivado中添加时序约束2023-06-23 4436

-

时序分析基本概念—SDC概述2023-07-03 8896

-

时序分析基本概念介绍—时钟sdc2023-07-05 4263

-

ASIC设计约束与SDC命令2023-07-09 1585

全部0条评论

快来发表一下你的评论吧 !