当RTL代码的接口中存在数组形式的接口时如何处理?

接口/总线/驱动

1163人已加入

描述

当在SpinalHDL中调用别人的RTL代码时,需要采用BlackBox进行封装。对于大多数场景,想必小伙伴们都已轻车熟路。今天着重来看下当RTL代码的接口中存在数组形式的接口时如何处理。

》合并数组和非合并数组

在开始之前先了解两个概念:合并数组与非合并数组。在SystemVerilog中,关于可综合的数组存在两种形式:

wire 1:0 data0; //合并数组

wire [7:0]data1[1:0]; //非合并数组

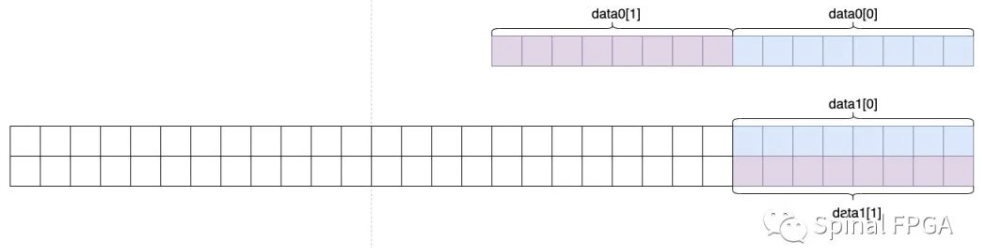

在仿真方面,合并数组是紧密排列的,而非合并数组则是按照内存对齐的形式进行排列(电路综合中则无需考虑):

相应的,合并数组则可以作为一个整体进行赋值,而非合并数组则不可以:

而合并数组与非合并数组,则可以通过SystemVerilog中所提供的流操作符进行相互转换处理(是可以综合的):

》BlackBox封装

在了解了上面的背景知识之后,再来看如何这种数组类场景如何封装至BlackBox。两条规则:

- BlackBox封装针对数组类接口仅能支持合并数组类型。

- 当接口中存在非合并数组接口时则需手动封装一层通过流操作符将非合并数组转换为合并数组。

基于上面的规则,可以进行数组接口的BlackBox封装。

看下面的RTL代码示例:

该模块输入,输出均为一个合并数组,实现功能为两个元素的数据交换。我们在进行封装BlackBox时可采用下面的封装形式:

这里我们在BlackBox中定义接口时将合并数组data_in,data_out均定义为Bits类型,宽度为合并数组中所有元素的位宽总和(2*8).

(这里面的setInlineVerilog也可不写,主要是懒得再创建一个SV文件了。

在进行调用时就可以和其他调用没有区别了:

进行仿真:

结果非常符合预期:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

stm32通过串口发送字符串存在数组里面遇到的疑问求解2024-05-14 546

-

RTL8201N系列接口电路2011-04-12 4583

-

请问循环搜索数组内容的停止如何处理?2018-08-21 2832

-

如何将接口的单个输出信号连接到LED外部和RTL代码?2019-10-16 1894

-

如何处理接口bewtween?2020-03-12 1864

-

为什么需要接口?接口电路有哪些形式?2020-12-23 3073

-

stm32如何处理数组中数据2022-02-21 1391

-

串口接收的数据存在数组里怎么解决?2023-10-27 602

-

脑机接口中基于VxWorks的ARM嵌入式系统2009-03-29 573

-

C语言教程之判断一个数是否存在数组中2016-04-25 1016

-

ADC时钟接口中的最小抖动2021-05-09 790

-

为什么要在串行通信接口中设置地线呢2022-02-02 4156

-

网络SMII接口解析2023-03-03 2762

-

原来SpinalHDL中BlackBox封装数组接口如此简单2023-05-22 1445

-

js判断是否在数组中存在2023-11-30 2179

全部0条评论

快来发表一下你的评论吧 !