科普一下先进工艺22nm FDSOI和FinFET的基础知识

模拟技术

描述

传统工艺的挑战

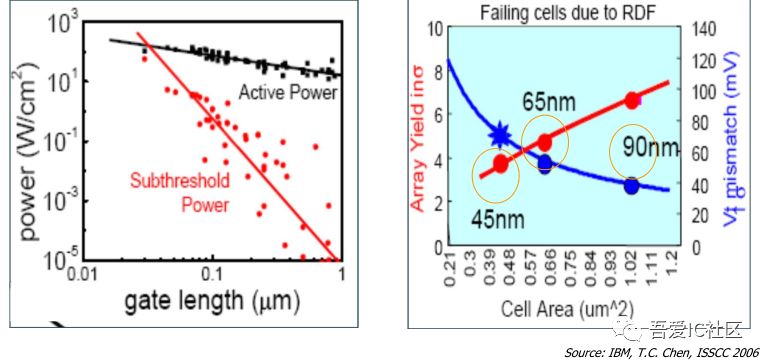

- Leakage/Power consumption issue

泄漏功率仍然是HKMG(High-K Metal Gate)一个主要问题。从下图看出,在28nm的High-K Metal Gate Stack中,leakage power仍然在总功耗中占据主导地位。因此,降低芯片leakage成为设计的重点之一。 Leakage是主要cost,直接影响整个芯片的功耗。

- 三十年内物理尺寸scaling1000倍,晶体管数量增加10的6次方,工艺制程遭遇挑战

CMOS技术走到22nm之后,因为光刻技术所限,特征尺寸已很难继续微缩,急需革新技术来维持进一步发展。在众多的候选技术之中,FDSOI(Fully Depleted SOI,全耗尽SOI)和FinFET技术极具竞争力。

对于FDSOI晶体管,硅薄膜自然地限定了源漏结深,同时也限定了源漏结的耗尽区,从而可改善DIBL(Drain Induced Barrier Lowering,漏致势垒降低)等短沟道效应,改善器件的亚阈特性,降低电路的静态功耗。此外,FDSOI晶体管无需沟道掺杂,可以避免RDF(Random Dopants Fluctuation,随机掺杂涨落)等效应,从而保持稳定的阈值电压,同时还可以避免因掺杂而引起的迁移率退化。

传统planar bulk& FDSOI& FinFET

传统bulk planar的局限性

- Channel area underneath the gate is too deep and too much of the channel is too far away from the gate to be well-controlled

- Higher leakage power(static/stand-by power)

- Gate is never truly turned off

解决方法:将channel变得更窄,使得可以被gate较好的控制。

可用的解决方案:FDSOI && FinFET

FD-SOI晶体管级优势

FD-SOI工艺可以获得较高的performance(性能比FinFET肯定还是要差点,但是比28nm提高很多),较低的leakage,power,而且成本与28nm HKPG接近。

另外,目前国内正在扶持发展FD-SOI工艺技术,对于采用这个工艺制程的企业均给与大额的补贴。所以实际上FD-SOI的芯片流片费用相比28nm还会更便宜。

FD-SOI技术不仅能得到FinFET全耗尽晶体管带给平面传统技术的全部好处,而且还能实现后者无法达到的先进的负偏压(back bias)技术。

减少寄生电容,提高器件频率,与体硅相比SOI器件的频率提高20-35%。由于减少寄生电容。降低漏电流,SOI器件的功耗下降35-70%。

FD-SOI消除了****闩锁效应 (Latch up 是指CMOS晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流。

FD-SOI工艺可以将工作电压降低至大约0.4V,而相比之下Bulk CMOS工艺的最小极限值一般在0.9V左右。使用FDSOI的后向偏置技术可以提供更宽动态范围的性能,因此特别适合移动和消费级多媒体应用。

什么是FinFET?

前台积电首席技术官和伯克利公司的前任教授胡正明及其团队于1999年提出了FinFET的概念,并在2000年提出了UTB-SOI(FD SOI)。这两种结构的主要结构都是薄体,因此栅极电容更接近整个通道,本体很薄,大约在10nm以下。所以没有离栅极很远的泄漏路径。栅极可有效控制泄漏。

FinFET原理

在鳍式场效应晶体管,该信道由一个薄的翅片由栅极在轻掺杂的薄基板包裹从三个侧面提供具有减少的漏电流和降低的短沟道效应的更好的静电控制形成。

FinFET具有由薄硅“鳍”包裹的导电沟道。

为什么我们需要FinFET?

随着设备尺寸的缩小,在较低的技术节点,例如22nm的,具有在沟道长度,面积,功率和工作电压的缩放比例,短沟道效应开始变得更明显,降低了器件的性能。为了克服这个问题,FinFET就此横空出世。

在传统CMOS器件中,沟道是水平的,而在FinFET中,沟道是垂直的。FinFET的宽度取决于Fin的高度。

在上图中,w1 = w3 =鳍的高度,w2 =鳍的厚度。

有效channel宽度=(2 *翅片高度)+翅片厚度

W =(2 * w 1)+ w 2

有效沟道长度=栅极长度= L

这种类型的栅极结构提供了对沟道传导的改进的电控制,并有助于降低漏电流并克服一些短沟道效应。

在FinFET工艺下的数字后端实现将会稍微复杂点,比如Fin必须在grid上。这就对floorplan提出了更多的挑战,比如模块boundary不能随意给,memory不能随意摆放等。

FinFET的缺点

- 工艺制程比较复杂

- 芯片流片需要更多的mask,成本急剧增加

静态 vs 动态 Body-Biasing技术

- Static: Need BB value optimization prior to implementation

- Dynamic: Can use BB optimization on the spot after implementation

在数字IC设计中,我们通常还是需要用到动态调整井偏置电压,符合low power设计要求。但是此时就需要BB Gen,这个东西还是蛮大的,需要占用芯片一部分面积。

采用了body bias技术后,除了需要增加BB Gen外,静态时序分析阶段的timing signoff也会变得更加复杂(signoff corner会增加很多)。

下图为28nm HKMG(High-K Metal Gate)与22FDX两种不同工艺的功耗与频率量化对比图。橙色曲线为28nm HKMG,中间褐色那条曲线为22FDX(不做bias),最上面那条蓝色曲线为22FDX(采用正向bias)。

从图中数据得知,在同样的频率下,采用22FDX(不做bias)工艺的功耗相比28HKMG工艺节省了近50%。而在同样的频率和同样的工艺22FDX下,采用FBB(Forward Body Biasing)的功耗较normal也节省了近50%的功耗。另外,在同样的功耗下,不同工艺下芯片的performance也相差30-40%。

22FD-SOI平台 ( 超低功耗,高性能,低成本应用需求 )

-

22nm平面工艺流程介绍2023-11-28 18866

-

科普一下CAN总线的基础知识2023-05-16 4747

-

锐成芯微宣布在22nm工艺上推出双模蓝牙射频IP2023-02-15 1388

-

22nm和28nm芯片性能差异2022-06-29 12460

-

北斗22nm芯片用途是什么?2022-06-27 4309

-

弄了个22nm的工艺配置完了之后报错是为什么?2021-06-24 1204

-

联电宣布22nm技术就绪2019-12-03 6078

-

GlobalFoundries 22nm工艺中国上海复旦拿下第一单2017-07-11 1354

-

功率和成本减半 Achronix交付先进22nm Speedster22i 系列FPGAs2013-03-04 4063

-

透视IVB核芯 22nm工艺3D技术终极揭秘2012-04-18 1537

-

台积电又跳过22nm工艺 改而直上20nm2010-04-15 1273

-

Intel 22nm光刻工艺背后的故事2010-03-24 1485

全部0条评论

快来发表一下你的评论吧 !