寄存器门电路原理分析

描述

当前行业内CMOS寄存器电路设计往往采用主从锁存器设计的结构,这与传统“数字电路设计”课程上学到的D触发器电路结构基本一致,而锁存器部分,则采用了传输门控制逻辑,这也是得益于CMOS工艺发展的成熟。

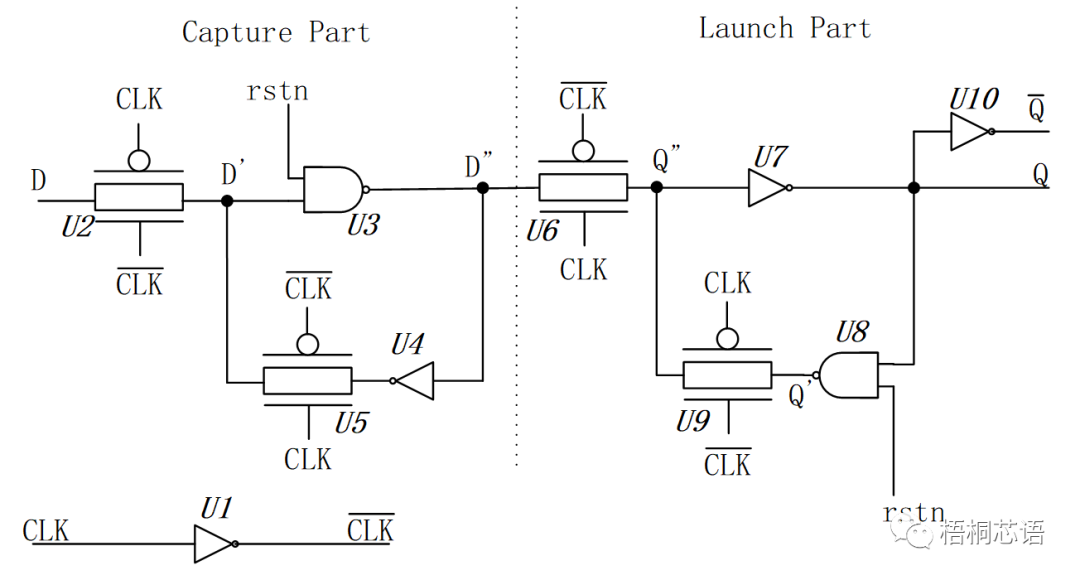

以一个带异步复位(低电平有效)的上升沿触发寄存器为例,其CMOS电路结构如下所示:

整个电路可以分为采集部分(Capture Part)以及输出部分(Launch Part)两个部分,由两个结构对称的锁存器组成,采集部分与输出部分的传输门控制信号,刚好相位相差180度(反向控制时钟),这可以保证两部分电路在控制信号为高电平或者低电平时,当异步控制信号rstn为高电平时,有且仅有一个部分电路有效。

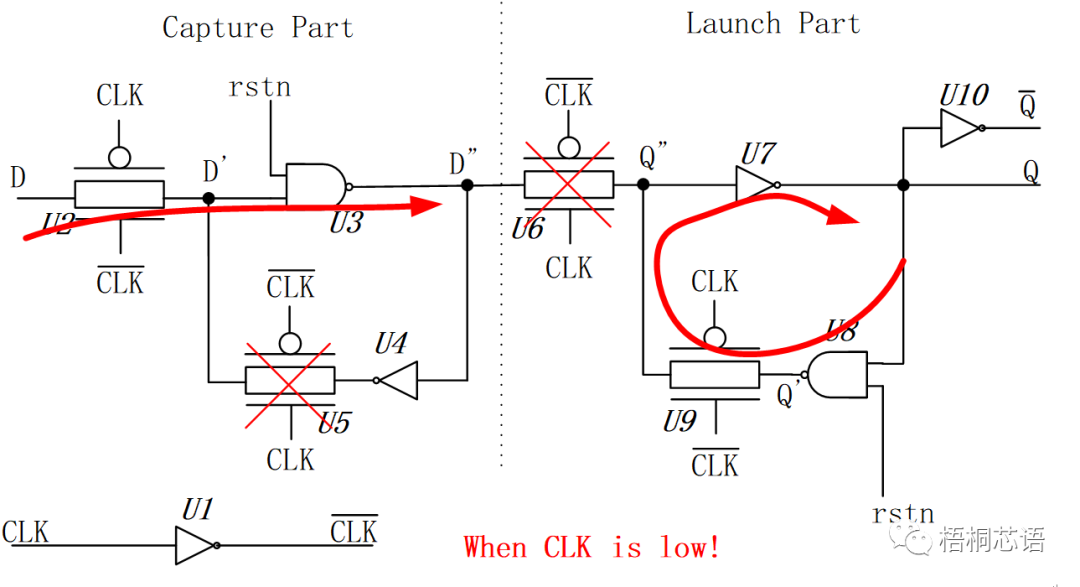

当传输门控制信号,也就是边沿触发信号CLK为低电平时,传输门U6关闭,采集部分与输出部分相互独立,处于采集状态;传输门U2打开,D端数据可以流入到D’及D’’;由于传输门U9打开,因此Q端来源于Q’’以及Q’,并形成稳定反馈环路,不会因为D’’的变化而发生变化,从而Q不会因为D的变化而发生变化。

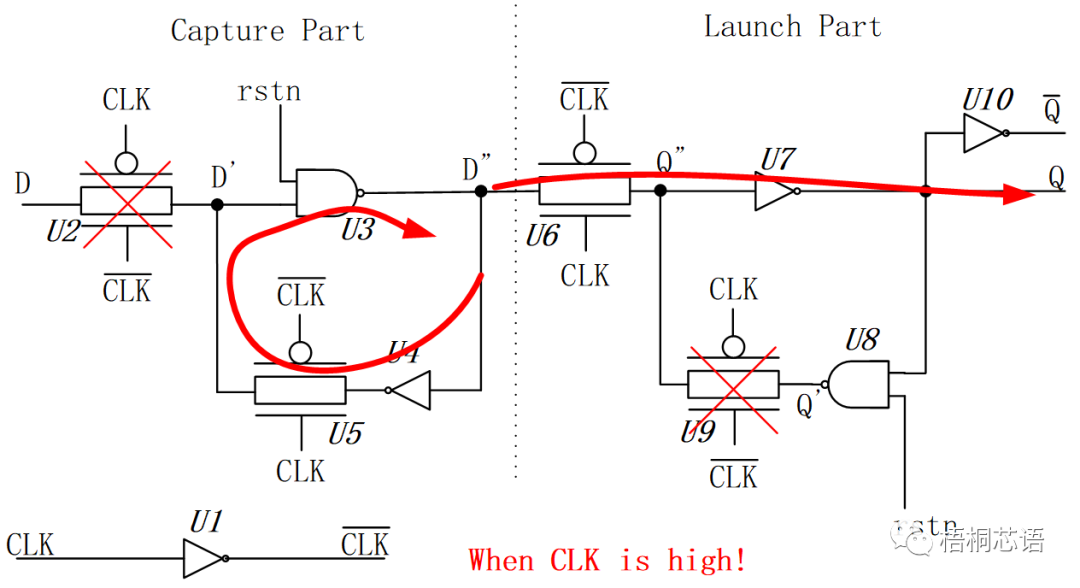

当CLK信号从低电平变成高电平(上升沿),传输门U6打开,输出部分与采集部分通路连接,D’’被传输给Q’’,并同时传递给Q端输出,从现象看,则是当CLK上升沿时,D端数据被传输到Q端输出。

CLK保持在高电平后,传输门U2关闭,D端输入与采集部分隔断,D’不会根据D的变化而发生变化,因此表现出来Q也不会因为D的变化而变化。

若CLK从高电平变成低电平(下降沿),传输门U6关闭,输出部分与采集部分的通讯再次被截断,Q端也不会发生变化。

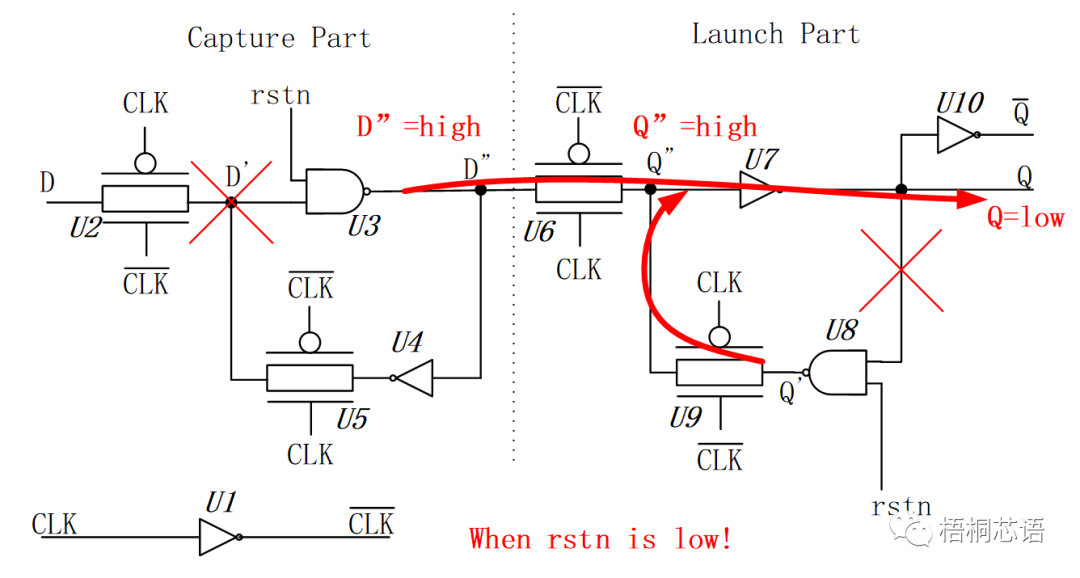

若异步控制信号rstn为低电平时,无论CLK如何变化,Q端都会保持在低电平输出。而且只要rstn从高电平变成低电平,Q端立刻复位到低电平,也不需要CLK来触发。因为在SoC设计中时钟往往会有个比较复杂的控制过程,上电后需要一个稳定时间,有一个异步复位或异步置位[1],可以在时钟稳定之前,先把整个芯片所有寄存器稳定在一个状态下,保证芯片的可控,这对于芯片验证的可靠性以及可测试性设计都有帮助。

[1] 一般来说,我们将复位为低电平,即逻辑0的行为,叫做复位,英文叫做reset;将复位为高电平,即逻辑1的行为,叫做置位,英文为set。

-

寄存器故障分析2024-08-29 2967

-

寄存器分为基本寄存器和什么两种2024-07-12 2817

-

寄存器是什么?怎么操作寄存器点亮LED灯?2023-07-21 5087

-

锁存器和寄存器介绍2023-04-18 7665

-

ARM通用寄存器及状态寄存器详解2023-01-06 9481

-

FPGA时序分析与约束(2)——与门电路代码对应电路图的时序分析 精选资料分享2021-07-26 1338

-

移位寄存器的特点_移位寄存器工作原理2017-12-22 50819

-

寄存器与移位寄存器2010-03-12 939

-

寄存器,寄存器是什么意思2010-03-08 22209

-

线性移位寄存器2010-01-12 2220

-

第二十六讲 寄存器和移位寄存器2009-03-30 10421

全部0条评论

快来发表一下你的评论吧 !