寄存器的时序要求有哪些?

电子说

描述

对于下面这个传输门来说,只有当CLK为高电平,即传输门打开时,输入端I的电平才会被传输到输出端O,这是一个正常的传输过程。

不过,传输过程不是一蹴而就的,一方面,CLK的切换需要时间(也就是我们所说的transition time),另一方面,如果在传输门打开到关闭的切换过程中,I输入的电压也在变换,而在CLK关闭后,O的输出刚好在高电平与低电平的一半,或者通俗一些说,刚好是0.5VDD。

如果这种情况出现在寄存器的U2传输门上,会发生什么?没错了,D’只有0.5VDD,那么一级一级传下去,D’’、Q’’、Q都是多少呢?

0.5VDD只是一个假设,实际上我们知道,对于CMOS传输曲线来说,当输入端电压处于一个较为稳定的接近于传输曲线中间位置,则输出端Q会出现不稳定的状态,我们就把这种情况称之为寄存器出现了亚稳态。

那么亚稳态是X[2]吗?亚稳态是中间态吗?亚稳态输出就一定是0.5VDD吗?这些问题,在任何企业、学校都会有热烈的讨论。

实际上,亚稳态既然叫做亚稳态,那么就是可能因为周围环境的不同,其输出会向一个方向偏移,比如说电子偏多的时候,可能偏向于低电平,空穴偏多的时候,可能偏向于高电平[3]。但由于不是被VDD或地直接驱动,变化速度会偏慢,实际表现就和下面这幅图一样,原本应该一下就变化的,可能需要一个缓慢的变化过程。

寄存器的setup和hold时序概念

通过亚稳态部分的介绍,我们知道,当时钟上升沿来到,并关闭输入端第一级U2传输门时,如果D端发生数据变化,有可能导致Q端输出产生亚稳态。

为了保证寄存器稳定工作,在设计电路时,需要满足两个时间窗口。

在时钟上升沿来到前的一个时间段,数据必须建立完成,这个时间称之为建立时间(setup time)。而在时钟上升沿之后一个时间段,则需要保持住数据不变化,这个时间称之为保持时间(hold time)。建立时间、保持时间与时钟的关系如下图所示。

现在大部分标准单元库设计的寄存器都采用了0保持时间或负保持时间设计,也就是保持时间为0或为负数,当然这也在某种程度上增加了建立时间的时间窗大小,降低了系统工作频率。好处是更容易帮助系统在各种不同的时序签核(Timing sign-off)条件下,快速收敛,简化了投片标准,加快了上市时间(Time to Market)。

在时序分析当中,还有一种路径上的setup time与hold time概念,与寄存器的概念类似,但意思不同,千万不要混淆了。

寄存器的recovery和remove时序概念

在建立时间和保持时间概念中,我们可以看到,当时钟触发沿到来时,为了保证电路稳定工作,需要在边沿前后一段时间保持D端数据稳定。

而对于一个带有异步复位或异步置位的寄存器来说,如果复位信号释放(从有效变成无效)与时钟触发沿同时出现,也会带来同样的问题。

当寄存器处于复位状态,且时钟处于低电平,则采集部分和输出部分由于传输门U6关闭,处于分割状态。输出部分电路,Q端输出来源于异步复位rstn驱动;而采集部分电路中,D’由于传输门U2处于打开状态,因此由D端输入,假设D端刚好与Q端数据相反,则在该实例中为高电平。而D’’则来源于异步复位rstn驱动,为高电平。

可以试想,如果异步复位释放,从有效变换成无效状态,即示例中从低电平转换成高电平,那么采集部分电路所有节点,将依靠D端进行翻转,直到稳定,其中D’’与Q’’因为传输门U6关闭,要等待CLK为高的时候才会进行传输。之后待CLK从低电平变换成高电平后,U6打开,输出部分电路再根据D’’进行翻转,直到Q端输出高电平,完成复位后,时钟上升沿触发工作效果。

但是如果在异步复位rstn释放的同时,时钟CLK出现上升沿,则可能出现U2还没有关闭,但U5已经打开的情况,D’会因为D为高电平以及D’’为高电平发生冲突。如果当U2完全关闭后,D’未完全稳定在某个状态,则可能导致后面电路失效,Q端在此出现亚稳态的情况。

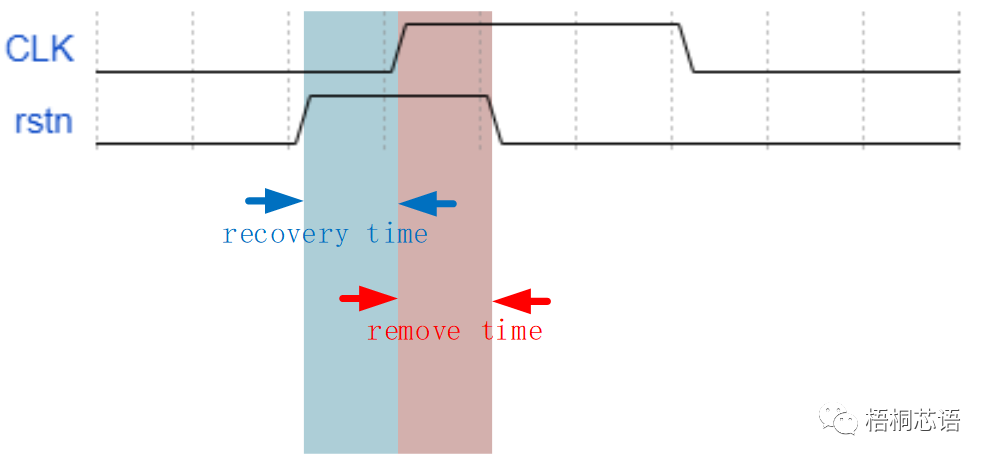

因此与建立时间与保持时间类似,对于带有异步复位或异步置位的寄存器来说,异步复位也需要在时钟上升沿到来之前的一个时间窗稳定下来,称之为recovery time,而在时钟上升沿后一段时间内保持住,称之为remove time。

-

寄存器分为基本寄存器和什么两种2024-07-12 3249

-

寄存器属于时序逻辑电路吗 寄存器是什么逻辑电路2024-02-18 3778

-

什么是移位寄存器?数字电路中的寄存器类型有哪些呢?2023-09-20 10064

-

Verilog设计寄存器2023-07-27 5194

-

寄存器的工作原理2023-02-20 10188

-

寄存器的作用以及复位2023-01-30 8791

-

GPIO寄存器2021-12-08 1402

-

寄存器与内存的区别2020-12-31 10952

-

寄存器与移位寄存器2016-05-20 1299

-

ARM寄存器详解2010-07-10 3306

-

寄存器,寄存器是什么意思2010-03-08 22414

全部0条评论

快来发表一下你的评论吧 !