RTL电路的设计原则和方法

电子说

描述

既然RTL是寄存器传输级电路,那么电路设计就一定是以寄存器的特性为基础进行设计。

一般来说,RTL电路设计我们建议3个主要的原则:

- 时序逻辑与组合逻辑分开

- 数据路径与控制路径分开

- 先画电路,后写代码

以上3个原则,我们一个一个来看。

时序逻辑与组合逻辑分开

这里涉及到数字电路基础知识,不懂的小朋友还是先把数字电路设计原理学一下。我们一般把寄存器(DFF)以及锁存器(LATCH)看做是时序逻辑,也就是数据输出与时钟变化保持有一定的关系。具体的原理,可以参考之前关于寄存器工作原理分析的部分。而组合逻辑,则输出与时钟没有关系,仅仅因为输入信号的变化,会立即产生变化,如选择器、与门、或门、非门等。

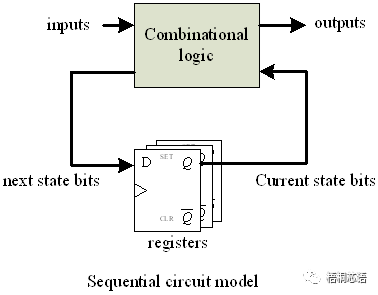

如下图所示,就是一组完整电路的功能框图模型:

其工作原理为:

(a) current state bits=↑(next state bits);

(b) next state bits=f1(inputs,current state bits);

(c) outputs=f2(inputs,current state bits);

这里面f1和f2就是分别算出next state bits以及outputs的组合电路功能。可以明确的电路,在这里就是时序逻辑电路,或者说是寄存器。所以我们在描述电路的时候,先描述寄存器就好:

接下来我们看,组合逻辑电路怎么设计。

数据路径与控制路径分开

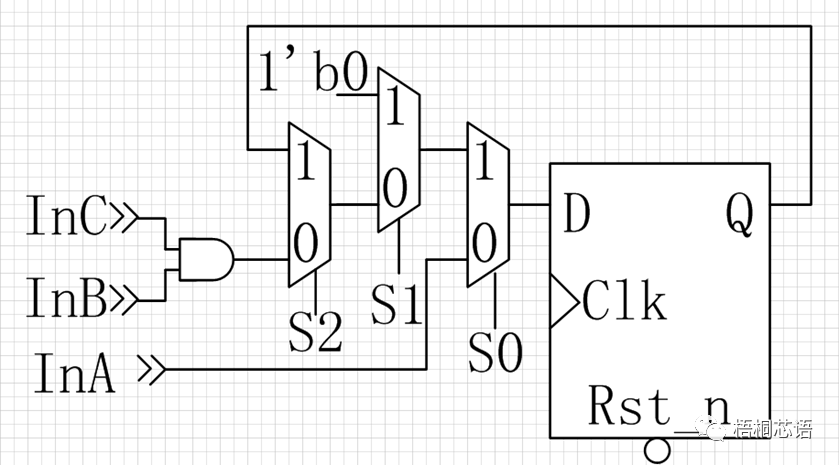

假设我们想描述以下电路:

那么时序逻辑的输入,也就是D端怎么获得?在正常的思考情况下,我们一般这样考虑问题,是有逻辑的:

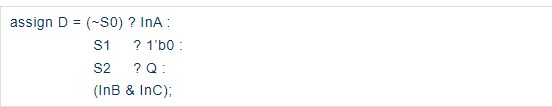

如果满足XX条件(这里假设S0为0)那么D端来自于InA,否则如果满足XX条件(这里假设S1为1)则赋值为1'b0,否则如果满足XX条件(这里假设S2为1)则来源于InC跟InB的与逻辑,否则就保持不变。

这种数据来源的逻辑思考,利用选择器实现成电路,就是数据路径的设计思路。而利用VerilogHDL来描述电路,就只需要用assign以及?,:的组合,实现选择器的功能即可。而Synthesis综合工具,会根据最终的电路进行优化,实现最优的组合逻辑结构。对设计者来说,首先能做用选择器来设计数据路径就可以了。

而S0、S1跟S2是怎么来的?设计S0、S1跟S2就相当于这个电路模型组合逻辑的控制逻辑设计。

当然S0、S1、S2又可以看做一种数据路径进一步扩展设计,他们可能是组合逻辑直接赋值,也可能是时序逻辑寄存器的输出。

先画电路图,后写代码

由于前些年软件与互联网产业的蓬勃发展,越来越多的人都把软件视为生产力第一工具,却忽略了工程师的主观能动性。越来越多的年轻人投入到集成电路设计领域往往只是学习了VerilgHDL语言,就开始编写电路。殊不知这样的电路,往往会面临大量不可预知的bug,以及调试人员茫然的眼神。

也许有同学说了,现在有很多代码风格(coding style),写电路的时候按照标准的代码风格写就好。也许作为一个接近20年电路设计经验的老工程师来说,心中的电路已经非常清晰,按照coding style编写的电路还是比较好的,但仍然会因为电路逐步复杂,有些部分无法把握,会遇到疏漏。

在这里我还是呼吁各位同学,先把电路设计功底做好,再考虑如何用描述语言描述出来。至少,这个才叫做电路吧。这样做的好处主要有以下3点:

逻辑清晰,便于表达及传递思路

电路直观,便于Debug以及修改

信号定义明确,Coding只需照抄

RTL电路设计的方法

其实根据RTL电路设计的原则,我们认为一个已知接口信号以及功能定义的模块,可以从输出开始往输入推着写。

比如说,我们要设计一个4bit计数器,其功能要求如下:

- 从0到15循环计数

- 加电平输入信号P_M,P_M为1则往上加,P_M为0则往下减

- 加脉冲输入信号Clr,Clr脉冲(高有效)来到,则计数器输出为0

- 加脉冲输入信号Load,电平输入信号DIN[3:0],Load脉冲(高有效)来到则计数器输出加载为DIN[3:0]的值

- 增加一个电平输入信号Hold,当Hold为高电平时,计数器保持当前值,不做增减。

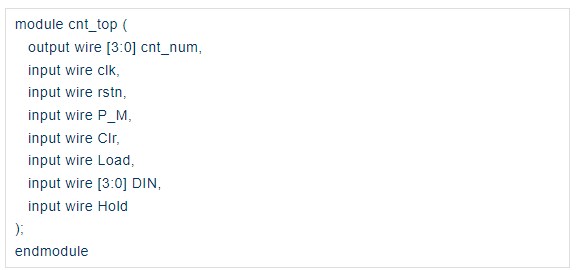

那么首先我们分析这个寄存器的输入输出。

输出就是0~15的数值,需要4bit输出信号cnt_num,而输入除了时钟复位(clk,rstn)外,有P_M,Clr,Load,DIN[3:0]以及Hold。因此我们先把输入输出整理出来。

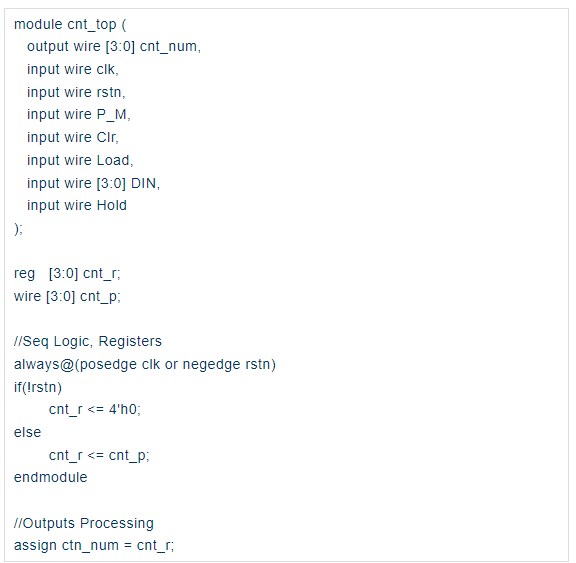

接着我们从输出设计开始往回(输入)推导,先定义输出需要的寄存器来存储每个周期变化用的计数值,cnt_r,并描述出来:

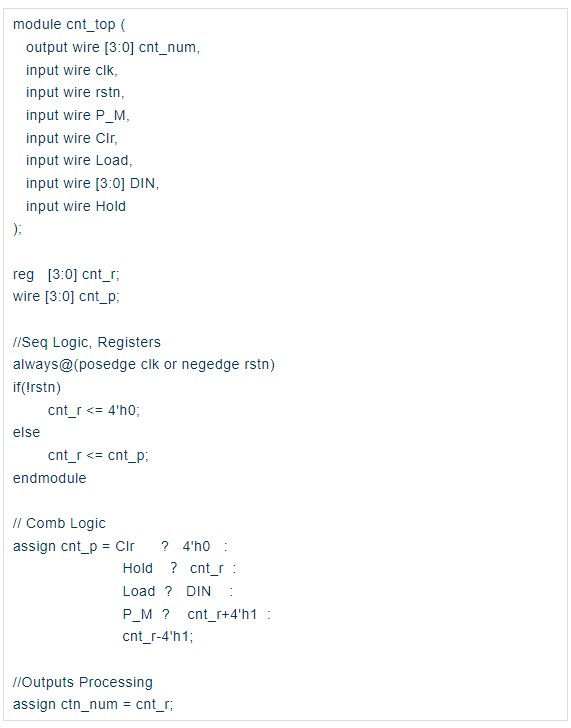

接着,根据功能定义,描述时序逻辑输入端的数据路径:

由于所有控制信号来源于输入,这个电路可以不做控制路径的设计。但有心的小伙伴应该发现了,如果Hold为高,则想加载DIN是无法实现的。因此这样设计的电路,其实是存在优先级的。需要与模块定义的朋友做深入交流,确保实际功能使用时不会出错。

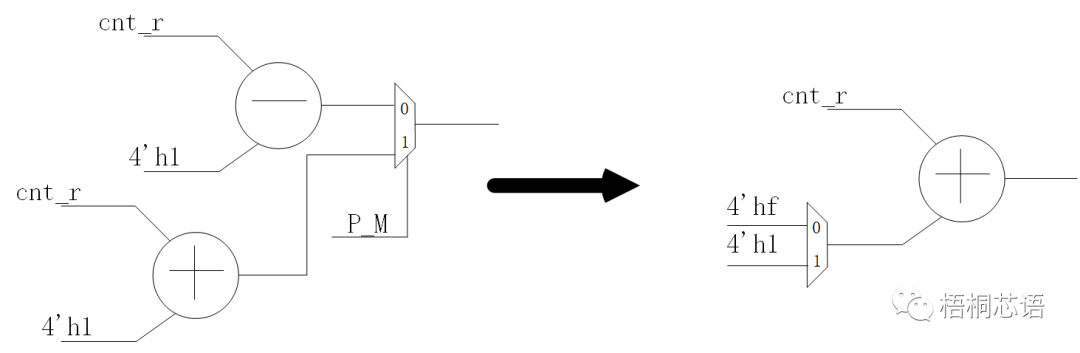

同时,我们看到这个电路里用到了1个加法器和一个减法器,如果想进一步优化电路面积,我们可以考虑加法器的复用:

这样做电路应该怎么改呢?留给大家去思考了。

复杂电路系统设计方法

现在又要有小伙伴说了,我们的电路很复杂的,如果每个都画出电路,那什么时候能投片。我的理解是,复杂电路都是简单电路的衍生,按照功能将系统进行框架划分,并定义出每个框架之间的接口信号及其时序要求,接着再通过画电路的方法,设计框架里的电路。有些小的电路实际上是会被复用的。每个公司产品线,大部分时间都会处于一个逐步演进的过程,小电路设计多数是刚开始,后续的工作量会逐步降低。

但如果公司从一开始就不重视画电路,只是电路描述做实现,也许前几款产品可以正常跑,过了一段时间,客户可能突然发现有些地方要优化,有些地方有bug,但之前设计人员可能已经离职。电路描述不好,电路图也没有,这个时候负责优化和解bug的小伙伴一定会郁闷的。

-

集成电路的替换方法及原则2012-04-01 5126

-

RTL8201N系列接口电路2011-04-12 4583

-

RTL8308+RTL4204交换机原理图2010-10-18 2600

-

RTL TTL探头电路图2008-12-24 1411

-

RTL,RTL是什么意思2010-03-08 14813

-

设计复用的RTL指导原则2011-12-24 729

-

RTL8710模块常用使用方法2016-05-25 2152

-

RTL8111E和RTL8105E应用参考电路pdf下载2018-03-07 3511

-

RTL8306SD和RTL8306SM应用参考电路pdf2018-03-09 2324

-

RTL8111E和RTL8105E网卡驱动芯片的电路原理图2020-01-10 11778

-

RTL8111E和RTL8105E网卡电路原理图免费下载2021-01-13 5870

-

RTL8187和RTL8225USB无线网卡电路图与RTL822电路图2022-09-07 1686

-

RTL8211 DEMO电路参考设计2023-01-29 1598

-

专用集成电路的设计原则 专用集成电路的设计方法2024-05-04 3229

-

电路板检修方法的原则是什么2024-05-29 1780

全部0条评论

快来发表一下你的评论吧 !