什么是三态电路?三态电路及其使用

电子说

描述

什么是三态电路

一般来说,我们认为CMOS数字电路的输出的稳定状态只有2种,就是逻辑0和逻辑1,从模拟信号量来说,就是0V和VDD。

那么有些小伙伴会说了,实际上输出状态还有Z态和X态。

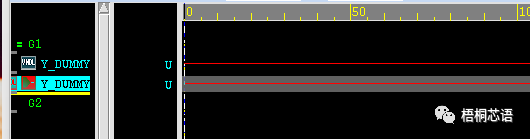

Z态表示没有驱动时信号的输出,又被表示为高阻状态High-Z,在仿真波形上,喜欢用一条处于中间位置的线条表示,有的工具用黄色线条,有些工具用红色线条。

而X态,则表示输出状态不是逻辑0,也不是逻辑1,在仿真波形上,往往用一种红色块表示。如下图所示:

从仿真信号来看,这样的描述是为了区分稳定输出的信号逻辑状态,但客观世界里,并不存在X态以及Z态这两种信号状态。只是在不稳定的情况下,由于外界不确定的驱动因素,会使得输出状态向逻辑0或逻辑1漂移。

一般来说如果想避免这种Z态或X态,那么就必须确保信号有,且只有一个驱动源在驱动。(亚稳态也是导致Z态或X态的一种原因,但在那个时候,其实就是存在多个驱动,或没有驱动的情况)

峰回路转,那么这里想说的三态电路,又是一个什么鬼呢?我们看下面这个电路结构。

上图所示,就是一种三态输出电路,当Enable为VDD的时候,输出电压Vout与A端输入电压保持一个逻辑电平转换。但是当Enable控制信号为0V,也就是逻辑0时,无论输入电压A端怎么变化,输出反相器的PMOS和NMOS都处于关闭状态,Vout就没有驱动了。

刚才我们说过,如果信号没有驱动,就是输出高阻态High-Z,那么Enable为逻辑0的时候,Vout就是High-Z。

这种可以输出第三种逻辑状态的电路,我们称之为三态电路。在数字逻辑设计中,原则上只有IO电路上可以使用,常规的RTL设计,是不允许使用的。

如何让High-Z从不稳定走向稳定

既然High-Z是一种因为没有驱动而导致无法使用的不稳定信号逻辑,那么又怎样去使用呢?

因为三态电路常被用于IO Buffer的电路中,因此一般来说,我们会在Vout输出上加一个上拉电路或下拉电路。当Enable无效时,Vout通过一个弱上拉或弱下拉连接到VDD或地上,使其稳定到VDD或0V。

如下所示,是某工艺下数字逻辑IO Cell的电路示意图,当OEN为1'b1的时候,A端数据是无法送到P(即PAD)端的,但通过配置PUN为逻辑0的时候,则P端被拉到了VDD,即逻辑1上,确保了稳定的输出:

FPGA上如何使用三态电路作为IO

一般来说,ASIC设计时,有专门的IO Buffer可以实现三态IO电路,实例化在电路中即可。但FPGA没有,可以使用以下Verilog HDL实现:

注意这只适用于FPGA,同时要在IO约束文件里设置PULLUP或PULLDOWN可配置上拉或下拉。

使用BUSKEEPER对三态输出做保持

有些早期设计的片内嵌入式存储电路,其输出口仍然会使用三态输出,原本是为了降低功耗(还没输出时,关闭输出驱动管),但这也导致输出端出现High-Z,无法直接连接到数字逻辑上。

这个时候就可以在每个可能出现三态逻辑的输出信号上,接一个叫做buskeeper的电路逻辑,有时候又叫busholder。

Buskeeper用了一对驱动力大体一致的反相器组成反馈,当内部关闭输出后,原本在信号上的逻辑1或逻辑0,就可以被保持住。确保数字逻辑中不存在高阻或不定态。

注意驱动能力

无论上拉或下拉,我们都会说 弱上拉 ,或 弱下拉 ,这是什么原因呢?

我们看下面这个IO,当输出使能关闭后,DRVP以及DRVN都处于OFF状态,VDDPST通过上拉PMOS,PUMOS,为电容充电,使得PAD达到VDDPST的电压值,也就是逻辑1。

如果打开输出使能,并想输出逻辑1,如下图所示,因为驱动管DRVN关闭,因此VDDPST通过DRVP以及PUMOS同时向电容充电,时PAD达到逻辑1。这个还是比较好理解的。

但是如果我们想输出逻辑0呢?由于上拉管PUMOS与驱动管DRVN同时打开,那么同时会有VDDPST通过PUMOS向电容充电,以及电容通过DRVN向地放电的两条通路。如果想让PAD达到逻辑0,那么必须是放电通路的能力远远大于充电通路。

由此可见,必须使用较大的上拉或下拉电阻,或者使用驱动能力较弱的上拉或下拉晶体管,才更可能使PAD在输出逻辑0的时候,更容易接近于地电平。

所谓驱动力,其实就是电流,对于电阻来说,电流就是电压与电阻的比值:

I=(VDDPST-VPAD)/R(I是驱动电流,VDDPST是IO的供电电压,而VPAD是PAD上的电压,理想结果是无限趋近于0V,R则是电阻的阻值)

由此可见,在假设VPAD无限接近于0,则希望电流越小(驱动力越小),则上拉或下拉电阻的阻值就需要越大。

而对于MOS来说,如果假设VPAD的电压无限接近于VDDPST或0V,则上拉或下拉晶体管处于饱和状态,可以提供电流的公式为下图中饱和区的计算方式:

根据公式可以看出,如果在一个特定工艺的芯片内,想减少电流,就是减小宽长比W/L的数值。

需要注意,因为PMOS的迁移率只有NMOS大概一半的样子,因此在设计电路时,下拉器件的选择尤为重要。经验不足的工程师,往往会在下拉驱动选择上翻跟头。

给大家一个问题思考,如果芯片内的下拉驱动能力比较强,后期芯片无法输出稳定的逻辑1,我们能不能通过板级设计解决这个问题呢?

电平适配电路

我们一般都认为IO的输出电压就是芯片供电的Post-Drive电压,如果驱动芯片A的Post-Drive电压VDDPSTA是2.5V,则VOH为2.5V,但接收芯片B的Post-Drive电压VDDPSTB是3.3V,VIL为2.7V。如何让接收信号稳定的接收到驱动逻辑电平呢?

这里可以巧用三态IO,当CHIPA要输出逻辑1的时候,不是通过驱动管输出逻辑1,而是输出一个High-Z状态,这个时候PAD上的信号就没有驱动了。在片外增加一个上拉电阻,并连接到VDDPSTB上,则此时PAD上的电压VPAD就会因为VDDPSTB通过板级上拉电阻向电容充电而上升到VDDPSTB上,并稳定为CHIPB提供逻辑1。

但也要注意一个问题,就是如果VDDPSTB比VDDPSTA高的太多,那么就要注意会不会因为VDDPSTB到地的电压过大,或者VDDPSTB到VDDPSTA的电压差过大烧坏了DRVN或DRVP。

通过上拉电阻输出逻辑1,或者通过下拉电阻输出逻辑0的三态IO Buffer,在GPIO以及I2C等通讯接口上是经常被用到的。具体电路,具体分析。

-

关于晶振的三态2025-05-15 4866

-

三态门电路的输出有哪三种状态2024-07-30 9722

-

三态单片机IO的三态是指什么2021-11-25 3297

-

三态输出门的电路图是什么样?2019-10-25 2042

-

什么是三态电路 三态电路有什么特点2019-05-21 7705

-

三态门怎么理解2019-03-10 19310

-

高阻态与三态门的电路原理分析2019-01-08 7101

-

三态门逻辑电路图大全(三款三态门逻辑电路图)2018-03-01 81606

-

三态电路在FPGA应用设计中的分析2010-08-06 688

-

三态MOS动态存储单元电路2009-10-10 1446

-

三态输出门的电路图和图形符号2009-07-15 3527

-

三态声光逻辑笔电路图2009-05-19 885

-

什么是三态门? 三态逻辑与非门电路以及三态门电路2008-05-26 49853

全部0条评论

快来发表一下你的评论吧 !