如何通过一个电容解决时钟辐射超标问题?

描述

一引言

在电磁兼容的辐射发射测试中,最常见的就是时钟辐射超标,随着系统设计复杂性和集成度的大规模提高,电子系统的时钟频率越来越高,处理的难度也越来越大。时钟辐射的症结在于,时钟信号对应的频域为窄带频谱,能量比较集中,在数据上体现为离散的有倍频特性的频点,而高频信号本身就很容易通过各种方式对外辐射。本文将结合具体案例分享如何通过一个电容解决时钟辐射超标问题,并提出面对时钟超标问题时可行的措施。

二案例背景

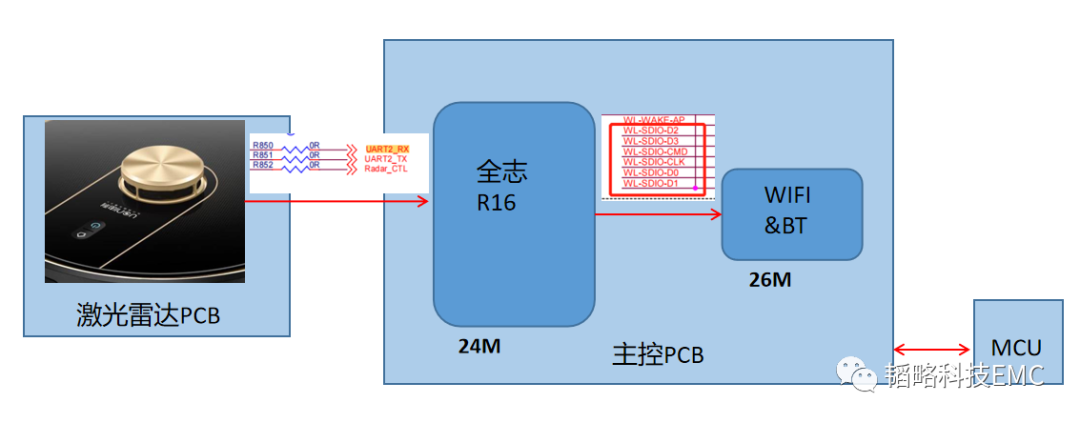

客户的一款扫地机器人在做辐射测试时,出现750MHz频点数据余量不足的情况,希望针对这个频点进行优化。简要的电路架构如下:

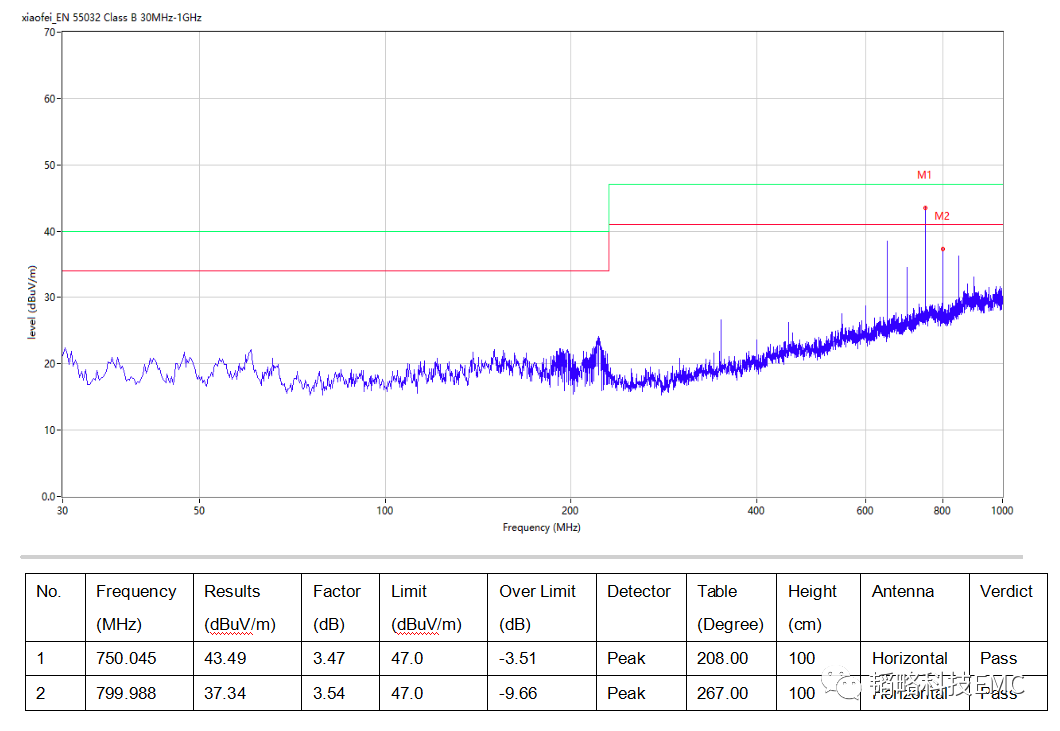

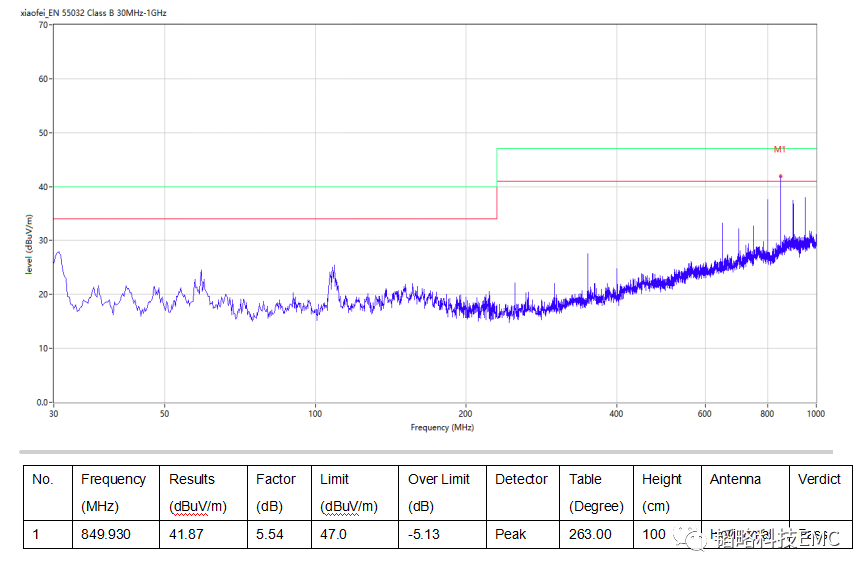

以下是通过韬略实验室复测后的其中一个实验数据:

从数据可以看出,750MHz这个频点确实比较高,前后离散分布的其他频点的频率差为50MHz,说明产品上存在以50MHz为基频工作的电路模块。

三整改过程与对策

1.查找源头 利用频谱仪进行排查,通过近场探头扫描发现定位到模块R16到WIFI芯片的时钟信号WL-SDIO-CLK的时钟频率刚好就是50MHz,其他模块没有这个频点。

2.辐射路径判断

除了时钟信号线WL-SDIO-CLK测得到50MHz的时钟倍频,通过探针探测,发现R16到WIFI芯片的数据信号线也能测到这些时钟频点,初步判断噪声源头为R16到WIFI的时钟信号,并耦合到数据通信信号。

3.整改过程

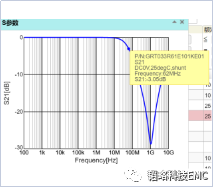

通过RC对时钟线和信号线进行滤波处理,越靠近R16芯片端越好,实际由于PCB布板空间问题,所以一开始只对时钟线做滤波处理,电容用100pF,主要考虑该电容的谐振频率点在1GHz左右,对750MHz频段可以起到较好的效果。

效果如下:

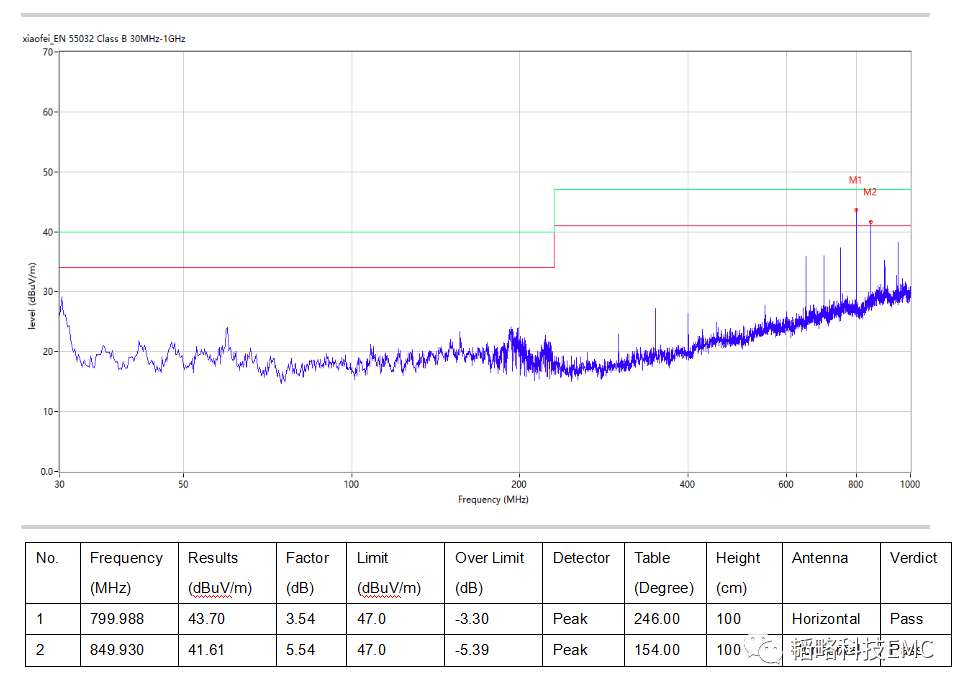

频率向更高的800MHz移动,考虑到拆装机的影响,说明只对时钟信号处理并没有起到很好的效果。后尝试对信号线加56pF电容滤波,数据如下:

可以看到,对800MHz及之前的频点有效果,但对850MHz这个频点并没有很好的改善效果。受空间限值,如果要针对时钟信号和数据信号走线做优化走线和滤波处理,需要配合改板,将滤波电容位置靠近R16芯片端,预留位置做RC滤波。

4.尝试查找是否存在其他辐射路径

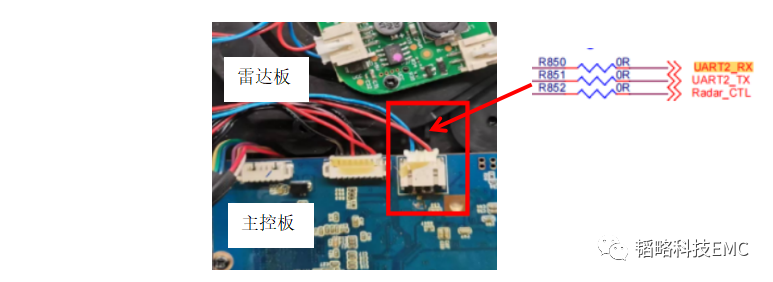

利用近场探头再仔细探查,主要针对排线和PCB板之间的信号连线,因为这些都是比较常见的辐射路径。通过排查,发现如图所示信号线有50MHz的倍频点:

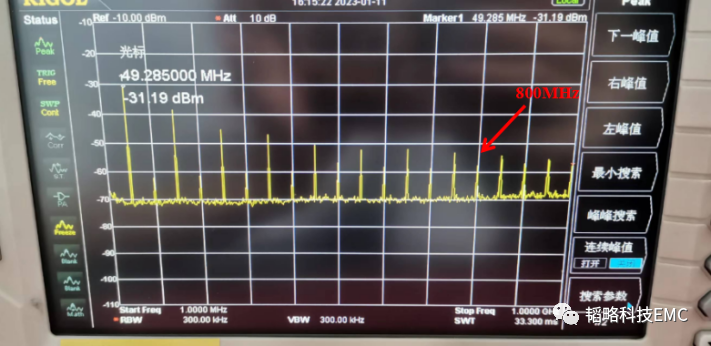

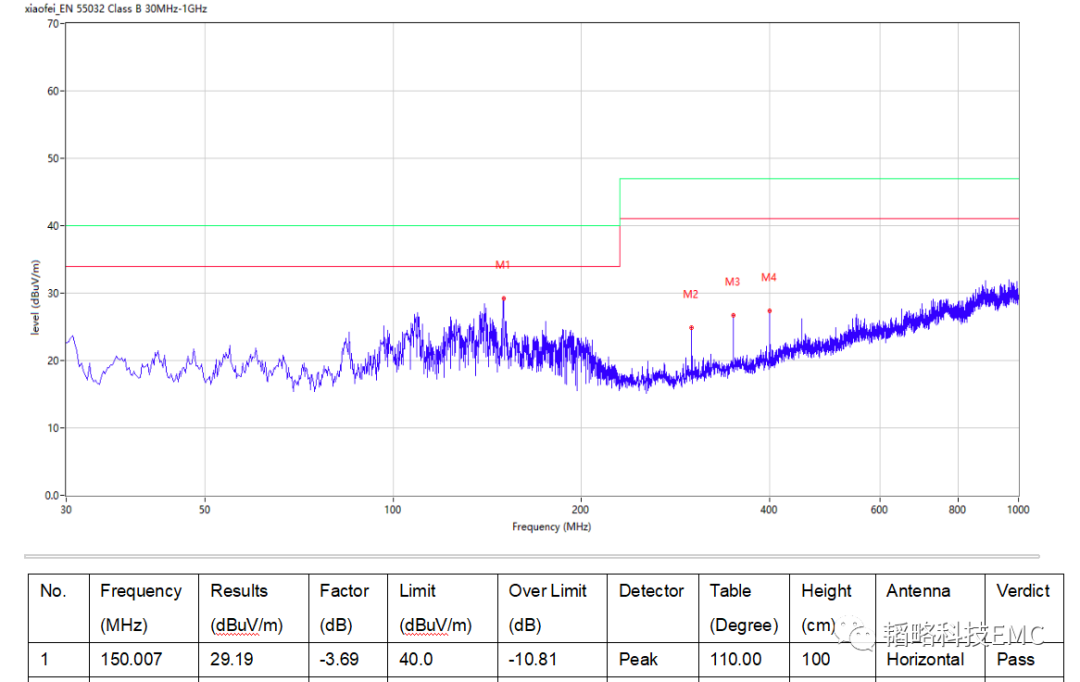

通过频谱探针进一步确定,信号引脚UART2_RX作为R16芯片与雷达模块的信号通信接口,耦合到了高频时钟噪声,成为了辐射天线之一,通过将该引脚对地加100pF电容滤波,结果如下:

从数据可以看出,高频段的噪声频点都没有了。

最终的整改措施只在UART_RX引脚处对地加100pF电容,整改用到的设备和器件有:频谱仪,近场探头,探针,电容。

四总结

本次整改只用一个电容便解决了高频时钟辐射问题,但整改过程却有很多值得反思总结的点,通过反思本次整改过程,针对时钟问题可供参考的经验总结如下: 1.时钟问题根源思考 高频时钟及其倍频容易出现以下几个问题: (1)通过信号本身PCB走线或信号环路形成对外辐射的天线; (2)串扰到靠近时钟线的走线; (3)耦合到排线,排线又是时钟辐射的良好天线; (4)最不好处理的,是在芯片内部串扰可能就已经发生,导致芯片IO口都带有高频信号噪声。 2.辐射路径排查思路 (1)通过测试数据,可以大致判断超标频率的基频; (2)如果基频跟电路已知工作频率一致,可以快速对该电路进行验证; (3)可以通过频谱仪,结合近场探环和探针,锁定时钟源头。 3.处理与验证 通常越靠近源头处理效果越明显,措施也会相对较少。 (1)直接对时钟进行展频处理,目前常见的展频手段有软件展频和通过硬件电路展频,硬件电路展频可以了解韬略科技的产品:展频IC和展频晶振; (2)在设计阶段,对时钟走线做包地处理,通过走线屏蔽减少其对外辐射和串扰的能力; (3)整改阶段,需要先排查噪声源头,同时也要尽量评估所有可能成为辐射天线的走线和排线,避免陷入对某个问题点反复验证,却不尽人意的死循环之中。

审核编辑:刘清

-

DCDC引发EMI辐射超标的整改案例2024-03-11 3747

-

如何使用频谱仪解决高频时钟辐射超标问题2024-04-16 2937

-

DCDC BUCK通过加RC Snubber解决EMI辐射超标的仿真和实测数据分析2025-04-27 617

-

[求助]关于线缆辐射发射超标的问题2009-01-14 7339

-

EMC辐射超标,内部时钟频率超标怎么解决?2016-09-19 31399

-

车载逆变器低频辐射发射超标求助2017-02-11 6227

-

AD9629输出30M时钟倍频辐射超标2018-11-13 5602

-

电磁兼容(EMC):如何高效解决辐射发射时钟超标问题?2020-04-22 4445

-

如何高效解决辐射发射时钟超标2023-05-17 3353

-

一个电容搞定高频时钟辐射超标问题2023-06-27 3409

-

时钟辐射超标怎么解决?2023-09-12 2105

-

时钟辐射超标整改方案2023-09-19 2626

-

EMC整改如何解决时钟辐射超标问题2023-10-31 3816

-

摄像头时钟辐射超标问题整改案例2024-07-16 3649

-

行车记录仪时钟辐射问题整改案例2025-01-21 1883

全部0条评论

快来发表一下你的评论吧 !