ALD在高深宽比器件制造上不可替代的应用

描述

在集成电路领域中,深宽比被定义为刻蚀深度与刻蚀图形CD(Criticlal Dimension)的比值。CD是IC制造中的一个重要指标,通常与刻蚀的特征图形的尺寸相关联,包括有浅槽隔离的间隙、晶体管的沟道长度、金属互联线的宽度等。随着高密度集成电路特征尺寸的不断减小,对于高深宽比的间隙进行均匀、无空洞,填充淀积工艺显得至关重要。

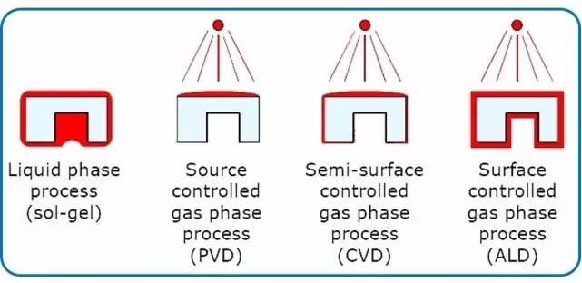

以3D NAND为例, 其复杂结构需要高的深宽比镀膜工艺,例如叠层沉积、高深宽比通道/通孔沉积和台阶沉积等等。这类非平面结构对沉积工艺的要求很高,常见的物理气相沉积(PVD)/化学气相沉积(CVD)的成核生长机制已经难以满足。

ALD与其他制膜技术对比(图片来源网络)

不同于传统的沉积方式,原子层沉积(ALD)的反应机制是逐层饱和反应,这种表面反应具有自限性,通过累积重复这种自限性可以制备所需精确厚度的膜层,并且具有良好的台阶覆盖率及厚度均匀性,连续生长可以获得致密性高的纳米薄膜。

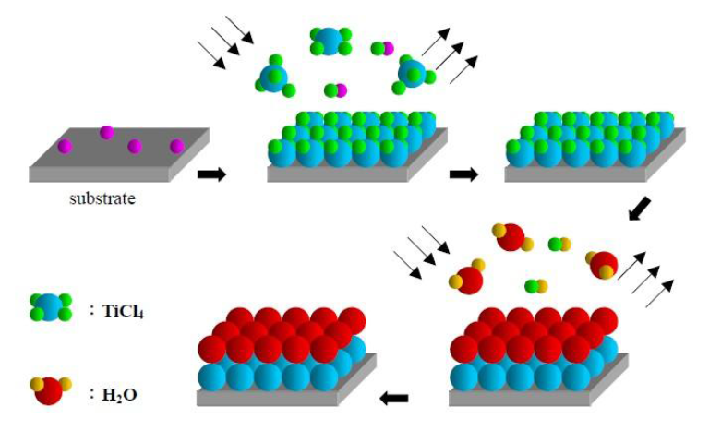

使用TiCl4和H2O制备的TiO2(图片来源网络)

基于表面饱和化学性吸附及自我限制的反应机制,原子层沉积(ALD)拥有下列优点:

通过对生长循环数的控制,可以精确控制目标膜厚

通过对前驱体流量的稳定性/均匀性控制,可获得较高致密性的薄膜

对于具有高深宽比结构的器件/材料,ALD具备良好的侧壁覆盖能力和阶梯覆盖能力,沉积保形性较好

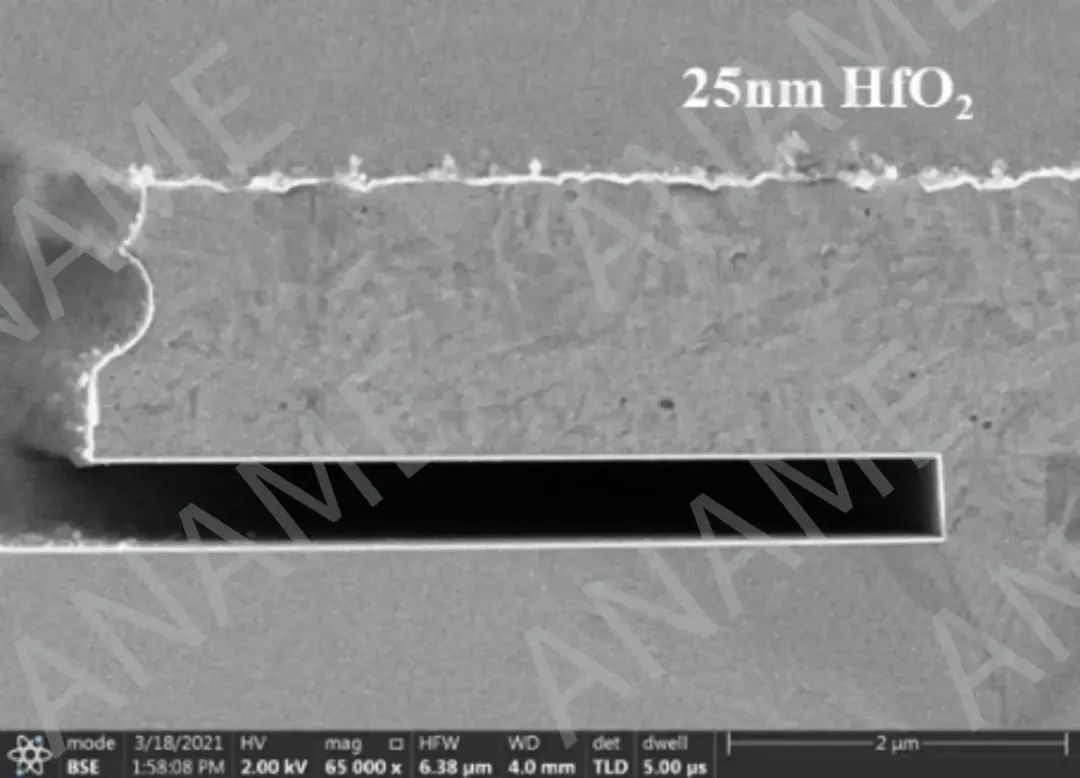

结合原磊技术团队成员多年的经验积累,并经过不断的优化和实践,原磊将ALD在深宽比器件制造的理论优势,用自己的技术和产品充分展现出来。原磊第二代研发型ALD设备Elegant-Y/A系类产品,在不改变腔体的前提下满足O3/Plasma/Thermal三种工艺的任意切换。针对高深宽比结构的材料/器件,设计了独有的FV-ALD工艺,给反应前驱体提供一个更加稳定的腔内气流环境,针对高深宽比的结构,有效扩大了阶梯覆盖能力以及样品表面膜层的均匀性,可以实现深宽比1:1000的沟道内Al2O3、HfO2和TiN的均匀致密沉积。

ELEGANT II-Y300

图1展示了Elegant-Y300系列ALD产品在Floating型沟道结构内沉积25nm HfO2薄膜的SEM图片。图2中展示了放大倍数的HfO2薄膜,可清晰地看到其致密均匀的沉积效果。.

Figure 1:高深宽比为1:1000沟道结构25nm-HfO2薄膜的SEM结果

Figure 2:高深宽比为1:1000沟道结构25nm-HfO2薄膜厚度测试结果

经过前期大量的工艺验证和研发,我司也摸索出一系列ALD制备氧化物、氮化物和金属的成熟工艺,包括:

氧化物

Al2O3、TiO2、SiO2、HfO2、Ta2O5、ZrO2、ZnO、SnO2、La2O3

金属

Fe、Ag、Co、Ni、Cu、Ru、Pt

氮化物

多元材料

TiN、TiC、GaN、AlN、HfON、LaAlO3、MnN、TaN、WN、Si3N4等

我司目前主要产品是研发和量产型原子层沉积(ALD)设备,其中GRACE MX系列和ELEGANT II-A系列机型均可成熟量产。

GRACE MX系列

原磊自主研发的第一代多层平板式原子层薄膜沉积(ALD)系统。支持全方位的工艺开发,且最大可容纳样品尺寸及层数可根据客户需求量身定制。

成熟量产型机台,可使用标准或自定义的 Cassette一次性装载25片6/8寸英寸晶圆。在化合物半导体领域,我司利用ALD技术开发出独特的处理工艺-即ISSET技术,能够大幅提升功率器件的电学性能。

审核编辑:刘清

-

ALD主板故障的维修2010-01-05 2423

-

揭秘TVS管在ESD静电防护中不可替代的贡献2019-03-11 3550

-

DFM实例分享-替代料审查2022-01-20 22020

-

电接枝技术助力高深宽比TSV2011-01-14 2399

-

激光切割技术在汽车制造业中不可替代的七大优势2020-09-15 3084

-

泛林集团推出先进介电质填隙技术,推动下一代器件的发展2020-09-23 1076

-

思锐智能专注ALD创新,助力超越摩尔2021-05-30 5607

-

SRII重磅亮相CICD 2021,以先进ALD技术赋能第三代半导体产业2021-11-10 1664

-

Beneq和LZH合作开发空间ALD系统,可快速在复杂光学元件上镀膜2022-12-22 5933

-

ALD技术工艺原理、优势及应用2023-10-18 11022

-

拓荆科技:超高深宽比沟槽填充CVD产品首台已通过客户验证2024-09-25 1315

-

接触孔工艺的制造流程2024-11-15 2580

-

用平面锥制造100μm深10μm宽的高纵横比硅通孔2024-12-09 2443

-

半导体制造里的ALD工艺:比“精”更“精”!2025-01-20 5402

-

ALD和ALE核心工艺技术对比2025-01-23 2731

全部0条评论

快来发表一下你的评论吧 !