复杂电路系统电源及PDS设计

电源设计应用

描述

现代大型集成电路,比如CPU、大型FPGA等消耗的电流往往达到数安到几十A,并且一些复杂系统电源种类繁多,因此电源系统的设计是否合理往往成为系统能否稳定工作的关键。电源系统的设计应该包含电源评估、电源供电电路设计和功率分布系统(Power distribution system 简称PDS)三个方面。本文分别探讨这三个方面的一般设计方法和思路。

一、电源评估

评估电源是电源系统设计的第一步,也是最重要的一步,决定了电源设计的成败。在设计电源的时候应该已经完成了整个系统的框图设计并基本选定了其中重要的IC芯片,这时我们需要参考数据手册Datasheet获得每一个IC的工作电压及消耗电流,并绘制下面这样一张表:

表一、 IC电源评估表

1. 电源类型

电源类型可以分为模拟和数字两大类,模拟电源是指为PLL、ADC/DAC等模拟电路供电的电源;而数字电源主要是为数字电路供电,它又可以分为核心电源(主要为集成电路的核心逻辑电路供电,比如FPGA 核心电、压源)和I/O电源(主要为I/O接口供电),现代大型IC的供电一般核心电压和I/O电源是分开供电。

2. 电压值

电压值一般包含最小、典型和最大值,一般设计的电路电源应该工作在典型工作电压上,并且电源波动范围不应该超过最小和最大值的范围。

3. 电流

在设计电源时电流值应该考虑最Worst的情况,比如大型FPGA系统电流可能会随着使用逻辑门的多少而相差很多;在设计供电电路时在评估的最大电流基础上要提供一定的设计余量。

4. 功耗

统计每个电源的功耗是为了更合理的分布电源Tree,参考电源树一节。

在获取每个IC的电源参数后,我们需要绘制下面这样一张统计表,这一步是为了电源电路的设计和规划电源Tree做准备。

二、电源电路设计

1. 模拟电源

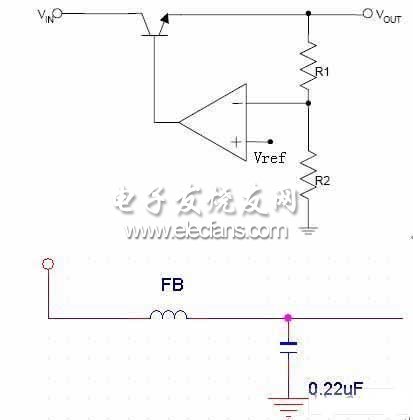

模拟电源往往为PLL、ADC/DAC、电流源等等模拟电路供电,它们的特点是电流较小,一般在几十mA到几百mA之间,并且对电源纹波敏感。因此模拟电源电路的设计往往选择LDO等,我们称为线性电源;并且对电源在IC引脚输入处要采取LC或铁氧体进行滤波以进一步减小电源纹波。其典型原理如图1所示:

图1

2. 数字电源

数字电源一般为逻辑电路供电,它们要求往往电压较小,但是电流很大。比如现代X86 CPU的核心电源一般在1V左右,但是供电电流可以达到几十安。并且由于CPU内部的省电状态的切换,电流的变化也很大(最省电和全速状态工作电流可能相差几十倍)。

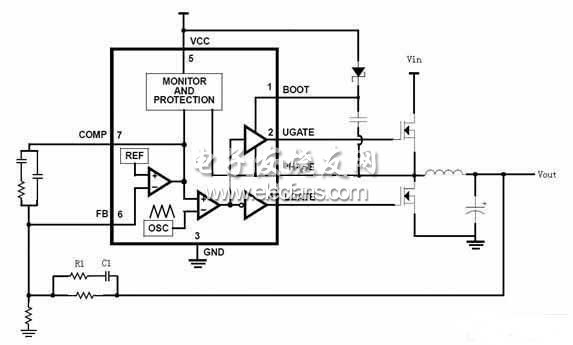

这类电源的设计一般选用数字调制的开关电源,这类电源一般由一个PWM控制器和外部输出MOS管、BOOT电路、反馈网络、LC滤波电路组成;另外也有些可以提供较大电流的LDO电源可以选用。对于超大电流供电时还需要考虑使用多项供电。下图是一个单相PWM供电电路的原理图:

图2

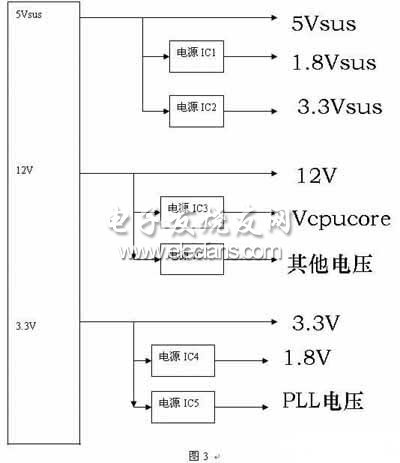

3. 电源Tree的绘制

在选择好电源的供电芯片后可以开始电源Tree的绘制,我们以典型的主板供电电路为例介绍。首先主板采用的外部供电电源来自一个350W电源,它分为12V、5V、5Vsus和3.3V输入,而主板上使用的电源有12V、5V(待机电压5Vsus)、3.3V(待机电压3.3Vsus)、CPU核心电压Vcore_cpu、CPU的PLL模拟电源、前端总线电源、内存1.8V电源(待机电压1.8Vsus)等等。其实一个主板上还有更多其他的电源,比如芯片组电源等等。我们需要合理的分配每路电源,保证每条电源路径末端的总功率不要超过前端电源的供电能力。最终我们应该绘制出一幅类似如图3所示的电源Tree(仅为示意图):

图3

当然,对于一个简单的系统设计起电源可能没有这么复杂。

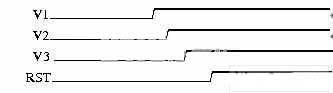

4. 电源上电时序

对于较为复杂的系统,在绘制完电源Tree的基础上我们应该根据电源的上电顺序和系统复位等信号的要求绘制出具体而明确的上电时序图,如图4所示。并根据该上电时序图指导电源设计时电源IC的上电先后顺序。

图4

三、 PDS系统设计

PDS系统的设计最重要的部分就是退耦和旁路电容选择和分布,很多人认为旁路和退耦的作用是一样的,而实际上是不同的。

1. 退耦和旁路电容工作原理

1) 旁路的模型如图

当IC内部出现高频的电流波动,比如I/O或门的开关,这些高频的瞬态电流变化如果从电源吸取电流会引起电流的高频波动,而电流源的内阻和电源走线在高频时呈感性阻抗L,频率越高阻抗越大,从而引起IC电源引脚处较大的压降。因此在靠近IC电源引脚放置电容Cbp为IC提供瞬态电流,在瞬态电流变化时IC引脚会从低阻抗的电容C上吸取电流(理论上电流可以从电源线和电容两条途径流动,但是电容阻抗低,所以电流会主要沿着电容流动)。电容电压下降后会从电源线上补充电荷。本质上旁路电容的作用减少电源线上的瞬态(高频)电流波动。 旁路电容为高频充放电提供电荷,因此它的ESR和ESL(包含到电源引脚引线电感)应该尽量低,尽量靠近电源引脚,常用的旁路电容是小容量的(0.1uF、0.01uF等)陶瓷电容。

2) 退耦的模型如图

电路IC1上不可避免的会在电源线上产生一些噪声或者电流波动(主要是较低频段,因为高频的电流波动可以被它的旁路电容消除),如果一个电源同时为多个IC模块供电,其中一个IC上的噪声就会传递到另外一个IC电路。为了减少模块之间的噪声耦合放置电容Cdec,它和电源线上的电感组成一个LC低通滤波电路,当噪声(来自另外一个电路模块,或者来自电源本身,比如开关电源本身输出电压就含有大量噪声)沿着电源线传递到某一个IC时就会被这个LC低通滤波器消除。本质上退耦电容的作用是避免电源噪声从一个电路模块传递到另外一个模块。退耦电容要滤除电源线上的较低频的噪声,因此LC低通滤波的截止频率要低一些,同时Cdec电容还有为后续电路(包含很多旁路电容)提供电荷、稳定电压的作用,因此电容Cdec容量较大,常采用大容量(几十到几百uF)的坦电容。

2. 退耦和旁路电容的大小及位置

退耦和旁路的最终目的是要在IC的电源引脚处产生稳定的电压,它们都要求尽量靠近IC的电源引脚,在实际的系统中有时并不需要刻意区分退耦电容和旁路电容,而统称为退耦电容。

1) 小容量陶瓷电容(一般0.01uF~0.22uF)作为旁路电容,它的放置原则是尽量减小ESL,一般采用0402封装,应该放置在最靠近电源引脚的地方。现在大量的高密度集成电路采用的都是BGA的封装,它的所有引脚都在Chip下部,通过引脚ball和PCB版的Top层焊盘相连,电源总线或平面一般通过Via过孔延伸到芯片封装下部的电源引脚。所以最靠近电源引脚的位置就是芯片封装的下部PCB的背面,电容的PAD最好和过孔via直接相连。有些芯片也会直接在封装体substrate上焊有电容,这样就可以减少在PCB板上的旁路电容数量。

2) 大容量的退耦电容(一般>33uF),一般封装比较大,不可能特别靠近芯片的引脚,不过这类电容用于滤除较低频率的噪声,对放置的位置不是特别敏感,所以最合适的位置可能在芯片的边缘靠近芯片的位置。

3) 有时也会在退耦Cdec和旁路电容Cbp中间放置一些容量在几个uF(2.2uF等)的陶瓷电容作为中间级,一般认为它们是用来滤除一些中间频率的噪声,并为附近的旁路电容提供电荷,这些电容一般采用0805的封装,也应该尽量靠近电源的引脚处。

在选择具体的电容时还要考虑到其ESR的大小、噪声的频率高低等因素,并确定电容的数量,有时还需要通过适当的仿真simulation来帮助设计。

3. PDS分布设计实例

例子1

BGA封装芯片的电源引脚集中在芯片的中心附近,电源通过类似bus的方式连接到芯片的中心区,可能的电容布局如图,上下两边为0.1uF和0.01uF的小电容,中心为2.2uF的陶瓷电容,坦电容放置在芯片边缘,具体的布局和过孔的位置需要根据电源引脚的分布具体的调整,原则上应该是一大一(或几)小进行配对。

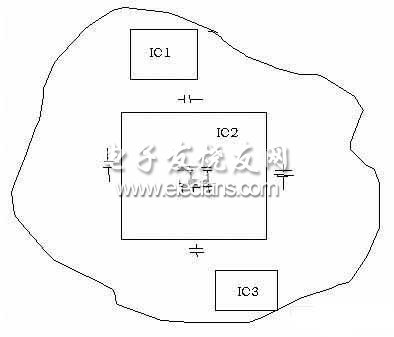

例子2

采用电源平面的方式,退耦电容放置在芯片边缘处靠近IC2的地方,IC1/IC3为其他使用该电源的芯片,IC2中心为小电容和中等容量陶瓷电容。

-

电子电路系统及标准最佳设计2011-07-28 770

-

电源传输系统PDS是如何引起的?如何缓解?2023-07-05 4486

-

警示灯光耦合器电路系统设计教程2016-01-29 2475

-

关于电路系统设计问题的解答2021-03-11 1721

-

如何去设计一种控制接口切换电路系统?2021-05-13 1052

-

如何对电子电路系统进行调测2021-08-06 2676

-

TOP2语音识别机器人系统电路系统电源电路设计2021-12-21 1055

-

超低功耗电子电路系统设计原则2008-10-28 741

-

什么是综合布线系统(PDS)2010-06-09 11470

-

PCB的输电系统(PDS)设计2012-06-13 2100

-

电路系统中的噪声问题研究2016-12-16 1013

-

用于相位法激光测距的电路系统设计2017-06-14 3839

-

PCB的PDS的设计目标2017-09-26 1161

-

哪些属于专用集成电路系统2024-04-14 1357

-

pds系统功能介绍 pds软件的优缺点分析2024-12-05 7784

全部0条评论

快来发表一下你的评论吧 !