源极接地放大电路参数讲解(1)

模拟技术

描述

三 放大电路参数

3.1 输入阻抗

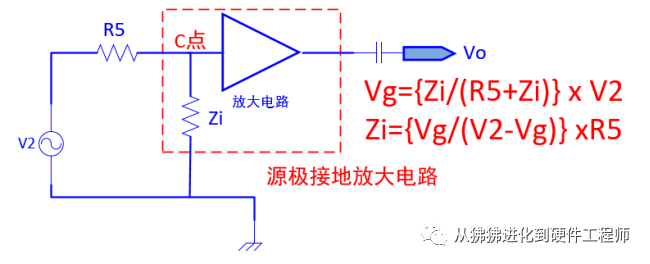

仿真或者测量输入阻抗,需要在信号输入端串联一个电阻,如下图R5。

对交流信号而言,栅极电压Vg(c点)就是R5和源极接地放大电路的输入阻抗Zi分压得到的。

当Vg电压是V2电压的一半时,R5=Zi。

取R5=12.2K,仿真得到V2(a点)和Vg(c点)的电压波形如下。V2正好是Vg的一半,即此放大电路的输入阻抗是12.2KΩ。换个角度看,其实它就是R1和R2的并联阻抗,理论计算R1和R2的并联阻抗(R1*R2)/(R1+R2)=12.4KΩ。仿真和理论计算差不多。另外,R5也会影响Vo的输出幅度。随着R5的增大,Vg被分配到的电压越来越小,经过放大后的Vo也会相应减小。

FET本身的输入阻抗非常高,因为FET没有栅极电流,所以FET的输入阻抗无群大。不过在实际电路中受R1和R2组成的偏置电路影响,电路整体的输入阻抗变低。

还有一个办法可以说明FET的输入阻抗非常大。如下图,在偏置电路和FET的栅极之间串联一个电阻R6,分别将其赋值为0Ω和1MΩ。仿真后观察结果,两种阻值下,输出电源Vo(b点)是一样的。这说明FET的输入阻抗是一个比1MΩ还大的值。否则,R6和FET输入阻抗分压之后,大多数电压会被落在R6上,栅极输入信号的振幅会降低,进而导致Vo的振幅降低。

此结论不适用于BJT,因为它存在基极电流。

3.2 输出阻抗

此类放大电路的输出阻抗仿真或者测量方法是:先测量输出开路时的输出电压Vo1。而后在Vo端加一颗负载RL,测试有负载时的输出电压Vo2。Vo2是此放大电路的输出阻抗Zo和负载RL对Vo1的分压值。

例如,之前的文章做过仿真,此放大电路开路时的输出电压Vo1=3V。现在在输出端放置一个负载RL(下图R7),取值为65KΩ。仿真结果是Vo2=1.5V。正好Vo2是Vo1的一半,说明Zo=RL,分压一半。

换个角度看,FET是一种电压控制电流的可变电流源。可以认为输出阻抗就是可变电流源内阻和漏极电阻(R3)并联的阻值。从交流信号角度看,VDD和GND是一致的。又因为电流源的阻抗是无穷大的,因此从输出端看的输出阻抗就是漏极电阻R3。这也和上面的仿真结果吻合。

未完待续

-

源极跟随器电路设计2023-08-31 3833

-

源极接地放大电路应用讲解2023-07-15 2708

-

源极接地放大电路设计(1)2023-06-23 855

-

共源极放大器电路及原理2009-12-08 20953

-

采用N沟MOSFET的源极接地型开关电路图2009-08-15 3116

-

导致源极接地电路高频特性降低的因素电路图2009-08-08 585

全部0条评论

快来发表一下你的评论吧 !