DC-DC的Layout要点(3)

描述

DC-DC-25---DC-DC的Layout要点

引言:DC-DC的布局布线少不了要使用过孔和铜皮,过孔和铜皮的相关寄生参数对于功率布局走线需要格外注意,本节简述过孔铜箔的相关参数估算以及使用注意点。

1.铜箔的阻抗

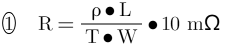

图25-1表示单位面积铜箔的阻抗值。通常为厚35um、宽1mm、长1mm铜箔面积的阻抗值。通常可利用下列公式进行阻抗计算:

l ∶ 导线的长度 [mm]

w ∶ 导线的宽度 [mm]

t ∶ 铜箔的厚度 [um]

p ∶ 铜的电阻率 [uΩcm]

T ∶ 温度

根据从图25-1读取到的每单位面积的阻抗值RP来计算,结果如下:

RP ∶ 从曲线中读取的阻抗值 [mΩ]

l ∶ 导线的长度 [mm]

w ∶ 导线的宽度 [mm]

t ∶ 铜箔的厚度 [um]

比如25°C时,宽3mm、长50mm的铜箔的阻抗值,可以根据下列计算得出是8.17mΩ。

根据该阻抗值,流过3A电流时的压降为24.5mV,当温度上升至100℃时,阻抗值增加29%,压降也增加至31.6mV。

图25-1:单位面积铜箔的阻抗值

2.铜箔的感抗

铜箔的感抗可以用以下公式表示。从公式可以看出,PCB布线的感抗值几乎不依赖于铜箔的厚度。

l ∶ 导线的长度 [mm]

w ∶ 导线的宽度 [mm]

t ∶ 铜箔的厚度 [um]

图25-2表示的是铜箔感抗的计算值。从图表可以看出,即使线宽增加2倍,电感值也不会降低到理想状态。想要抑制寄生电感的影响,缩短布线长度是最好的解决办法。假设电感值L[H]在电路板布线上的流过的电流在时间t[s]之内的变化量为i[A],则将在其电路板布线的两端产生以下电压。

例如在寄生电感值为6nH的电路板布线上,在10ns内流过了2A的电流时,将产生以下电压:

图25-2:铜箔的感抗

3.过孔的阻抗

过孔的阻抗值用以下公式表示。图25-3表示的是板厚1.6mm、镀层厚0.015mm (15um) 条件下过孔的阻抗值。

h ∶ 板厚 [mm]

d ∶ 过孔直径 [mm]

tm∶通孔镀层厚度[mm]

p ∶铜的电阻率[uΩcm]

T ∶ 温度

图25-3:过孔的阻抗

4.过孔的感抗

根据Howard W. Johnson的方法,过孔的感抗值按以下公式表示。图25-4显示了计算结果。

h∶ 板厚[mm]

d ∶ 过孔直径[mm]

感抗值虽然很小,但布线呈直角时会导致EMI恶化。

图25-4:过孔的感抗

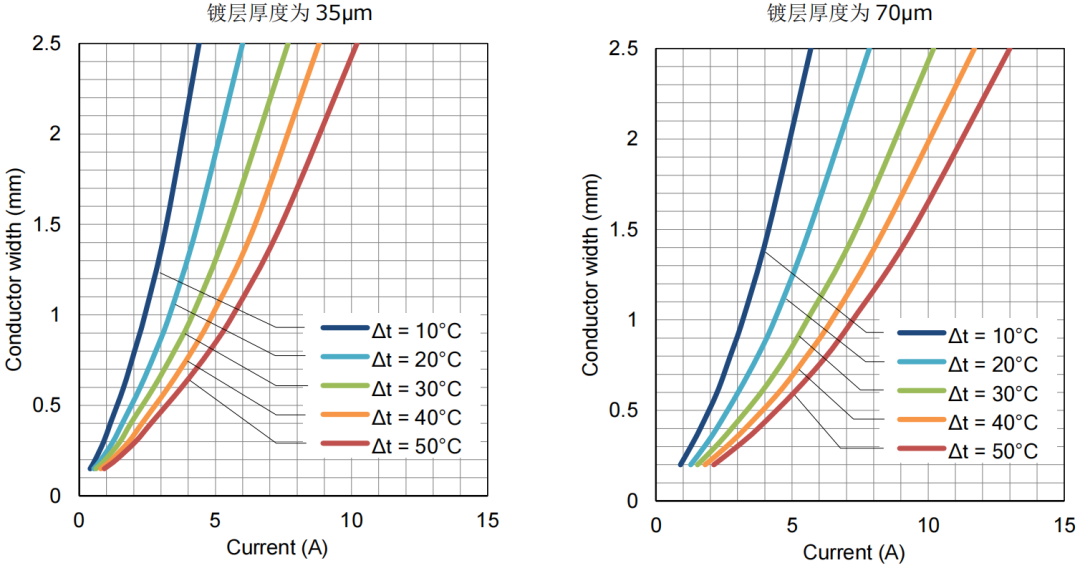

5.过孔的容许电流

过孔的直径乘以π后的值相当于线宽,可以根据图25-5中导体的电流导致的温度上升图表推测出过孔的容许电流值,但是由于过孔的镀层厚度只有18um,容许电流能力要低于图表所示镀层厚度为35um的导线。

图25-5:镀层厚度、导线宽度、电流导致的温升

在前述布线项中,曾建议在镀层厚度为35um时,按照1A电流使用1mm以上宽度的导体进行布线,但是因为过孔的镀层厚度只有一半,所以建议按照1A电流使用2mm以上宽度的导体进行布线。图25-6是容许电流的示例,请根据使用用途配置过孔的个数,确保容许电流、阻抗、感抗满足规格要求。

图25-6:容许电流

6. 拐角布线

如果将拐角布线折为直角,阻抗将在拐角处发生变化,这会导致电流波形紊乱,产生被称为“反射”的波形畸变。开关节点等频率较高的布线EMI可能会恶化。如图25-7所示,尽量将拐角处做45°折线或者圆弧弯曲状处理,弯曲的半径越大,阻抗的变化越小。

图25-7:拐角布线

-

DC-DC的Layout要点(2)2023-07-15 6688

-

DC-DC工作原理2012-08-29 12722

-

DC-DC锂电FAE-深圳2014-03-14 2141

-

DC-DC的layout有哪些原则2021-11-16 2122

-

推荐一个DC-DC电路设计工具2023-03-17 7448

-

减小DC-DC变换器中的接地反弹的接地要点2016-12-17 803

-

DC-DC中PCB设计的layout2021-09-13 8483

-

DC-DC PCB layout 指导2021-11-09 1073

-

DC-DC PCB layout指导说明2022-05-12 1243

-

DC-DC的PCB设计2022-09-06 1827

-

了解一下DC-DC的layout2023-02-12 3048

-

DC-DC转换器PCB设计的一些要点2023-10-23 1942

-

如何设计好DC-DC电源,以下几点值得注意2023-11-30 1859

-

5条DC-DC PCB layout建议2024-01-16 1986

-

DC-DC的PCB设计注意的点2024-01-17 1318

全部0条评论

快来发表一下你的评论吧 !