电源之LDO-2. LDO的压降

电源之LDO-2. LDO的压降

电子说

描述

关注个人公众号阅读其他文章:硬件之路学习笔记

也可以点击直接跳转下列文章:

电源之LDO——1.LDO基础知识

电源之LDO-2. LDO的压降

电源之LDO-3. LDO的热性能

电源之LDO-4. LDO的电源抑制比

电源之LDO-5. LDO的噪声

电源之LDO-6. LDO的输出电容

1. 什么是压降?

压降电压 Vdrop 是指为实现正常稳压,输入电压 VIN 必须高出所需输出电压 VOUT的最小压差。

2. 压降在数据手册中如何体现?

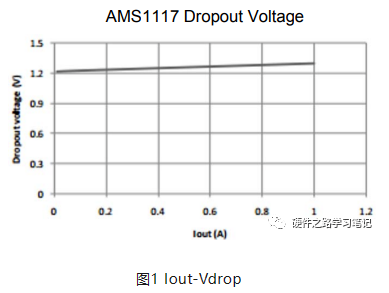

以经典LDO AMS1117-3.3为例,在数据手册中其Vdrop电压在0.8A时为1.1V,意味着想要输获得3.3V-0.8A的功率输出,在不考虑温度等其他影响条件下,VIN至少要等于3.3+1.1=4.4V。 部分手册还会给出具体的输出电流-Vdrop曲线,如下图1

3. 决定压降的因素是什么?

输出电流是Vdrop的一大影响因素,但其决定因素是LDO 的架构。为说明原因,我们分别介绍PMOS结构LDO与NMOS型LDO,并对比其工作情况。

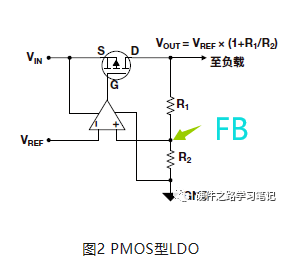

PMOS型号LDO稳压输出原理:当Vout小于Vref+(1+R1/R2),即FB小于Vref,运放VP小于VN,运放输出电压Vg减小,Vin不变,即Vs不变,则|Vgs|=|Vg-Vs|增大,所以MOS的Vds减小,Vout=VIN-Vds增大,产生了负反馈;反过来同理。 因为运放输出电压最低是0V,所以VGS最大值为VIN-0=VIN,即Vds有限小,Vdrop就等于Vds,这就是PMOS的Vdrop有限小的原因。同时,当输出电流增大时,Vgs也需等大,依旧是同样的原因,输出电流也有限大。为什么数据手册上给的Vdrop要限制输出电流为0.8A?正是由于输出电流和Vdrop都受运放最小输出电压限制。 同时由于VGS的最大值等于VIN,所以PMOS型LDO在大电压输入的场合更能获得低的Vdrop。

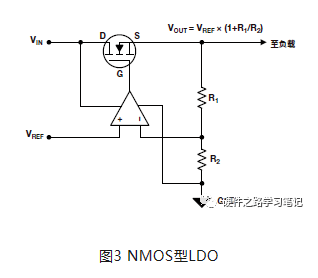

与PMOS相似的负反馈,不再赘述,不同的是,NMOS型的Vgs因为Vg受运放最大输出电压Vg的影响有限大,所以Vdrop=Vds有限小。

4. 如何降低压降

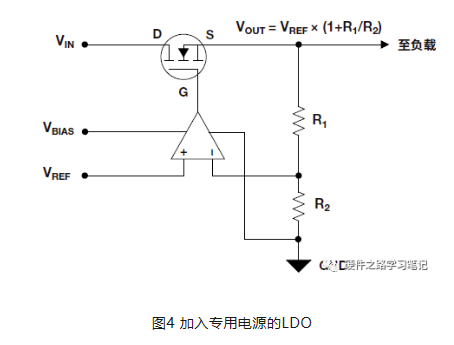

了解了NMOS和PMOS型LDO的控制逻辑后我们可以轻易得出降低Vdrop的方法-增大|Vgs|,由于Vs我们无法控制,因此我们可以通过增大Vg来增大Vgs,一般有以下两种方法。

①. 为运放增加专用的辅助电源,此电源大于输入电压。

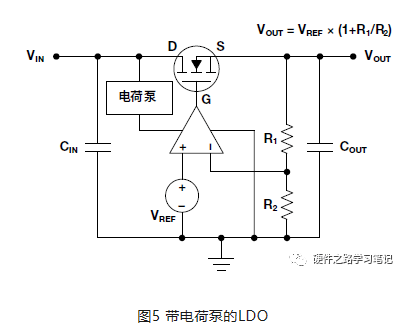

②. 更简单的方法是加入电荷泵提高运放供电电压。

审核编辑:汤梓红

-

LDO器件如何选择?如何计算温升?LDO压降高发热大怎么破?2023-10-30 4692

-

决定低压降稳压器LDO压降的因素介绍2023-09-22 3352

-

线性电源LDO基础知识(一):压降Dropout Voltage2023-05-06 4148

-

一文弄懂LDO2021-12-03 2230

-

电源芯片设计选择DC/DC还是LDO2021-11-17 1596

-

DC/DC和LDO的区别2021-11-09 787

-

电源芯片选择DC-DC还是LDO看了就知道2020-12-09 3111

-

如何测量LDO标准压降和极低压降之间的差异2020-11-23 5148

-

浅析LDO2019-05-29 2659

-

电源芯片选择什么好?什么是 LDO(低压降)稳压器?2018-06-25 27865

-

LDO和DC/DC电源的区别之谈(摘选)2017-03-03 4900

-

LDO低压差线性稳压器2012-12-25 4237

-

MITSUMI超低饱和压降NMOS LDO稳压器MM35012010-12-07 1659

全部0条评论

快来发表一下你的评论吧 !