什么是同步有限状态机?为什么要用状态机?怎么表示状态机?

电子说

1.4w人已加入

描述

什么是同步有限状态机?

同步:所有的状态跳转都是在时钟的作用下进行

有限:状态的个数是有限的

为什么要用状态机?

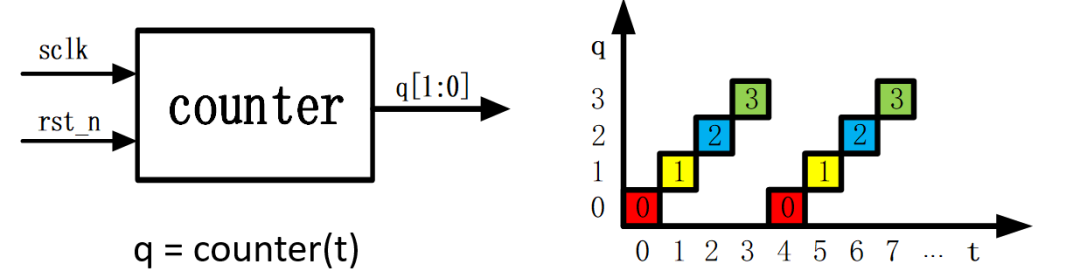

FPGA是并行处理的,如果我们想要处理具有前后顺序的事件时,就需要引入状态机。状态机的每一个状态代表一个事件,从执行当前事件到执行另一事件我们称之为状态的跳转或状态的转移。

状态机特别适合描述那些发生有先后顺序或时序规律的事情。小到计数器大到微处理器都适合用状态机描述。

怎么表示状态机?

状态机需要具备什么?

- 输入:根据输入确定是否需要进行状态跳转

- 输出:当前时刻状态要做的事情是什么

- 状态:要处理的事情

状态机的设计步骤是怎么样的?

- 首先分析输入、输出有哪些,需要多少个状态

- 其次根据分析绘制状态转移图

- 设计实现的模块

- 状态机代码的编写

FIFO的使用

什么是FIFO?

FIFO(First In First Out)即先入先出,是一种数据缓冲器,用来实现数据先入先出的读/写方式。FIFO有一个写端口和一个读端口外部无需使用者控制地址,使用方便。

根据FIFO工作的时钟域可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。异步FIFO是指读/写时钟不一致,是相互独立的。

FIFO的作用是什么?

- 用于缓存数据

- 用于做多bit数据的跨时钟域处理

- 用于做时钟、位宽不匹配问题的接口

如何使用FIFO?

- 在一定时间内,写数据的总带宽一定要小于等于读数据的总带宽

- 控制好FIFO的关键信号,读写时钟、读写使能、空满标志信号

- FIFO一定不能写满、也不能读空,要考虑FIFO的背靠背问题,设置好存储深度

FPGA设计中的技巧

一、使能信号(en)、标志信号(flag)、计数器(cnt)

二、模块框图设计——方案的确定

三、波形设计——代码的实现

四、代码规范——可复用性和效率

五、仿真调试——修改查错

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog状态机+设计实例2024-02-12 6343

-

SaberRD状态机建模工具介绍(一)什么是状态机建模2023-12-05 3228

-

什么是状态机?状态机的种类与实现2023-10-19 13142

-

有限状态机分割设计2023-10-09 1338

-

Verilog状态机的类型2023-06-01 2993

-

如何以面向对象的思想设计有限状态机2022-02-07 720

-

什么是有限状态机呢2021-12-20 1498

-

基于事件驱动的有限状态机介绍2021-11-16 3104

-

如何使用FPGA实现序列检测有限状态机2020-11-04 1320

-

有限状态机有什么类型?2020-04-06 4252

-

初学者对有限状态机(FSM)的设计的认识2017-02-11 4774

-

VHDL有限状态机设计-ST2016-06-08 1005

-

有限状态机的建模与优化设计2016-03-22 825

全部0条评论

快来发表一下你的评论吧 !