采样保持电路之开关寄生的影响

描述

“采样保持电路是模数转换器(ADC)中最重要的电路之一。其电路中存在的寄生电容会引入时钟馈通、沟道电荷注入等非理想因素严重影响ADC的整体性能。鉴于此,本文将介绍这些非理想因素产生的原因及常见的解决方法”

01采样保持电路

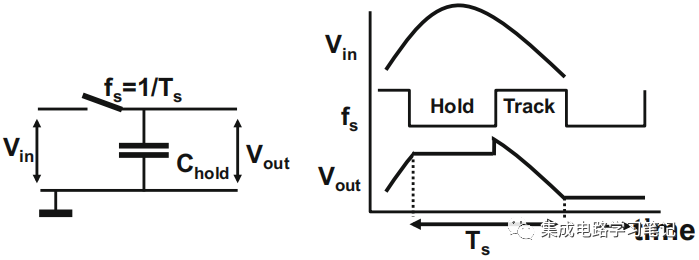

采样保持电路通常被用在模数转换器设计中,起到信号采集的作用。图1是一个由开关和电容组成的采样保持电路。在采样阶段,开关闭合且电容Chold采集输入信号的信息。在保持阶段,开关断开Chold保存采样时刻输入信号的信息,从而实现信号的采样和保持的功能。

图1 采样保持电路[1]

02开关寄生对采样精度的影响

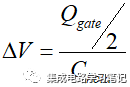

图1所示的采样保持电路中的开关可由一个简单的MOS管实现。当开关导通时,沟道内存在电荷会积累电荷Qgate。开关断开后,这些电荷会流出到采样电容上从而引起采样误差。这就是 “电荷注入” 。由电荷注入产生的误差可表示为

其中,1/2是假设沟道中的一半电荷流入到采样电容上。

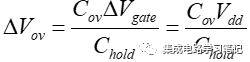

此外,时钟馈通效应也是引起采样误差的一个重要来源。MOS管的栅漏或栅源之间存在交叠电容Cov。采样结束时钟跳变时,会通过交叠电容馈通到采样电容上,从而引起采样误差。由时钟馈通而导致的误差可表示为

可见时钟馈通引入的是一个与输入信号无关的失调电压。

03解决时钟馈通和电荷注入的几种方法

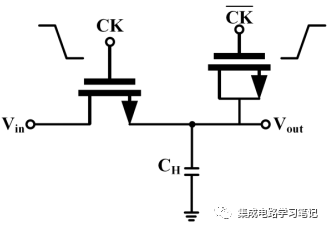

1. 增加虚拟开关

如图2所示,相比于图1增加了一个额外的虚拟开关。虚拟开关的状态与采样开关的状态相反,且大小为采样开关的二分之一。当采样开关关断时,沟道电荷Qgate的一半流向输出端一侧,此时虚拟开关开启并吸收采样开关释放的多余电荷。从而达到采样电容上的输入信号不被影响的目的。

该方法虽然简单但也存在一定的问题。采样开关不可能刚好向输出一侧注入一半的电荷。因此不能完全抑制电荷注入所引起的误差。

图2 增加虚拟开关

2. 底板采样

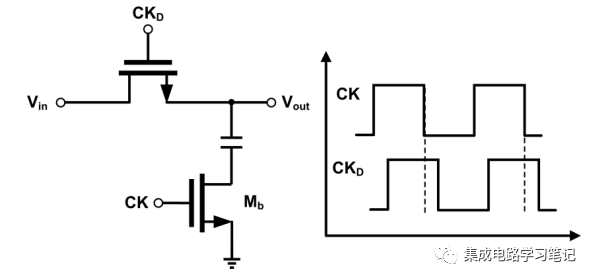

图3为底板采样技术的示意图。当采样结束时,晶体管Mb首先断开,此时采样电容下极板浮空,随后另一个晶体管再关断。因为采样电容下极板浮空处于高阻状态,晶体管内电荷不会流入采样电容上,从而避免电荷注入而引起的采样误差。值得一提的是,该结构无法解决时钟馈通的问题。

图3 底板采样方法

3. 差分采样

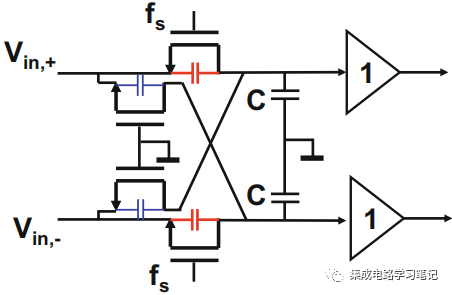

在模拟集成电路设计中,差分是一种常见的消除偶次非线性的方法。如图4所示,实际采样电路中,不仅有时钟馈通和沟道电荷注入等非理想因素,输入信号通过MOS管的漏源寄生电容Cds(红色标识)也会馈通到输出端。通过增加两个常关断的MOS开关大小与采样开关一致,并结合差分结构可以有效的减小输入信号馈通的影响。

该差分结构相较于底板采样等方法具有采样精度高的优点,但这是以增加功耗和面积换来的。

图4 差分采样结构

-

采样保持电路图(五款采样保持电路设计原理图详解)2018-02-23 107105

-

采样保持电路设计及其工作原理2022-10-20 8868

-

深度剖析采样保持电路2022-11-08 11239

-

转:采样保持电路2011-07-28 4867

-

简易的AD转换器的采样保持电路的模拟开关如何实际2023-10-25 3425

-

对采样保持电路的分析2010-04-13 834

-

一种新型高速采样保持电路2010-05-24 1078

-

采样保持电路2009-01-02 1877

-

采样与保持电路图2009-04-09 2154

-

采样保持电路原理(S/H)2009-04-12 26684

-

采样保持电路图2009-07-08 1198

-

采样时间为20US的中速采样和保持电路2010-05-05 2017

-

单片采样保持电路2010-05-23 3660

-

峰值电压采样保持电路2020-01-21 18286

-

ADG1211开关实现采样保持电路2023-03-17 3579

全部0条评论

快来发表一下你的评论吧 !