HSP50415在数字上变频应用研究

处理器/DSP

描述

介绍了Intersil公司推出的可编程数字上变频器HSP50415的结构、功能和特点,给出了HSP50415在数字上变频应用中与TMS320VC5509的接口电路。

1 引言

软件无线电的基本思想是在一个通用的硬件平台上,通过软件加载的方式用软件实现所有无线电台的功能。软件无线电的理想结构是将A/D、D/A尽可能地靠近天线。考虑到目前A/D、D/A的带宽及DSP的处理能力,一般采用中频采样的软件无线电结构。

2 HSP50415的功能和特点

2.1 HSP50415的内部结构和功能

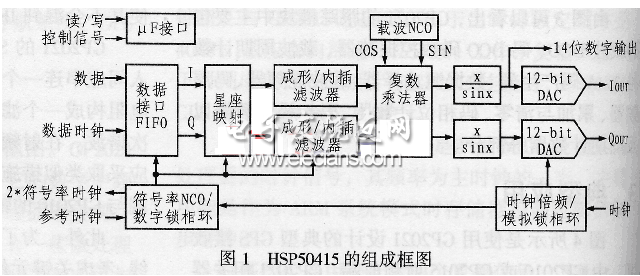

HSP50415由256深度的FIFO数据缓冲器、星座映射器、成形和内插滤波器、复数乘法器、符号率NCO、载波NCO及双路DAC组成。其内部组成如图1所示。各组成部分的功能如下:

前端数据输入模块:HSP50415的信号输入管脚是DIN(0~15)、ISTRB、TXEN和DATACLK。数据输入有两种方式:一种是固定符号速率传输方式,一种是猝发传输方式。在固定符号速率传输方式下,数据将以2倍采样率进入数据缓冲区,缓冲区为256×32bit的FIFO。一旦一对I和Q数据进入FIFO,数据会以采样率读出。因为FIFO完成了一个串并变换,将一路信号变换成I和Q两路信号,因此输入端数据率是输出端的2倍。在猝发方式下,当数据满或半满时,FIFO的标志位可触发DSP的中断,通知DSP停止发数据,这时可读数据。I/O输入时序如图2所示。

星座映射图:星座映射图中有一个用户可编程查找表(256×8bit RAM),这个查找表仅支持I/Q最大位宽为4bit(256QAM)的数据,可完成各种正交的PM和AM基带码映射。I和Q数据合并成8bit的数据作为地址去查表,得到映射数据并以Iout<3:0>和Qout<3:0>的形式输出,如图3所示。

成形滤波器:成形滤波器的基本内插率为×4、×8或×16。此外,还有一个可选的2bit模式以供用户将抽样率减少1/2。成形滤波器的运算由移位累加来完成,其最大输入采样率为MIN((CLK×2×2^twoBitMode)/(#bit×interpolationRate),CLK/4)。若使用2bit模式,则式中twoBitMode为1,否则为0,#bit为输入数据的位数,interpolationRate为内插率。

半带滤波器:半带滤波器的内插率为2,由于其系数在偶数点上为零,因此可将计算量减少一倍。

内插滤波器:内插滤波器将半带滤波器的输出采样率插值到最终的采样率Fsout。

数控振荡器(NCO):为内插滤波器提供时钟,并允许输入和输出采样率有非整数倍关系。

乘法器:把基带信号调制到可编程中频上。

输出模块:HSP50415内部集成了双路12位DAC,并由x/sinx滤波器提供滚降补偿,可以实现模拟输出。另外还提供了14位数字输出。

2.2 HSP50415的特点

HSP50415是一个功能强大的可编程调制器,编程十分灵活,信号的极性可以通过编程来改变,内部集成了高速D/A转换器,性价比较高。HSP50415具有功耗低、 精度高、可靠性强等优点,其主要性能参数如下:

●最高输出采样率达100MHz?最高输入数据率达25MHz。

●编程载波NCO和符号NCO均为32位,精度高。

●x/sinx滚降补偿。

●每路有四片64×72位的FIR滤波器,其系数RAM可由Intersil公司提供的软件来产生。

●成形滤波器的内插率可编程设置,达24个符号间隔,半带滤波器和内插滤波器的系数是固定的。

●数字信号处理能力大于70dB(SFDR)。

●14位数字输出或双路12位D/A模拟输出,D/A处理能力大于50dB。微处理器端口有18个控制寄存器,可方便地控制256×32位FIFO及其深度、成形滤波器的阶数、增益调整、符号速率、载波频率及是否旁路某些模块等。

2.3 HSP50415的主要管脚功能:

CLK: 系统时钟

SYSCLK/2: 系统内部时钟

DIN<15:0>: 数据总线

CDATA<7:0>: 微处理器数据总线

RD: 微处理器读

WR: 微处理器写

ADDR<2:0>: 微处理器地址总线

Iout<13:0>,Qout<13:0>: 数字输出

IOUTA,IOUTB,QOUTA,QOUTB: 模拟输出

2*SYMCLK: 采样时钟的2倍

REFCLK: 参考时钟

DATACLK: 异步数据时钟

TXEN: 猝发模式选通信号

ISTRB: 路数据选通信号

INTREQ: 中断请求信号

FEMPT,FOVER,FFULL: FIFO电平监控信号

LOCKDET: 数字锁相环的状态标志

ICOMP,QCOMP: 为减小串音提供的补偿信号

REFLO: 内部参考选择

REFIO: 外部参考电压输入

FSADJ: 满量程电流调整

2.4 HSP50415的初始化及参数设置

HSP50415的初始化包括两部分,一是对控制寄存器的初始化,二是对成形滤波器系数RAM及星座映射器RAM的初始化。HSP50415总共有18个寄存器,通过对这些控制寄存器的访问,可以方便地控制256×32位FIFO及其深度、成形滤波器的阶数、增益调整、符号速率、载波频率以及是否旁路某些模块等,从而便于进行硬件调试。系数和控制字的值可以使用Intersil公司网站提供的可执行文件sim415.exe和modulator.exe方便地产生。图4表示将值为AABBCCDD的控制字送入地址为0C的控制寄存器的时序。

HSP50415的参数可由下面的公式确定:

符号率NCO=(symbolrate/Fsout)×232

载波NCO=(carrierFrequency/Fsout)×232

3 HSP50415的调制原理及实现

HSP50415的复数乘法器可完成如下运算:

S(n)=I(n)cos(ω0ts)-Q(n) sin(ω0ts)?

其中,S(n)为输出信号,ω0为载波频率,ts为取样间隔。根据I(n)和Q(n)编码方式的不同,可以完成BPSK、QPSK、m-QAM等调制方式。如令Q(n)=0,则:

S(n)=I(n)cos(ω0ts)

此时即可得到DSB调制信号。

4 用HSP50415实现数字上变频

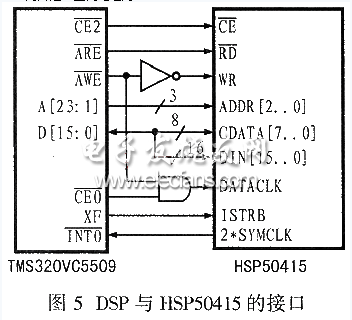

HSP50415编程灵活,可应用于无线电台的发射系统中。图5为HSP50415与TMS320VC5509的接口电路,可用来实现数字上变频技术。

图中采用了两个片选信号,用于区分微处理器端口和数据端口。初始化时CE2选通,DSP通过微处理器接口访问HSP50415。初始化完成后CE0选通,DSP每收到一个中断,便通过DATA/FIFO接口向HSP50415发一个数据。XF连接ISTRB以表明这个数据是I数据还是Q数据。CE0与AWE相或产生DATACLK信号。中断信号由2*SYMCLK产生。

5 典型程序代码

5.1 一个32位寄存器初始化代码

amov #BUFF0,xar0 ;BUFF0定义为片选2空间的地址0x400000

mov #0xDD, *ar0

amov #BUFF1, xar0 ;BUFF1定义为片选2空间的地址0x400001

mov #0xCC, *ar0

amov #BUFF2, xar0 ;BUFF2定义为片选2空间的地址0x400002

mov #0xBB, *ar0

amov #BUFF3, xar0 ;BUFF3定义为片选2空间的地址0x400003

mov #0xAA, *ar0

amov #BUFF4,xar0 ;BUFF4定义为片选2空间的地址0x400004

mov #0x0C, *ar0

5.2 简单的发送程序(以正弦波为例)

mov #63, ac0 ;设发射通常为64,循环发送

amov real_data, xar1 ;xar1中存放实数

amov imag_data, xar2 ;xar2中存放虚数

send:

amov #FIFO, xar0 ;定义FIFO为片选0空间地址为0x02000

bset xf

mov *ar1+, *ar0

bclr xf

mov *ar2+, *ar0

sub #1, ac0

bcc qq, ac0==0

reti

qq: mov #63, ac0

amov real_data, xar1

amov imag_data, xar2

reti

- 相关推荐

- 热点推荐

- 变频

- TMS320VC5509

- HSP50415

-

上变频和下变频的定义 下变频和上变频的区别2023-10-05 8006

-

HSP50415评估板示意图s2023-03-21 519

-

怎么实现基于AD9857的数字上变频电路设计?2021-05-31 1680

-

数字上变频器芯片Tames复调制2021-05-11 881

-

可编程调制器HSP50415电子资料2021-04-08 1119

-

基于FPGA的高效灵活数字上变频实现设计2020-01-29 4878

-

数字上变频器IC调制复杂调制2019-07-22 1366

-

可编程数字上变频器HSP50415的结构、功能和特点2018-08-29 5954

-

基于FPGA的DUC数字上变频设计2016-04-27 1265

-

通信系统中数字上变频技术的研究与设计2012-08-29 1801

-

基于数字上变频器的中频调制器2011-07-11 4466

-

发射机中频数字化的设计与实现2011-02-27 868

-

基于QDUC的雷达上变频电路的设计2010-12-29 1224

全部0条评论

快来发表一下你的评论吧 !