ICer这5种bug你是不是经常遇到?

电子说

1.4w人已加入

描述

在你们的工作中都遇到过哪些bug呢?下面这些你见过没?

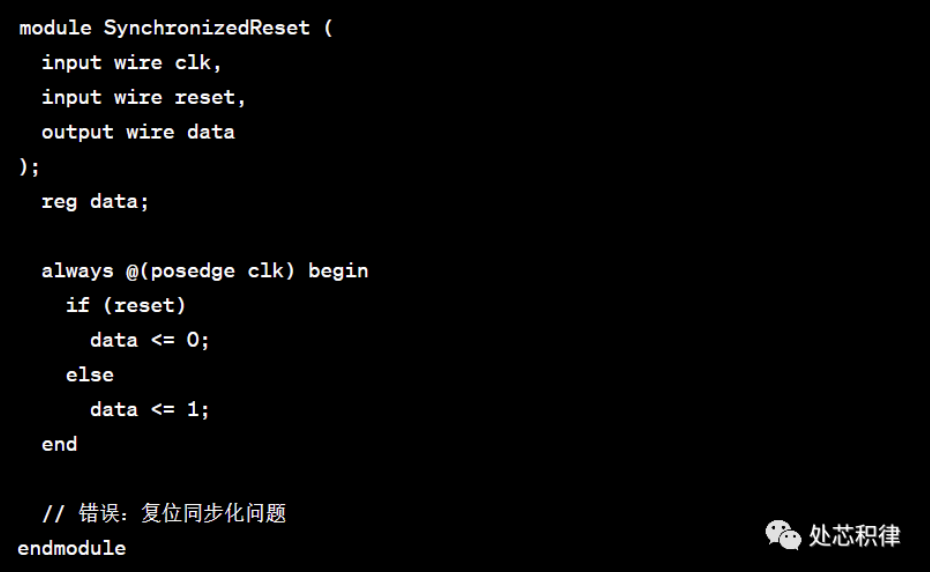

1. 复位同步化问题

错误的地方:在时钟上升沿处处理复位信号,但未同步复位信号到时钟域,可能导致复位信号的抖动或同步问题。

2.未初始化的寄存器的问题

错误的地方:未对寄存器 reg1 和 reg2 进行初始化,初始值未定义,可能导致未知的行为和仿真结果。

3. 异步信号同步问题

错误的地方:直接将异步信号 async_signal 用于时钟边沿触发的逻辑中,没有进行同步处理,可能导致元数据冲突和时序问题。

4. 不完整的数据路径

错误的地方:在数据路径中,信号 d 通过与门的连接计算得出,但未将 d 直接连接到输出 c。这可能导致输出 c 未能正确反映数据路径的结果,导致逻辑错误或意外行为。

5. 不正确的信号赋值顺序

错误的地方:在信号赋值时,赋值顺序不正确,导致信号之间的依赖关系混乱,可能导致逻辑错误或不一致的行为。

6.逻辑错误

错误的地方:在逻辑运算中,使用了错误的操作符,导致逻辑功能与预期不符。

7. 时序插入问题

错误的地方:在时序逻辑中,对计数器值进行判断时,条件错误地设置为 counter == 4,而实际上应该是 counter == 3。这会导致时序行为出现问题。

8.非活跃信号处理

错误的地方:在处理信号时,缺少 else 分支,未能正确处理信号非活跃的情况,可能导致逻辑错误。

9. 组合逻辑环路

错误的地方:在连续赋值语句中,创建了组合逻辑环路,其中信号 b 依赖于信号 c,而信号 c 又依赖于信号 b,这会导致综合和仿真时的不确定行为。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

谷景告诉你屏蔽绕线功率电感是不是感量越大性能越好2024-06-10 1381

-

怎么看网线是不是千兆网线2023-06-26 8301

-

这17种焊接陷阱,你遇到过多少?2022-04-14 1653

-

芯片是不是就是CPU2021-12-16 21515

-

芯片驱动内阻是不是越小越好,上升沿的斜率是不是越陡越好?2021-03-31 5697

-

#1024程序员节#话题讨论:不会填坑的程序员不是一个好程序员!2020-10-23 3704

-

如何判断步进电机是不是失步2020-09-25 8299

-

EDMA3CC_COMPL_HANDLER_RETRY_COUNT的值是不是bug2018-06-21 2254

-

遇到问题,你会去找VS你会去问。?2018-05-12 1877

-

这个是不是事件结构的bug,为什么这个控件没有被清空呢?2016-10-09 2949

-

完善用户资料任务是不是有BUG?2013-10-06 4736

-

labview大神心得-你是不是经常徘徊不定?2011-11-24 31715

全部0条评论

快来发表一下你的评论吧 !