LLC峰值电流控制PWM发波的设计实现

控制/MCU

描述

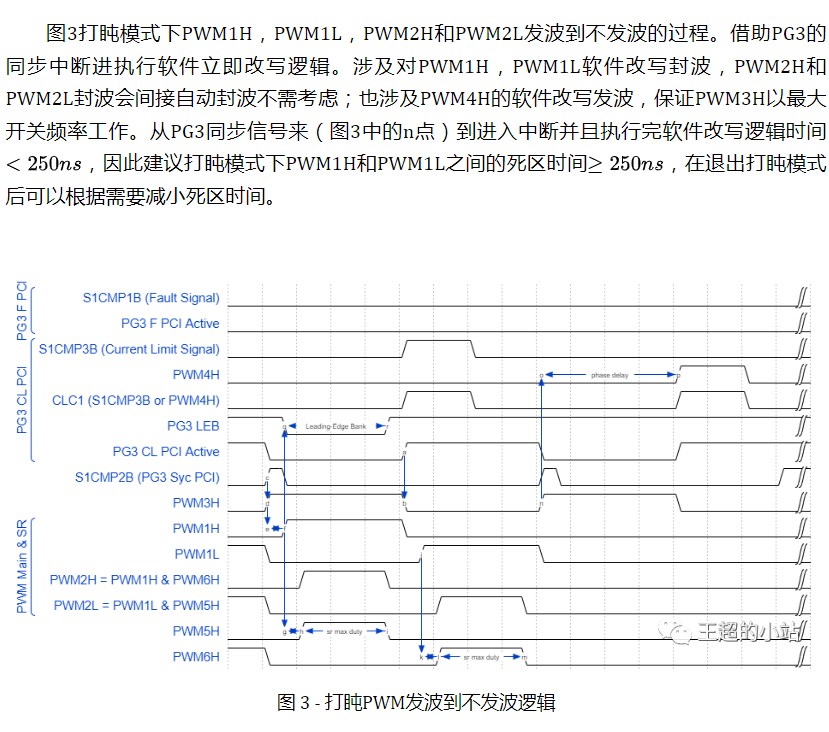

本文介绍基于 dsPIC33CH512MP508 实现的LLC峰值电流控制PWM发波逻辑,该发波逻辑充分利用了 dsPIC33C 系列MCU强大的PWM外设,用到了诸如PCI同步功能,PCI故障、限流对输出的硬件改写,借助软件改写实现Burst模式下发波与否,以及不同组PWM之间的组合逻辑。

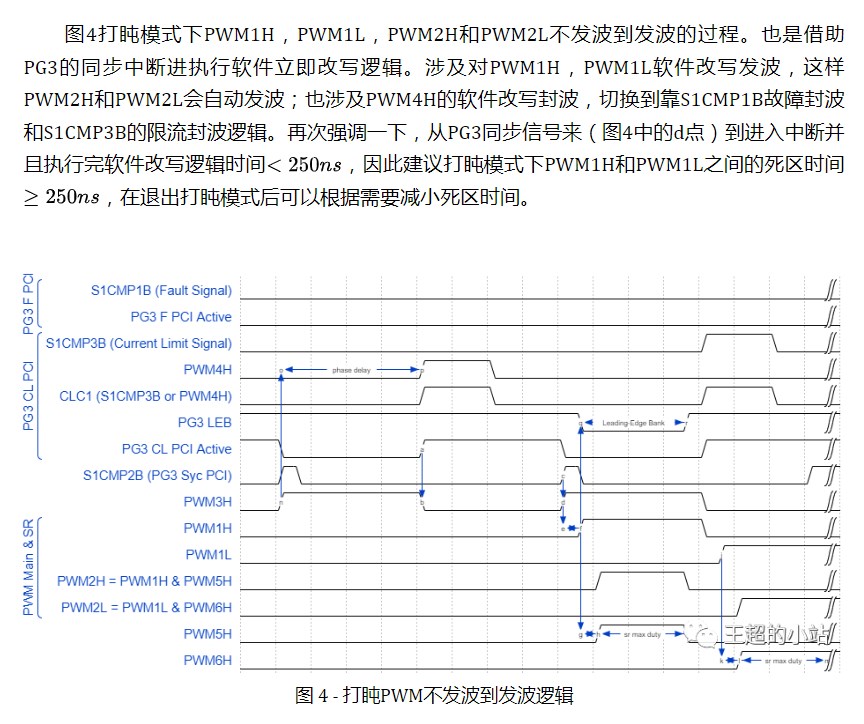

1. PWM发波逻辑说明

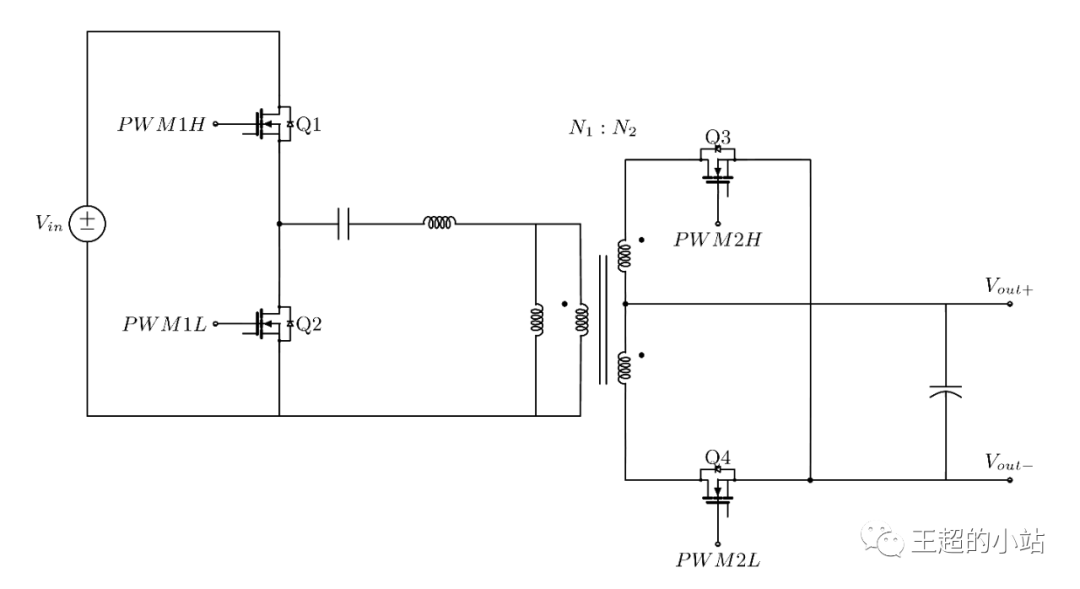

带同步整流的半桥LLC拓扑结构示意如下,需要2对PWM波。这里基于dsPIC33CH512MP508的从核实现,其中PWM1H和PWM1L为主管PWM驱动,PWM2H和PWM2L为同步管PWM驱动。

图 1 - 半桥LLC拓扑示意

带同步整流的半桥LLC峰值电流控制的发波逻辑具体说明如下。

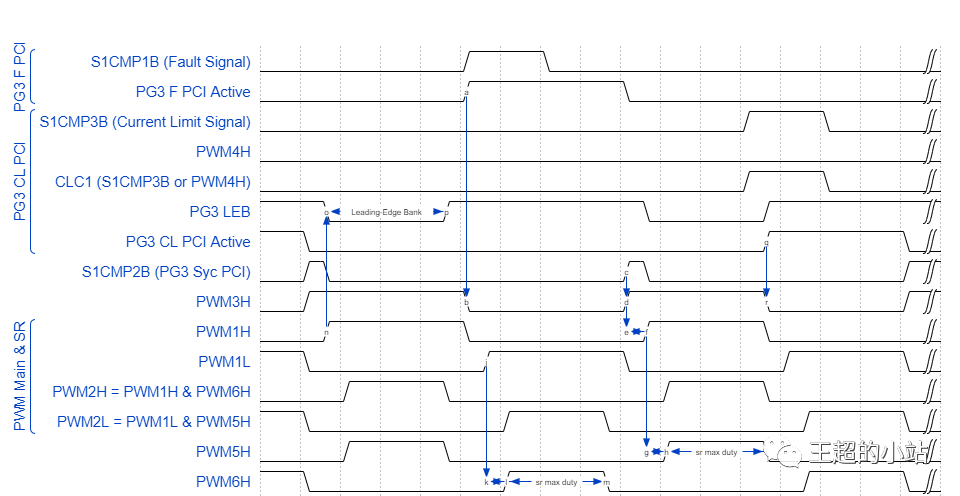

- PWM3H为源头信号,初始周期为一很低频的值,通过S1CMP1B故障封波以及CLC1(S1CMP3B or PWM4H)限流封波来改变PWM3H的高电平持续时间,而PWM3H周期依赖于S1CMP2B的同步实现。

- PWM1H和PWM1L为半桥LLC的主管驱动,PG3与PWM3H上升沿同步,在PWM3H下降沿硬件限流封波改写直到下一个PWM3H上升沿,同时PG1因互补模式,输出需要有死区(图2中的e<->f)控制。

- PWM5H与PWM1H的上升沿同步,PWM5H用于限制LLC同步整流管的导通时间(图2中的h<->i),最终LLC同步整流管 PWM2H = PWM1H & PWM5H,而同步管PWM2H相对于PWM1H的相位delay可以通过PG5PHASE控制(图2中的g<->h)。

- PWM6H与PWM1L的上升沿同步,PWM6H用于限制LLC同步整流管的导通时间(图2中的l<->m),最终LLC同步整流管 PWM2L = PWM1L & PWM6H,而同步管PWM2L相对于PWM1L的相位delay可以通过PG6PHASE控制(图2中的k<->i)。

- PWM4H用于打盹模式不发波工况下维持PWM3H以最高开关频率工作,主要靠PG4PHASE实现(图3中的o<->p)。

正常工作时的PWM逻辑波形如图2,主要靠标准的电流峰值限流信号(S1CMP3B)实现峰值电流控制,特殊的为了保护机器当电流瞬时值过大,而经硬件处理获得的电流峰值信号并未触发S1CMP3B翻转,此时则靠电流故障信号(S1CMP1B)来实现峰值电流控制。

图 2 - 正常工作时PWM波形

2.3 发波逻辑验证

主核的PWM1H(RB14)和PWM1L(RB15)在50kHz到350kHz来回滑动,为50%占空比互补模式无死区,以模拟外部输入信号。同时实验前需按如下规则接线,搭建好的平台如图6所示。注意:S1CMP3B与S1CMP1B连接的为同一个信号PWM1L,实验室也可以一个连接为PWM1L,一个连接为GND,以分别验证PG3的PCI限流和故障。

- 将PWM1H(RB14)与S1CMP2B(RD10)相连,PG3的PCI同步信号为PWM1H的上升沿。

- 将PWM1L(RB15)与S1CMP3B(RC3)相连,PWM1L的上升沿代表电流过流。

- 将PWM1L(RB15)与S1CMP1B(RC6)相连,PWM1L的上升沿代表电流故障。

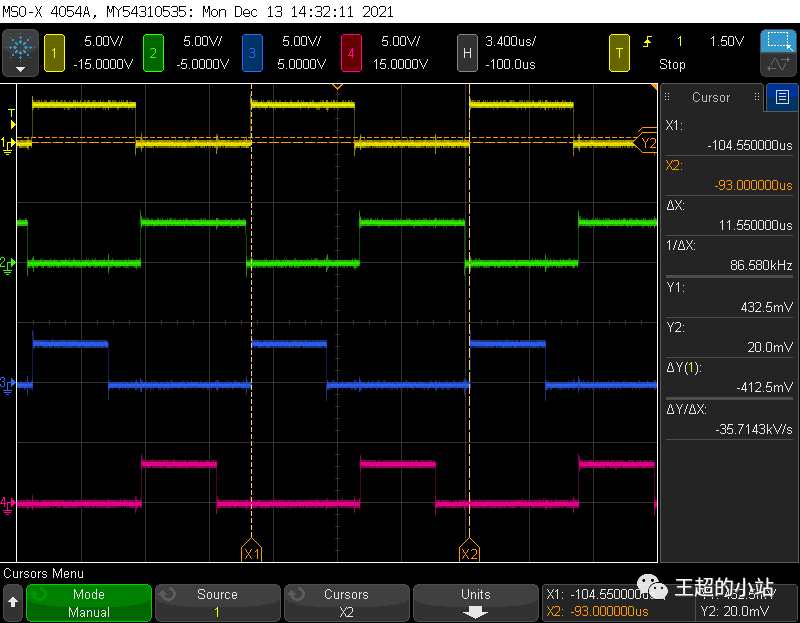

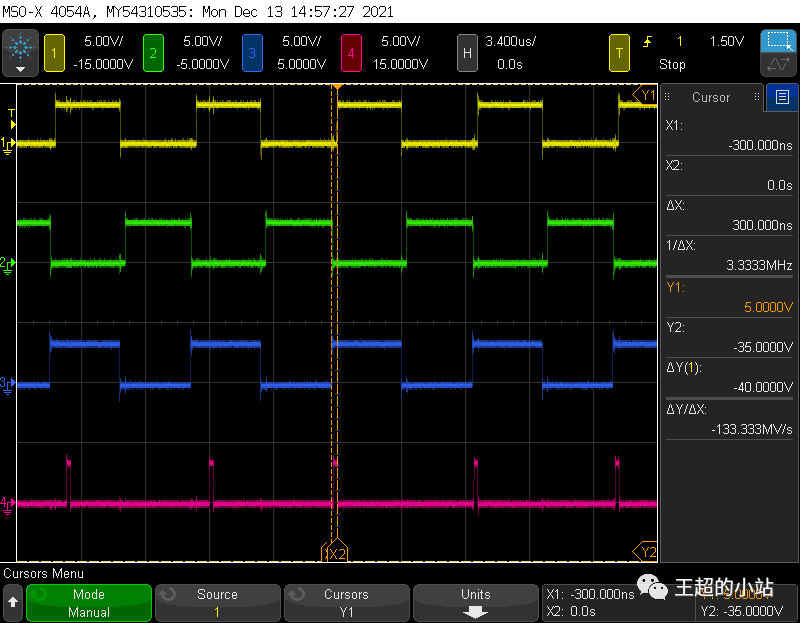

1)稳态时,同步管PWM2H和PWM2L被限制最大占空比工况波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

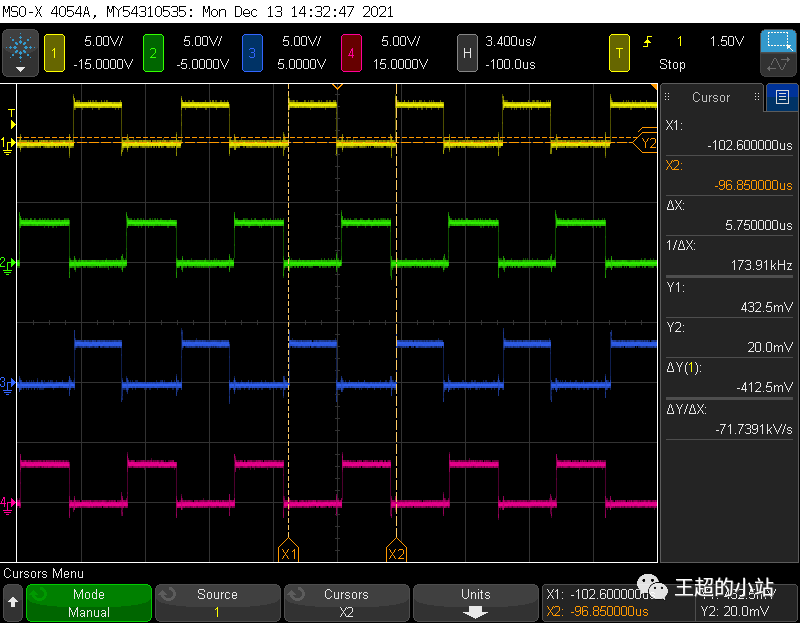

2)稳态时,同步管PWM2H和PWM2L未被限制最大占空比工况波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

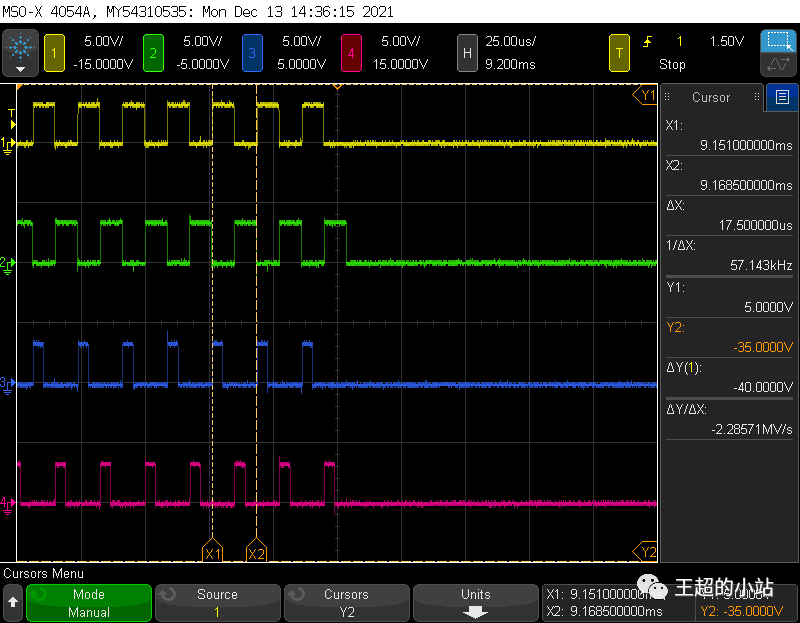

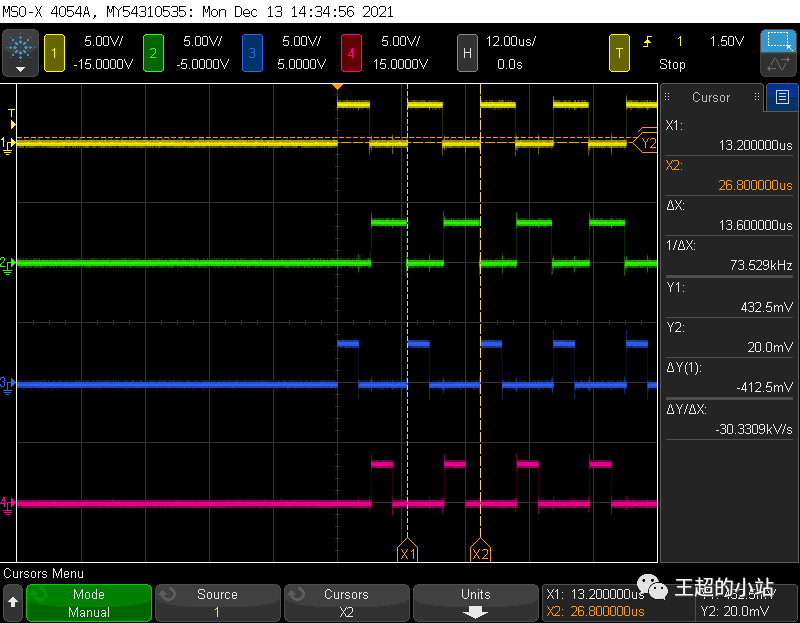

3)发波到禁止发波过程波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

4)发波禁止到发波过程波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

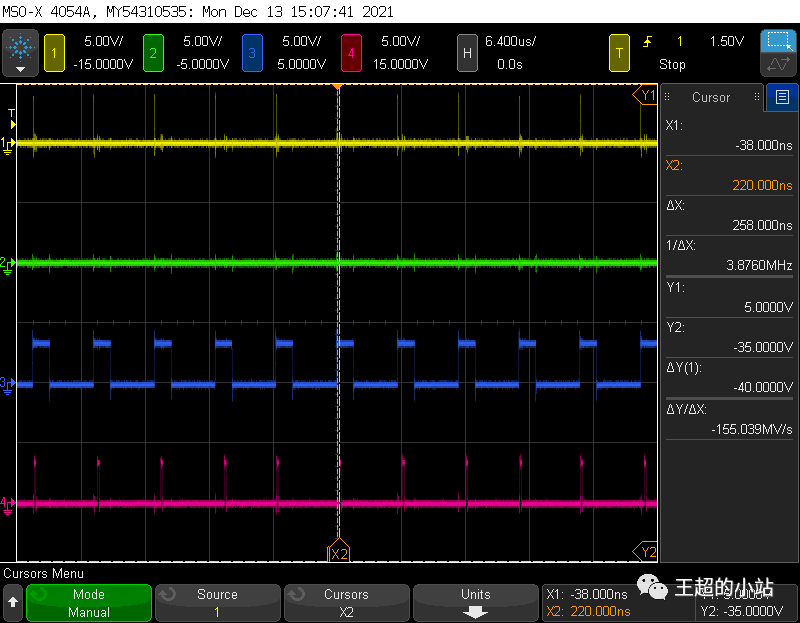

5)功率管发波期间PWM3H和PG3同步中断IO(RD0)翻转波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM3H, CH4: RD0

6)功率管非发波期间PWM3H和PG3同步中断IO(RD0)翻转波形如下:

CH1: PWM1H, CH2: PWM1L, CH3: PWM3H, CH4: RD0

注意:以上波形均未考虑同步管相对于主管的相位延迟,大家可以通过PG5PHASE和PG6PHASE自行设置。

-

平均电流控制和峰值电流控制的区别2023-12-14 8125

-

基于峰值电流控制的变换器建模2023-10-16 1867

-

基于dsPIC33CK256MP508实现的三相交错LLC PWM发波逻辑2023-07-22 8800

-

Buck基于变占空比的PWM调制概览2023-03-23 1800

-

详解LLC电路的PWM工作状态2023-03-21 7962

-

改进峰值电流模式控制2022-11-07 734

-

一种全桥移相控制PWM发波方案2022-09-30 15334

-

ARM11嵌入式系统实时网络通信和PWM波输出控制的实现2021-07-30 1180

-

如何在数字控制系统中实现LLC变换器的电流模式控制?2021-03-11 2969

-

如何在数字控制系统中实现 LLC 的电流型控制?2020-07-09 6923

-

改进峰值电流模式控制的方法2018-09-20 2397

-

峰值电流模控制中的斜坡补偿技术2011-09-19 2235

-

载波反相三角波比较电流跟踪PWM控制法2011-08-22 1637

-

峰值电流模式控制PWM2011-08-09 5932

全部0条评论

快来发表一下你的评论吧 !