一文了解NAND闪存技术的发展演变

描述

对NAND存储器的需求不断增长

随着游戏产业和数据中心的蓬勃发展,全球 NAND 市场正呈扩张之势。而由于新冠疫情的爆发,人们更多选择远程办公和在线课程,对数据中心和云服务器的需求随之增长,市场对 NAND 存储器的需求也大幅增加。从移动或便携式固态硬盘到数据中心,从企业固态硬盘再到汽车配件, NAND 闪存的应用领域和使用场景愈发多样化,各种要求也随之出现,常见的譬如更高的读写速度、最大化的存储容量、更低的功耗和更低的成本等等。为了满足这些要求,数据的存储方式和堆叠方法也在不停发展演变。

NAND闪存的数据存储办法

NAND 闪存是一种通过在氮化硅的内部补集点捕获电子或空穴来存储信息的设备。在这种设备中,工作区和栅极间会留有通道供电流通过硅晶片表面,而根据浮置栅极中存储的电荷类型,便可进行存储编程 (“1”) 和擦除 (“0”) 信息的操作。同时,在一个单元内存储 1 个比特的操作被称为单层单元 (SLC)。氮化硅内部捕获的电子数量与单元晶体管的阈值电压成正比,因此,当俘获大量电子时,即实现了高阈值电压;捕获少量电子会造成低阈值电压。

通过将捕获的电子数量分成三份,并将每份的中间电压施加到单元栅极上,可以检查电流的流通状态,从而确定所捕获的电子数量。在这种情况下,存在四种状态,其中包括擦除状态:这就是 2 比特多层单元 (2 bit-MLC)。2 比特多层单元的这四种状态可以描述为“11”、“10”、“01”和“00”,每个单元可以存储 2 个比特的信息。从定义而言,多层单元指的是一种状态,在这种状态下,一个单元具有多层的 2 个比特或更多比特;然而在本文中,多层单元是相对于单层单元(SLC,Single Level Cell)而言的。方便起见,本文将存储 2 个比特信息的多层单元(MLC,Multi Level Cell)称为 2 比特多层单元。

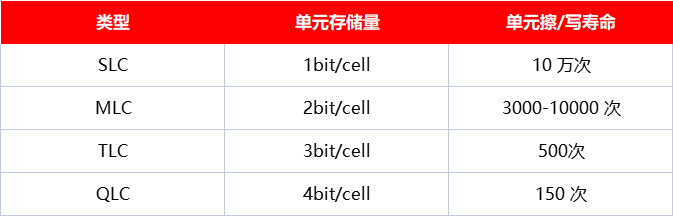

在相同的方法下,若产生八单元状态并存储 3 个比特的信息时,此类状态则被称为三层单元 (TLC,Triple Level Cell);同样,当产生十六单元状态并存储 4 个比特的信息时,则称为四层单元 (QLC, Quadruple Level Cell)。单元状态越密集,一个单元内便可储存更多信息。举例来说,与单层单元(SLC) NAND 闪存相比,四层单元(QLC) NAND 闪存能够以 67.5% 的芯片尺寸存储相同数量的信息;但若想进行更多运行和读取的操作,就要增大单元状态的密度。相应地,由于单元状态之间的空间狭窄,更大的密度会使性能降级并出现读取错误的可能性,从而导致设备寿命缩短。因此,重要的是,首先要根据NAND闪存的应用领域决定是否优先考虑信息量,性能和寿命,然后选择适当的编程方法。

NAND闪存行业的发展趋势

当前,NAND 闪存正在从 2D 发展到 3D 和 4D。对于 2D-NAND,如果在同一区域实现更多的单元数量,形成更小的工作区和栅级,便能增大存储容量。直至 2010 年初,2D-NAND 中的扩展一直是这项技术的主要焦点所在;然而,由于精细图案结构的限制,且储存数据会随时间推移而丢失导致使用寿命缩短,该技术已无法再实现扩展。因此,3D-NAND逐渐取而代之,成为业界关注焦点,现在所有 NAND 制造商都在开发和制造 3D-NAND 产品。

在 3D-NAND 的结构中,存储容量会随着三维叠层中堆叠层数的增加而变大。3D-NAND 使用了堆叠多层氮氧化物的方法,形成一个被称为“塞子”的垂直深孔,在其中形成一个由氧化物-氮化物-氧化物制成的存储设备。通过这种方法,仅需少量工艺即可同时形成大量单元。在 3D-NAND 中,电流通过位于圆柱单元中心的多晶硅通道,便能根据存储在氮化硅中的电荷类型实现存储编程和擦除信息。虽然2D-NAND 技术发展的目标是实现形成较小的单元, 3D-NAND 的核心技术却是实现更多层数的三维堆叠。

为在 3D-NAND 的基础上进一步增大存储容量,4D-NAND技术也随之而来。经过几代技术的发展,当前的半导体行业已实现了用更多层数存储更多信息,目前最高层为238层,存储企业也正在研发更多层的产品。

审核编辑:刘清

-

NAND闪存是什么意思2024-08-10 12919

-

一文解析NAND的闪存接口ONFI2024-04-03 11307

-

芯科普 | 一文了解 NAND 闪存技术的发展演变2023-07-24 1803

-

典型3D NAND闪存结构技术分析2023-06-27 3433

-

从NOR到NAND闪存,从Intel到英伟达,闪存的发展史由谁来续写?电子学习 2023-02-08

-

LTE发展演进及关键技术2021-04-07 967

-

简述NAND闪存的写入限制与发展2021-04-01 3769

-

NAND闪存芯片有哪些类型2020-09-18 8549

-

解析NAND闪存和NOR闪存2020-07-30 16707

-

NAND闪存的自适应闪存映射层设计2010-05-20 1233

-

计算机软件的发展演变简介2010-04-13 4576

-

NOR闪存/NAND闪存是什么意思2010-03-24 8949

-

CPU芯片封装技术的发展演变2006-04-16 1792

全部0条评论

快来发表一下你的评论吧 !