ttl电路和cmos电路的区别 TTL逻辑门的电路图设计

描述

ttl电路和cmos电路的区别

TTL (Transistor-Transistor Logic) 和 CMOS (Complementary Metal-Oxide Semiconductor) 是两种常见的数字电路家族,它们在电路结构和性能上有一些区别。

1. 电路结构:

- TTL:TTL电路使用双晶体管(BJT)作为主要的开关元件。TTL逻辑家族包括TTL、LS-TTL、HCT-TTL等各种变种。

- CMOS:CMOS电路使用场效应晶体管(FET)作为主要的开关元件。CMOS逻辑家族包括CMOS、HC-CMOS、AC-CMOS等各种变种。

2. 功耗:

- TTL:TTL电路在开关过程中会有短暂的能量消耗,同时也导致一些功率损耗。

- CMOS:CMOS电路几乎不消耗能量,只有在切换时瞬时消耗一些能量,因此功耗较低。

3. 噪声容忍度:

- TTL:TTL电路对于噪声比较敏感,较高的噪声容忍度,使其在工业和高速应用中更受欢迎。

- CMOS:CMOS电路具有较高的噪声容忍度,适合在低功耗应用和噪声环境中使用。

4. 工作电压:

- TTL:TTL电路通常使用较高的工作电压,典型的5伏特(V)供电。

- CMOS:CMOS电路通常使用较低的工作电压,典型的3.3伏特(V)或以下供电。

5. 速度:

- TTL:TTL电路具有较快的切换速度和短的延迟时间,适用于高速应用。

- CMOS:CMOS电路的切换速度相对较慢,但在低功耗和高集成度应用中有优势。

总体而言,TTL电路具有快速响应、耐噪声的特点,适用于需要高速和噪声容忍度的应用。而CMOS电路功耗低、噪声容忍度高,适用于低功耗和高集成度的应用。选择使用哪种类型的电路,需要根据具体应用的需求来决定。

TTL和CMOS输出的电平判断

TTL和CMOS输出的电平判断是不同的。

在TTL电路中,逻辑高电平(“1”)对应于较高的电压(一般为2.4V至5V),逻辑低电平(“0”)对应于较低的电压(一般为0V至0.4V)。当输入信号超过TTL门电平的一半时,门电路将被视为为逻辑高电平。例如,对于标准TTL(S-TTL)电路,当输入电压超过0.8V时,门电路被视为逻辑高。

而在CMOS电路中,逻辑高电平(“1”)对应于较高的电压(一般为3V至5V),逻辑低电平(“0”)对应于较低的电压(一般为0V至0.5V)。当输入信号超过CMOS门电平的一半时,门电路将被视为逻辑高电平。例如,对于标准CMOS电路,当输入电压超过1.5V时,门电路被视为逻辑高。

需要注意的是,具体的电平判断取决于具体的电路家族和制造商,不同的规格和芯片可能会有微小差异。因此,在使用任何具体的TTL或CMOS芯片时,应查阅其数据手册以获取准确的输入/输出电平规格。

我们使用的大多数系统都依赖于 3.3V 或 5V TTL 电平。TTL 是晶体管-晶体管逻辑的缩写。由双极晶体管构建的电路来实现切换和保持逻辑状态。

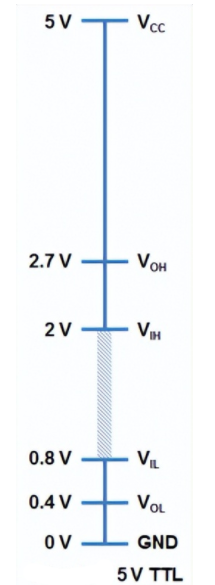

对于任何逻辑系列,阈值电压电平是必须要了解的一个点。以下是标准 5V TTL 电平的示例:

V OH ——TTL 设备将为高信号提供的最小输出电压电平。

V IH -- 被视为高电平的最小输入电压电平。

V OL -- 设备将为低信号提供的最大输出电压电平。

V IL——仍被视为低电平的最大输入电压电平。

从上图中可以看到最小输出高电压(VOH)为2.7V。这意味驱动高电平设备的输出电压至少为2.7V。最小输入高电压 (V IH ) 为 2 V,意味着基本上2V以上的电压都将作为逻辑1(高)读入TTL设备。

应该还可以注意到一个设备的输出与另一个设备的输入之间存在0.7V的缓冲,被称为噪声容限。

同样,最大输出低电压 (V OL ) 为 0.4 V,发出逻辑0的设备将低于0.4V。最大输入低电压 (V IL ) 为 0.8 V,意味着低于0.8V的输入信号在读入设备都是逻辑0。

如果电压介于 0.8 V 和 2 V 之间会怎样?这个电压范围是不确定的,会导致无效状态,通常称为浮动。如果在设备上的输出引脚在此范围内“浮动”,则无法确定信号会产生什么结果,可能会在高电平和低电平之间任意反弹。

TTL电路如何工作?

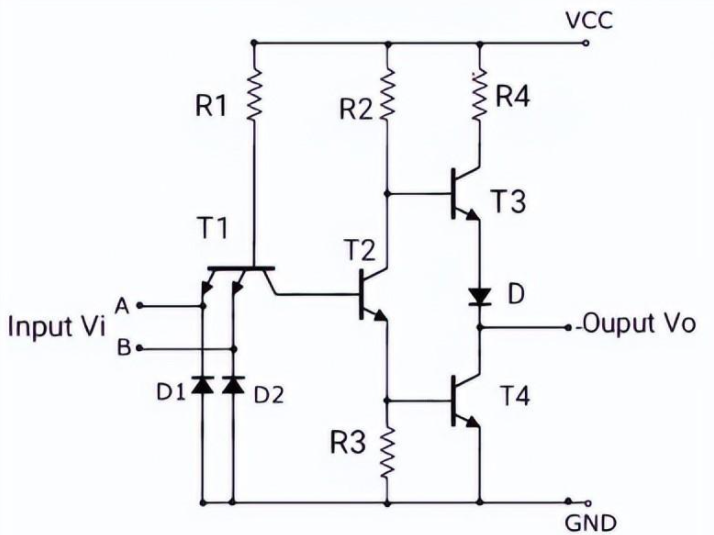

下面为标准TTL逻辑门的电路图,正 NAND 门功能,如下图所示。这种标准的TTL逻辑电路在某些情况下与二极管-晶体管逻辑(DTL)电路有关。

具有 2 输入与非门的 TTL 电路

从上图可以看出,T1是输入三极管,在开关时间上有优势。晶体管 T2 是分相器,晶体管 T3 和 T4 提供图腾柱输出。该 TTL 电路具有极低的输入阻抗、高扇出和更好的抗噪性,并且能够进行高电容驱动。

当输入 A 和 B 为高电平时,晶体管 T2 和 T3 导通并充当共发射极放大器。晶体管 T4 和发射极处的二极管正向偏置,并且流过的电流量可以忽略不计。输出为低电平,代表逻辑 0。

当两个输入均为低电平时,二极管 D1 和 D2 正向偏置。由于 5V 的电源电压 VCC,电流通过 D1 和 D2 以及电阻 R1 流向地面。R1 中的电源电压下降,晶体管 T2 关断,因为它没有足够的电压来导通。因此,晶体管T4也因T2截止而截止。晶体管 T3 导通(高电平)并充当射极跟随器。输出为高电平,代表逻辑 1。

当输入 A 和 B 中的任何一个为低电平时,二极管就会由于低输入而正向偏置。整个操作与上述相同。因此,输出为高电平(逻辑 1)。

编辑:黄飞

-

什么是TTL逻辑电路 TTL与CMOS的区别和优缺点2024-11-18 6398

-

CMOS电路和TTL电路的区别 cmos电路和ttl电路优缺点2024-02-22 14635

-

TTL和CMOS逻辑门电路的几点认识2024-01-28 19503

-

TTL电路和CMOS电路的区别2022-08-31 24718

-

TTL集成电路和CMOS电路有哪些区别2021-11-02 21431

-

TTL门电路的逻辑扩展2018-08-24 2780

-

COMS与TTL电路的区别2018-02-13 22091

-

CMOS与TTL电路的详细对比区别2017-12-19 115437

-

【转】TTL逻辑门与普通逻辑门有什么区别2016-08-23 3664

-

转载-------TTL和CMOS门电路的区别2014-03-23 18133

-

CMOS和TTL电路探讨2012-02-06 2060

-

CMOS电路驱动TTL电路2009-09-24 5976

-

TTL逻辑测试器电路图2009-04-07 866

-

TTL探头电路图2008-12-24 1089

全部0条评论

快来发表一下你的评论吧 !