常见的流控机制之fifo与带外流控

电子说

描述

在数据处理模块中,我们经常会涉及数据流控反压。什么是流控呢?简单来说就是控制数据流停止发送。常见的流控机制分为带内流控和带外流控。带外流控流控比较简单,就是需要一根额外的信号线来表示流控信息,如ready ,1表示可以发送数据,0表示不可以发送数据.如果取名为fc(flow control),则0表示可以发送数据,1表示停止发送数据。带内流控机制中,流控信息是通过数据通路传输的,没有额外的流控信号线。带内流控在接口模块非常常见,例如以太MAC的pause帧和PCIe的信用量机制。流控系列文章分为4篇,今天是第一篇。首先将最简单的流控机制,fifo与带外流控。

1、什么是FIFO

FIFO(first in first out)是一种用寄存器reg或者RAM实现的存储结构,常用于存储数据通道中的数据流,采用先入先出的数据,当下游模块无法及时处理上流模块输出的数据时,此时需要用FIFO暂存数据,防止数据丢失。

2、FIFO的流水反压机制

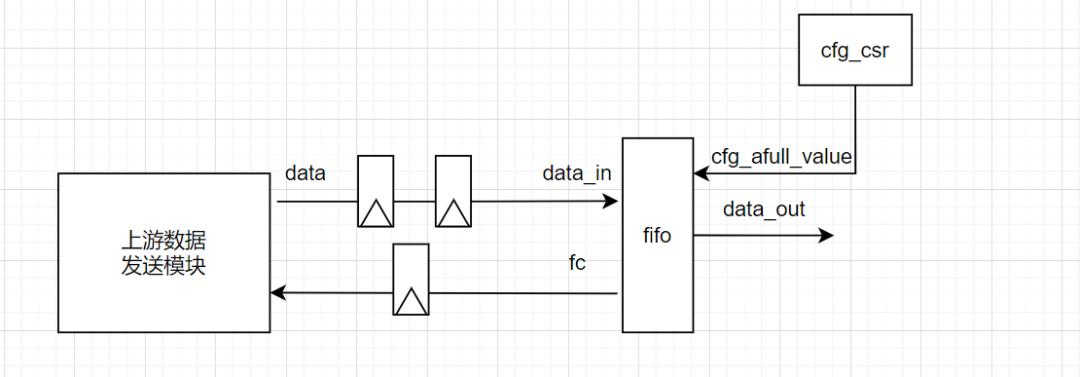

每一个fifo都有一个将满阈值cfg_afull_value(名称随意,看得懂就行),通常由寄存器配置模块cfg_csr提供。当fifo内的数据量达到或超过cfg_afull_value时,将满信号afull从0跳变成1,即fc信号从0跳变1。上游发送模块感知到fc为1时,则停止发送数据,有可能是1~2周期就停止,有可能是一个整包发送完才停止,根据代码实现才能判断。在fc跳变成1后,fifo需要能够缓存路径上的data以及上游发送模块停止发流之前发出的所有data。这就是fifo的流控机制。

图1:fifo流控示意图

3、FIFO深度如何设置

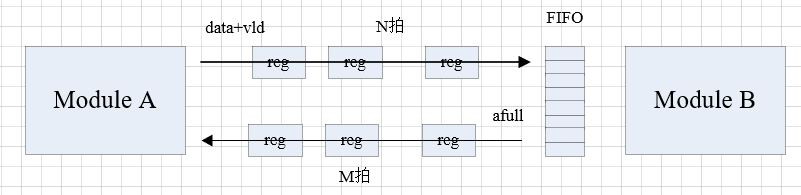

如图2所示,数据data和有效信号vld从模块A产生,经过N拍延时,输入到FIFO,FIFO产生将满信号afull,经过M拍延时反馈到模块A,假设模块A接收到afull=1时,立即停止发送数据。假设FIFO深度为fifo_depth,每拍为一个时钟周期。

图2:fifo深度计算示意图

1为了保证FIFO不发生溢出,请问将满阈值cfg_afull_value至少应该设置成多少?

2为了充分发挥FIFO的性能,FIFO深度depth应该为多少?

FIFO将满阈值如何设置:

当FIFO中的数据为cfg_afull_value时,产生afull=1,

Afull=1经过M拍到达模块A,此时FIFO中应该有(cfg_afull_value+M)个数据。

Afull=1到达模块A时,模块A立即停止发送数据,此时电路中还存在N拍数据将陆续送到FIFO中,所以最后FIFO中应该为(cfg_afull_value+M+N)个数据,

为了保证数据不会溢出,所以应该满足公式fifo_depth>= cfg_afull_value+M+N,因此,将满阈值应该至少为depth_fifo-(M+N)

FIFO深度depth应该为多少?

若fifo_depth过小,afull有效之后,fifo中存储的数据将很快被下游数据读取,而新的数据又无法及时到达FIFO,因此会造成流水气泡,影响电路性能。

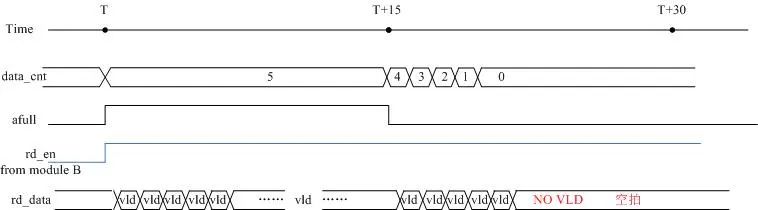

假设M=5 ,N=10,假设fifo_depth=20,则cfg_afull_value=5, 所以在T时刻,fifo中存了5个数据后afull=1会有效,在之后的15个周期内会陆续存入15个数据。假设下游模块B每个周期读取FIFO中的一个数据,因为当FIFO内的数据data_cnt小于5时,afull才会无效(为0),因此在T+15和T+30的时刻内,下游电路B只能读5个数据,因此会造成数据断流,影响电路性能。

图3:流控信号时序图

为保证电路性能,在T+15到T+30这个时间段内应该有15个数据可读,因此cfg_afull_value应该不小于15(M+N)。所以FIFO深度应该不小于2*(M+N)

结束语

其实FIFO的流控方式有个明显的弊端,一旦反压路径M(见图2)过大,会明显浪费资源。

编辑:黄飞

-

什么是带FIFO的OV76702022-01-19 0

-

轿车外流场的数值模拟2009-03-20 0

-

链接后的RX邮箱的FIFO机制是什么意思?2019-08-15 0

-

链接CAN RX邮箱的FIFO机制怎么使用?2019-08-28 0

-

FIFO的具体设计和常见问题2021-01-06 0

-

流控制机制,流控制机制原理是什么?2010-03-20 635

-

Proteus程序之AMP应用UART0_FIFO2016-01-18 455

-

可重构密码流处理器片外流访存系统的设计2017-01-07 576

-

FPGA之FIFO练习3:设计思路2019-11-29 1886

-

FPGA之FIFO的原理概述2019-11-29 4668

-

FIFO队列原理简述2022-07-10 1677

-

同步FIFO之Verilog实现2022-11-01 2015

-

异步FIFO之Verilog代码实现案例2022-11-01 1689

-

过流保护是由什么组成 过流保护与其它保护机制的区别2023-07-12 2747

-

XILINX FPGA IP之FIFO Generator例化仿真2023-09-07 1968

全部0条评论

快来发表一下你的评论吧 !