ttl电路中输入端悬空代表什么 ttl电路正确接线图图解

描述

ttl电路中输入端悬空代表什么

在TTL(Transistor-Transistor Logic,晶体管-晶体管逻辑)电路中,输入端悬空意味着输入端没有连接到高电平(Vcc)或低电平(地/0V)。悬空输入可能导致不确定的电平状态,因此是不推荐的。

在TTL电路中,通常会将输入端连接到确定的电平,以确保电路的可靠性。连接到高电平(Vcc)时,表示为逻辑高(1),连接到低电平(地/0V)时,表示为逻辑低(0)。如果输入端悬空,它可能容易受到电磁干扰或漂移,导致电路的功能不稳定或未定义。

为了防止输入端悬空,可以使用电阻或其他电路来将输入端连接到一个确定的电平。这样可以保证输入信号的稳定性,并确保电路的正确操作。

ttl门电路输入状态怎么判断

在TTL门电路中,输入状态可以通过输入电平来判断。根据TTL的定义,当输入电压低于输入低电平(通常为0.8V)时,被视为逻辑低(0),当输入电压高于输入高电平(通常为2V至5V之间)时,被视为逻辑高(1)。

要判断输入状态,可以使用示波器或逻辑分析仪来测量输入引脚的电压。如果输入电压高于输入高电平,则表明输入状态为逻辑高;如果输入电压低于输入低电平,则表明输入状态为逻辑低。

另外,TTL门电路还具有一些传输特性,比如输入输出转换延迟和噪声容限等,可以对输入状态做出影响。因此,在实际应用中,需要考虑这些因素来确保正确判断输入状态。

ttl电路正确接线图图解

1、标准2输入TTL电路

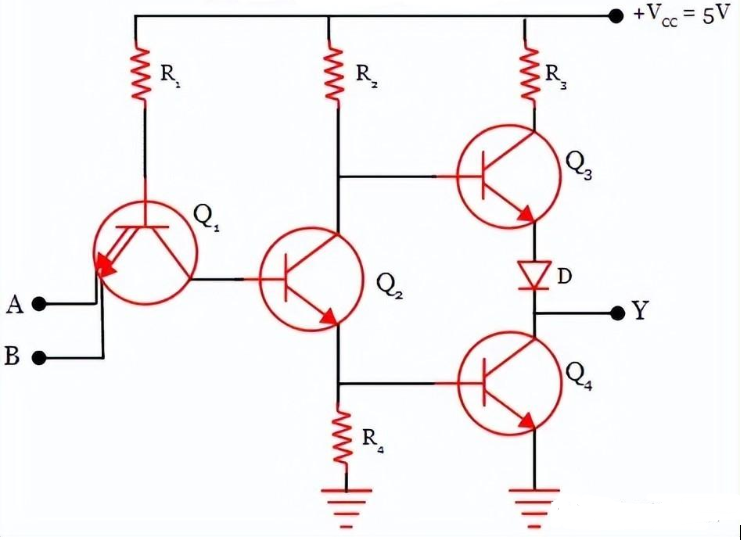

下图为2输入TTL与非门的电路图。它有四个晶体管Q 1、Q 2、Q 3和Q 4。晶体管 Q 1在发射极侧有两个输入端。三极管Q 3和Q 4组成输出端,称为图腾柱输出。

标准2输入TTL电路

2 输入 TTL 与非门的电路可能看起来很复杂。我们可以通过考虑 2 输入 NPN 晶体管的二极管等效来简化其操作,如下图所示。

标准2输入TTL电路

在图中,二极管DA和DB代表晶体管Q 1的2输入发射极结。二极管 DC代表晶体管 Q2的集电极-基极结。

当输入 A 和 B 均为低电平时,两个二极管均正向偏置。因此,由于电源电压 +V CC = 5 V 而产生的电流将通过 R 1 和两个二极管 D A 和 D B 流向地面。

电源电压在电阻 R 1中下降 ,不足以导通晶体管 Q 2。随着 Q 2打开,晶体管 Q 4也将截止。但是晶体管Q 3被拉高。由于 Q 3是射极跟随器,因此端子的输出也将为高电平,即逻辑 1。

当任何一个输入(A 或 B)为低时,具有低输入的二极管将正向偏置。将发生与上述相同的操作,在这种情况下,输出将为高电平。

当输入 A 和 B 均为高电平时,发射极-基极结处的两个二极管都将反向偏置。集电极-基极结处的二极管 D C正向偏置。它将打开晶体管 Q 2。随着Q 2导通,晶体管Q 4也将导通。

输出端的两个晶体管都将导通,因此终端输出将具有低电平,这被视为逻辑 0。

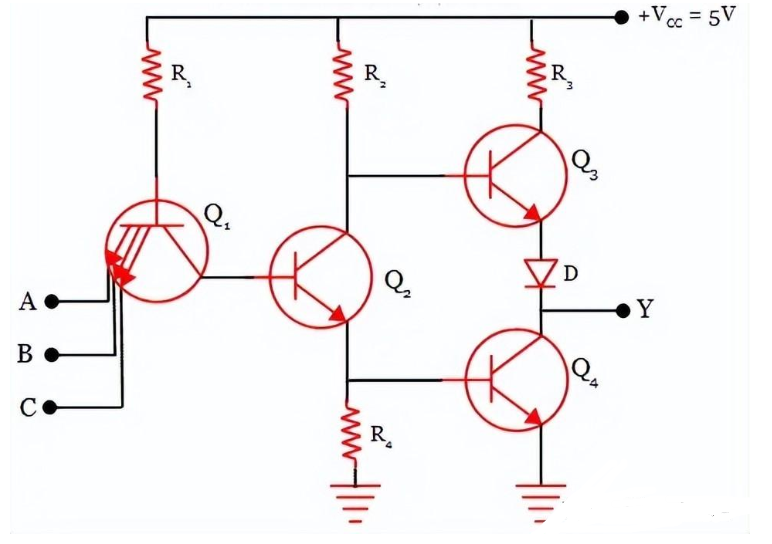

2、标准3输入TTL与非门电路

下图为标准3输入TTL与非门电路。这与我们在2输入TTL与非门电路中差不多,只是这里输入晶体管Q 1具有三个发射极而不是两个。工作原理与 2 输入 TTL 与非门相同。

、标准3输入TTL与非门电路

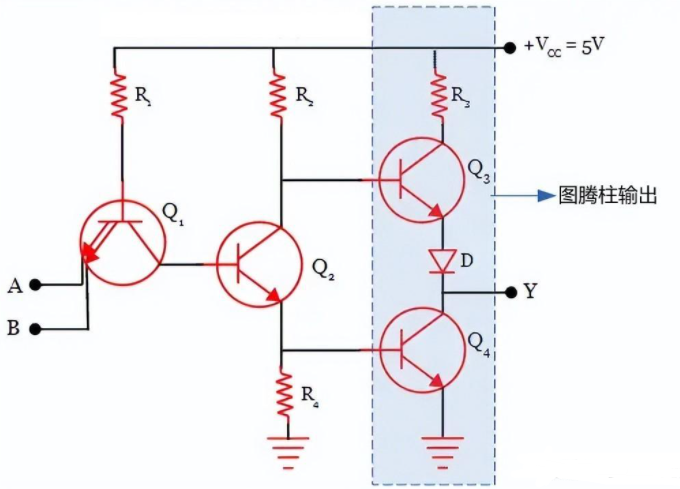

3、TTL图腾柱输出电路

在下图所示的电路中,阴影部分表示图腾柱输出。三极管Q 3、Q 4、二极管D和限流电阻R 3构成TTL的图腾柱输出结构。

标准图腾柱输出,TTL电路具有以下特点和优势:

1、由于延迟时间短,与 DTL 相比,它们的运行速度相当高

2、抗噪性低(0.4V)

3、每个门的平均传播延迟为 10 纳秒 (ns)

4、平均功耗为 10mW

5、它的最大扇出为10,这意味着一个输出可以驱动另外10个TTL输入

6、其他数字电路的接口很容易。

7、与二极管相比,其中应用的多发射极晶体管占用的空间相对较小

8、该系列价格相对便宜,市场上大量供应

9、应用简单易行

10、图腾柱晶体管在二进制 1(高)状态下提供非常低的输出阻抗

11、TTL 设备是兼容的(即一个 TTL 设备的输出可以作为输入提供给另一个 TTL 设备。在这种情况下,第一个设备称为驱动器,而第二个称为负载)

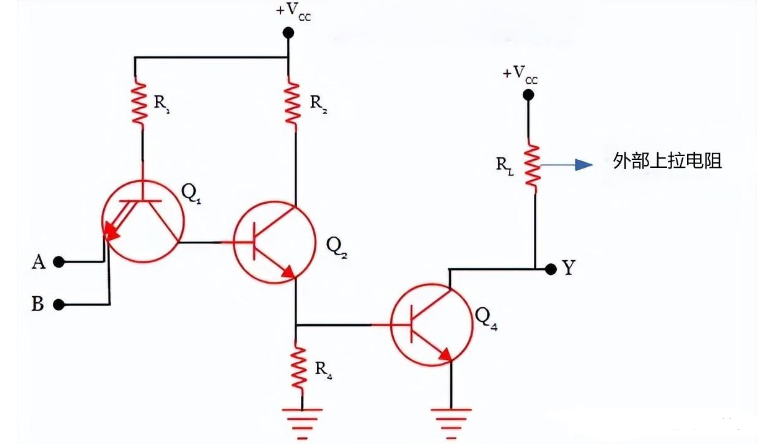

4、TTL集电极开路输出电路

TTL逻辑的集电极开路输出配置如下图所示。在此配置中,取消了晶体管 Q 3和上拉电阻。取而代之的是外部上拉电阻以确保正常运行,如图所示。

TTL集电极开路输出

输出取自 Q 4的集电极开路端子。当晶体管 Q 4关闭时,输出 Y 将为高电平,而当 Q 4导通时,输出将为低电平。

5、TTL三态门输出电路

在这种输出配置下操作晶体管时,可以获得高阻抗。三种输出状态是:高、低和高阻抗。

三态逻辑电路利用图腾柱排列的高速运行,同时允许输出进行线与运算(连接在一起)。Hi-Z 状态是图腾柱排列中的两个晶体管都关闭的状态,因此输出端对地和 V CC为高阻抗。换句话说,输出是一个开路或浮动终端,既不是低电平也不是高电平。实际上,输出端并不是完全开路,而是相对于地和 V CC具有几 MΩ 或更高的高电阻。

TTL三态门输出电路

上图显示了三态逆变器的电路,该电路有两个输入:A 是正常逻辑输入,F 是能够产生 Hi-Z 状态的启用输入。

当 F = 0 时,无论逻辑输入 A 的状态如何,电路都会进入其高阻抗状态。F 处的低电平正向偏置晶体管 Q 1 的发射极-基极结,并使电阻 R1 的电流从晶体管Q分流2使 Q 2关断,从而使晶体管 Q 4关断。E 处的低电平还正向偏置二极管 D 2以从晶体管 Q 3的基极分流电流,因此 Q 3也关闭。由于两个图腾柱晶体管都处于截止状态,因此输出端基本上是开路。

具体的可以看如下真值表:F = 1 时,电路作为正常逆变器运行,因为 F 处的高输入对晶体管 Q 1或二极管 D 2没有影响。在此启用条件下,输出只是逻辑输入的反相。

TTL三态门输出电路真值表

TTL三态门输出电路优点:

高速运转,传播延迟大约为 10 毫秒,与DTL和RTL逻辑器件相比更快。

与 DTL 和 RTL 相比功耗更低。

低成本。

更好的扇出。

噪声可靠运行。

编辑:黄飞

-

如何搭建简单的TTL电路2024-11-18 2054

-

TTL电路输入正确接线图2024-02-18 7154

-

TTL逻辑电路多余的输入端该如何处理?能否悬空?2024-01-16 8135

-

ttl与非门悬空相当于输入什么电平2023-09-17 6128

-

TTL电路多余的输入端的处理方式2023-07-25 6475

-

TTL门电路输入端一般不悬空该怎样接入一个电阻2023-04-28 1838

-

TTL门电路输入端简析2022-01-25 12570

-

关于TTL和CMOS门电路的逻辑输入端输入关系的区别/总结2021-11-30 6435

-

CMOS和TTL集成门电路多余输入端如何处理?2018-08-30 5795

-

CMOS和TTL集成门电路多余输入端的处理方法2015-01-13 49815

-

TTL或非门的逻辑电路及其代表符号2009-04-07 9917

全部0条评论

快来发表一下你的评论吧 !